مقدمة: الحرب على نطاق المليمتر في تصميم DDR5 PCB

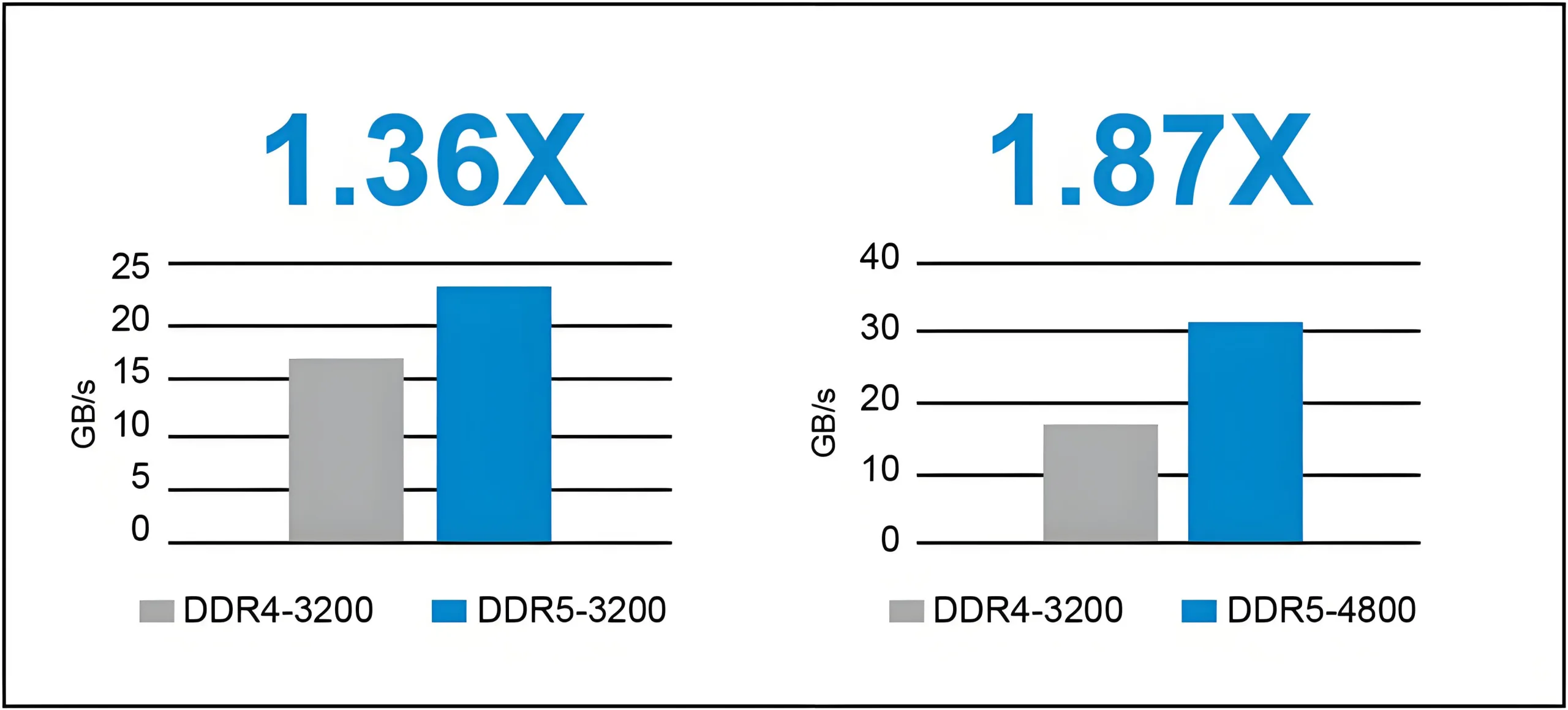

تمثل القفزة من DDR4 إلى DDR5 نقلة نوعية: ترتفع معدلات الإشارة من 3,200 طن متري / ثانية إلى 6,400 MT/s أثناء انخفاض جهد التشغيل إلى 1.1 فولت. هذا التحدي المزدوج يتحول ثنائي الفينيل متعدد الكلور التوجيه من هندسة الاتصال البسيطة إلى حرب دقيقة على نطاق ملليمتر. تكشف بيانات الصناعة ذلك 80% من حالات فشل تصميم DDR5 تنشأ من مشكلات التوجيه, مع 90% يمكن الوقاية منها من خلال محاكاة التخطيط المسبق. تشرح هذه المقالة خمسة مخاطر خطيرة في توجيه DDR5, مدعومة بالبيانات التجريبية ودراسات الحالة, تقديم حلول قابلة للتنفيذ لمحترفي ثنائي الفينيل متعدد الكلور.

1. الخصائص الفيزيائية لذاكرة DDR5: لماذا تفشل طرق تصميم ثنائي الفينيل متعدد الكلور التقليدية

1.1 معدل الإشارة وثورة النطاق الترددي

ل DDR5-6400, يصل تردد الساعة الفعال 3,200 ميغاهيرتز, مع معدلات حافة بأسرع ما يمكن 0.5 ملاحظة (20-80% وقت الارتفاع). هذا يثير:

-

تأثير الجلد المتفاقم: تركز التيارات عالية التردد على أسطح الموصلات, تقليل سمك النحاس الفعال إلى 0.66 ميكرومتر عند 10 GHz.

-

تصاعد فقدان العزل الكهربائي: ركائز FR4 تظهر ظل الخسارة (ص) ل 0.02 في 10 GHz, تسبب >3 توهين إشارة ديسيبل/بوصة.

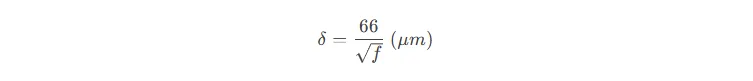

التحقق من صحة الصيغة (عمق الجلد):

في و = 10 جيجا هرتز, δ≈0.66 ميكرومتر,ترك النحاس التقليدي 1oz (35 ميكرومتر) مع <2% استخدام.

2. خمسة حقول ألغام وتدابير مضادة للتوجيه DDR5

2.1 حقل ألغام 1: خطأ في التوقيت - عتبة البقاء ±15ps

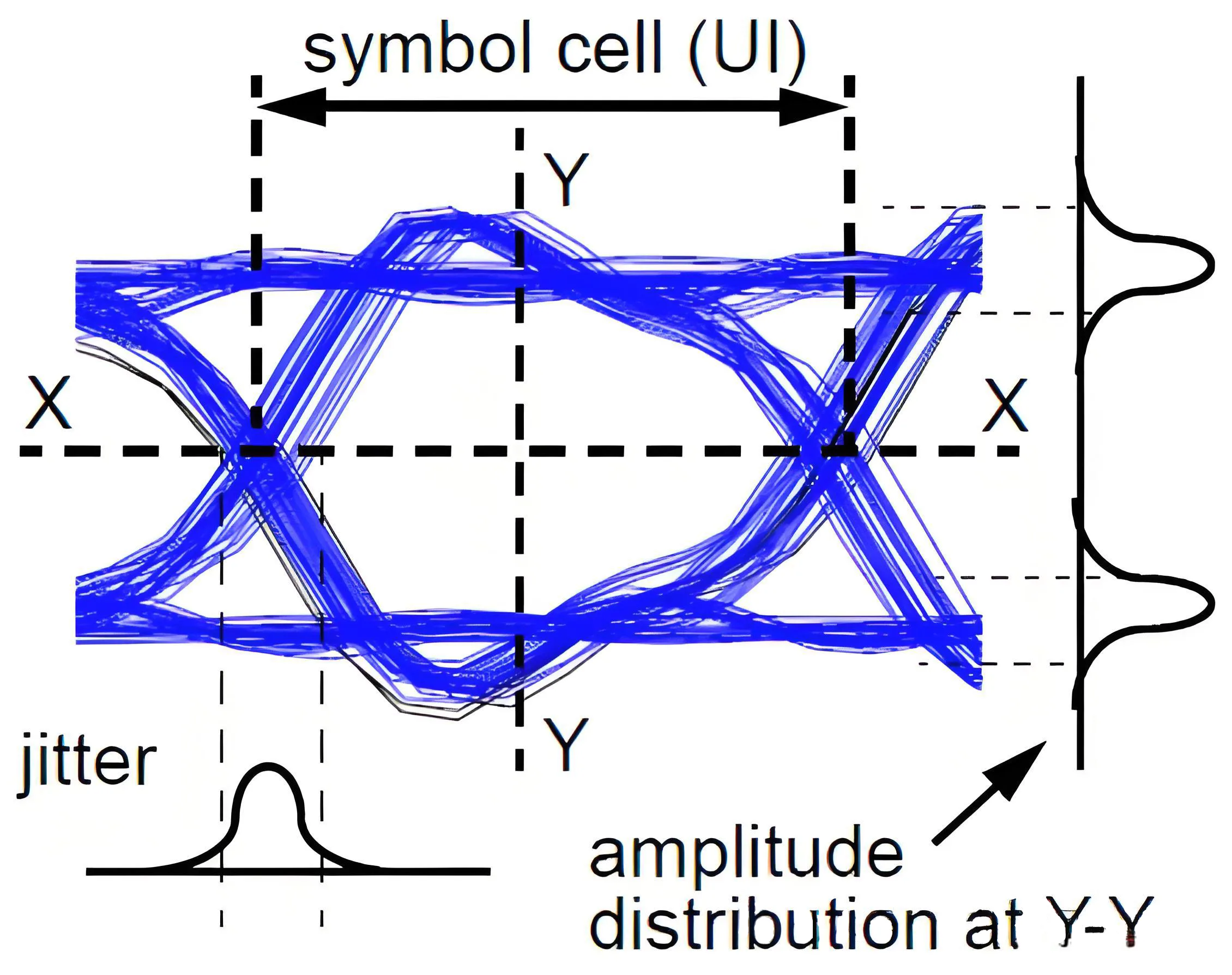

تأثير: يؤدي عدم تطابق الطول بمقدار 5 مل إلى تأخير بمقدار ±12 ثانية, انهيار عرض العين الأفقي بمقدار 30%.

دراسة الحالة: عانى تصميم GPU من تدهور BER 10-12 ل 10-7 بسبب انحراف 8 مل DQ/DQS.

الحلول:

-

3د- تعويض التوجيه: استبدل التعرجات 90 درجة بـ 45 درجة أفعوانية, تقليل السعة الطفيلية بواسطة 30%.

-

معايرة التوقيت الديناميكي: إجراء عمليات محاكاة مونت كارلو (إيقاع سيغريتي) يغطي اختلافات العملية بنسبة ±10%.

صيغة (هامش التوقيت):

تهامِش=تدورة-(تشركة+ترحلة جوية+تغضب)

ل DDR5-6400 (تدورة=0.3125 ), يتم تشغيل تنبيهات النظام عندما تهامِش<50 ملاحظة.

2.2 حقل ألغام 2: انقطاع المعاوقة – تسونامي الإشارة 5Ω

مخاطرة: عبر أسباب عدم تطابق المعاوقة >15 خسارة العودة ديسيبل, انهيار ارتفاع العين العمودي 40%.

بيانات: كل غير محسّن عبر الإضافات 0.2 خسارة الإدراج ديسيبل @ 5 جيجا هرتز.

الحلول:

-

عبر الثورة: تنفيذ فيا الليزر أعمى (≥4 مل) مع تعويض antipad, الحد من اختلاف المعاوقة إلى ± 3Ω.

-

تحسين الوسادة: استخدم منصات بيضاوية الشكل (1.5:1 نسبة العرض إلى الارتفاع) لتقليل التأثيرات السعوية بواسطة 20%.

صيغة (عبر نموذج المعاوقة):

Zvia≈87ϵr⋅ln(5.98ح/(0.8د1 + د2))

أين : سمك عازل, د1: عبر القطر, : قطر الوسادة.

2.3 حقل ألغام 3: تأخير عبر الطبقات – تأثير الفراشة 0.1ps/mm

تأثير نسج الألياف: اختلاف ثابت عازل (Δϵr=0.3) من أسباب دورية الألياف الزجاجية 0.6 انحراف تأخير ps/بوصة.

الحلول:

-

محاذاة المحور Z: قم بتوجيه إشارات مجموعة البايت عند زوايا ±45 درجة لإلغاء تباين العزل الكهربائي.

-

التعويض عبر الطبقات: التحميل المسبق لبيانات Dk/Df للركيزة في أدوات EDA لتصحيح التأخير تلقائيًا.

2.4 حقل ألغام 4: تموج الطاقة – التفاعل النووي المتسلسل بقوة 1 مللي فولت

حساسية: 50يؤدي تموج mV عند مصدر 1.1V إلى زيادة ارتعاش السائق بمقدار 20%.

محاكاة: يجب أن تكون المعاوقة المستهدفة لـ PDN ≥2 mΩ@100 MHz - 5x أكثر صرامة من التصميمات التقليدية.

الحلول:

-

3مصفوفة المكثفات D: نشر 0.1μF (0402) + 10nF (0201) المكثفات بالقرب من المرحلية, تغطية 10 كيلو هرتز – 2 جيجا هرتز.

-

أعمدة نحاسية صغيرة: تضمين أعمدة قطرها 200 ميكرومتر تحت BGAs, قطع حلقة الحث بواسطة 30%.

2.5 حقل ألغام 5: تعطيل مسار العودة – قنبلة EMI غير المرئية

مخاطر EMI: تولد المستويات المرجعية المكسورة ضوضاء في الوضع الشائع, تجاوز حدود EMI بواسطة 10 ديسيبل.

الحلول:

-

خياطة الأرض: مكان فيا الأرض (.10.1Ω) كل 100 mil بين طبقات الإشارة.

-

جسر الطائرة المنقسمة: استخدام المكثفات المدفونة (على سبيل المثال, اف اكس 0402 ب) لاقتران 10nF عبر انقسامات الطاقة.

3. القواعد الذهبية لتصميم DDR5: الصيغ وسلاسل الأدوات

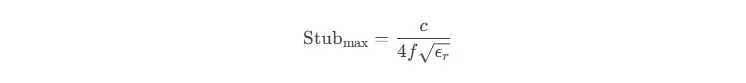

3.1 عبر الحد من كعب الروتين:ل DDR5-6400 (و = 3.2 جيجا هرتز) على FR4: كعب الروتينالأعلى.714.7 ملم.

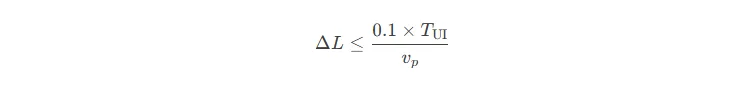

3.2 التسامح الزوجي التفاضلي:

مع تواجهة المستخدم=0.3125 نانو ثانية و ضدص=6 بوصة/: ΔL ≥1.9 مل.

3.3 هدف مقاومة PDN:

لتموج 50 مللي فولت وتيار عابر 10 أمبير: زهدف≥5 مΩ.

4. إعادة هندسة عملية تصميم ثنائي الفينيل متعدد الكلور: من التجربة والخطأ إلى المحاكاة

4.1 التخطيط الطوبولوجي:

-

فيا نموذج في HFSS; تحسين أبعاد antipad.

-

استخراج مقاومة المكدس عبر SIwave; إنشاء مكتبات S-parameter.

4.2 تنفيذ التوجيه:

-

تمكين فحوصات المعاوقة في الوقت الحقيقي في Allegro; انتهاكات العلامة التلقائية.

-

تنفيذ طوبولوجيا الطيران مع انحراف 2 مل داخل المجموعة.

4.3 تصديق:

-

إجراء اختبارات مخطط العين (إعلانات Keysight) مع ارتفاع العين ≥70 مللي فولت.

-

قياس منحنيات TDR; الحد من اختلاف المعاوقة إلى ±5%.

خاتمة: ال “ثلاثة الجسم” قانون تصميم DDR5

تحت غيغاهرتز السرعة, الضوضاء بالميليفولت, وقيود التسامح ميكرون, تصميم DDR5 PCB يدخل أ “ميكانيكا الكم” عصر. يتطلب النصر في حرب سلامة الإشارة تقارب علوم المواد (ركائز منخفضة Dk), العمليات المتقدمة (mSAP), وإتقان المحاكاة.

شعار UGPCB

شعار UGPCB