Disruptive intelligente Fertigung: Wie UGPCB gemeinsam mit der Industrie die globale PCB-Lieferkette neu gestaltet 4.0

Wenn die Rauheit der Kupferfolie das Schicksal von 5-Gbit/s-Signalen bestimmt,

Mit 100-Layer besiegen wir die digitale Flut (Standardmäßige starre Leiterplatte) Präzisionsstapelung.

Die Entwicklung der Leiterplattenherstellung: Von der Handverkabelung bis zur Industrie 4.0 Intelligente Cluster

In der jahrhundertelangen Saga der Elektronik, Die Leiterplattenfertigung hat einen revolutionären Wandel erfahren. Frühe Geräte beruhten auf einer manuellen Verkabelung, mit Fehlerraten von bis zu 18%-22% (IEEE-Daten). Modern automatisiert PCB-Design schneidet dies unten ab 0.0001%. UGPCBs Industrie 4.0 smart factory cluster now redefines “Made in China” with a productivity benchmark of ¥2 million output per worker annually.

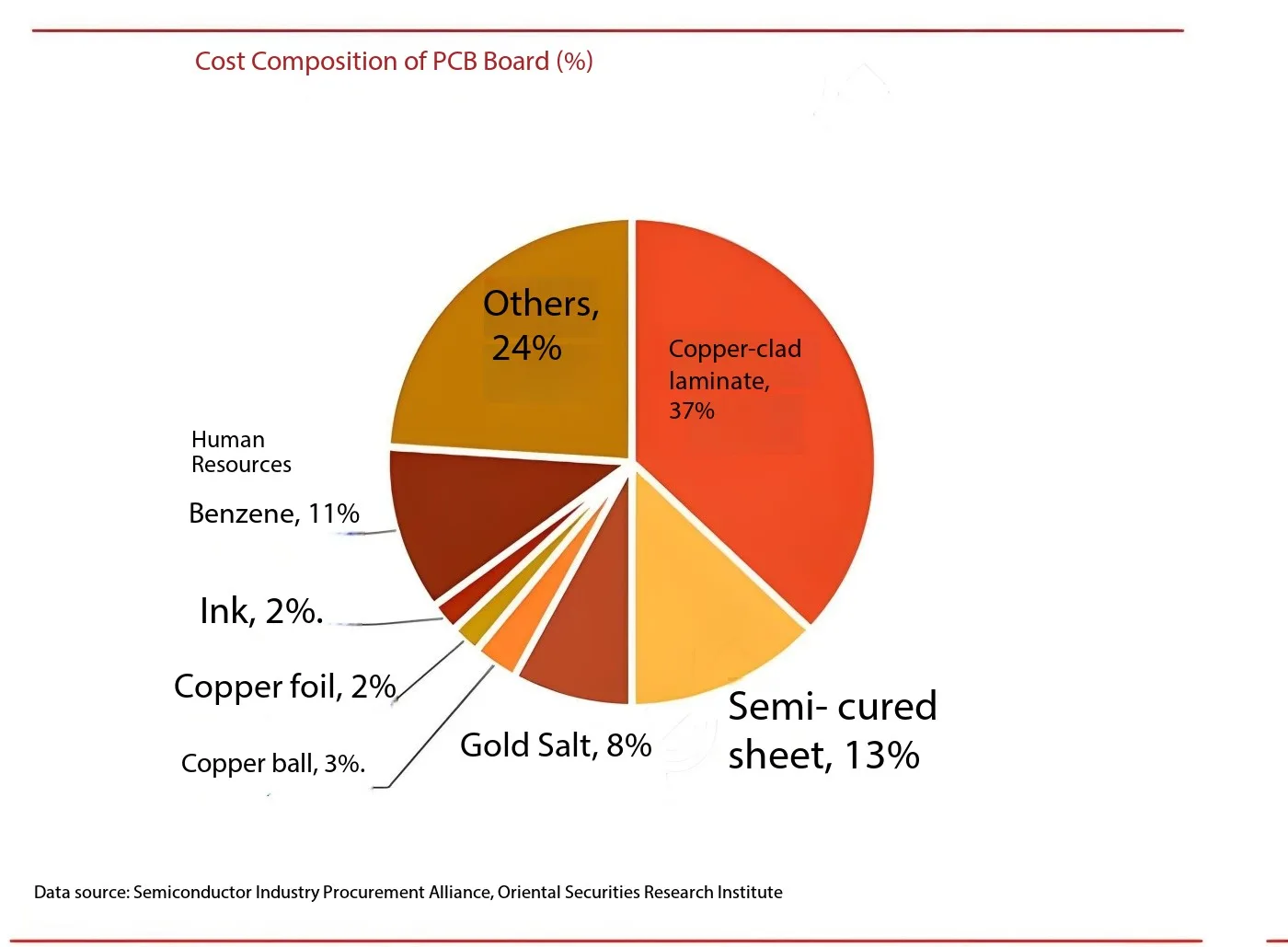

Kostenanatomie: Entschlüsselung der Matrix der High-End-PCB-Produktion

Herausforderungen und Lösungen bei den Rohstoffkosten

• PCB-Kupferfolienformel: Leiterverlust δ = √(2/(omg)). Bei >5GHz Signale, 3µm ultradünne Folie reduziert den Einfügungsverlust um 40%.

• CCL dominiert die Kosten (37%): UGPCB sichert Partnerschaften mit globalem Top 10 Kupferlieferanten (kontrollierend 73% Kapazität), Minderung von Preisvolatilitätsrisiken.

Die 5G-Technologiepyramide: UGPCBs 100-Layer-Aufstieg

Kämpfe auf Mikrometerebene in der Hochgeschwindigkeitssignalübertragung

Für 112-Gbit/s-Übertragung, Rauheit des Leiters (Rz) muss ≤1,5μm sein. Durch die Pulsbeschichtung von UGPCB werden Kupferkörner im Nanomaßstab erzielt, Reduzierung der Einfügungsdämpfung:

IL(dB) = 2.3 × 10⁻⁶ × f⁰˙⁵ × L (f=Frequenz/GHz, L=Spurlänge/Zoll)

Durchbrechen von HDI-Verbindungsgrenzen

| Spezifikation | Industriestandard | UGPCB-Fähigkeit |

|---|---|---|

| Min. Spur/Abstand | 75μm | 40μm |

| Microvia-Durchmesser | 100μm | 50μm |

| Schichtausrichtung | ± 50 μm | ±15μm |

Industrie 4.0 Intelligente Fabrik: Der neuronale Knotenpunkt der zukünftigen Fertigung

Das KI-gestützte Fehlererkennungssystem von UGPCB kombiniert mit automatisierten PCB- und PCBA-Produktionslinien bildet eine Blaupause für eine intelligente Fertigung. Diese Synergie steigert die Produktivität, Renditen, und Kundenzufriedenheit.

Bewerbungen gewinnen: Die Strategie von UGPCB in Billionen-Dollar-Märkten

Erfassung des 5G-Geräteanstiegs

2023 Die weltweiten Auslieferungen von 5G-Telefonen erreichten 725 Millionen Einheiten (IDC), was die Nachfrage nach SLP-Substrat ankurbelt:

Market Value = 725M × 0.38 (adoption) × $12 (price) = $3.3B

Der mSAP-Prozess von UGPCB erreicht 92% Ertrag, übertrifft die 85% Branchenmaßstab.

Leistungselektronik für Fahrzeuge mit neuer Energie

Wärmeleitfähigkeit des Aluminiumsubstrats: λ=α×ρ×Cp

Die Metallkerne von UGPCB liefern 8,0 W/(m · k) Leitfähigkeit, Verbesserung der 800-V-Plattformkühlung durch 60%.

Globaler Beschaffungsplan: 5 Technische Säulen für die Auswahl von UGPCB

-

Geografischer Vorteil: Die Effizienz des Perlflussdeltas übertrifft die EU/USA um 40%.

-

End-to-End-Fähigkeiten: Herstellung von einlagigen bis 100-lagigen Leiterplatten.

-

Qualität in Militärqualität: 3A + 2.5Cpk-Prozesssteuerung.

-

Risikominderung: Die proprietäre DFM-Engine verhindert 90% Designfehler.

-

Grüne Herstellung: 99.8% Goldsalzgewinnung, RoHS 3.0 konform.

“While you receive ±3% impedance test reports,

We’ve compressed tolerances to ±0.8% in our labs.”

- Chefingenieur Zhou, UGPCB-Hochgeschwindigkeitssignallabor

Starten Sie noch heute Ihren Technologiesprung

Warum 3,000+ Globale Technologiefirmen vertrauen UGPCB:

50% Faster High-End PCB Production | 48-Hour Rush Turnaround | 15% Bulk Cost Reduction

Fragen Sie unsere Ingenieure nach kompetenten PCB- und PCBA-Lösungen.

Erklärung zur Datenüberprüfung:

Die in diesem Dokument zitierten 5G-Smartphone-Lieferdaten stammen aus dem IDC Q2 2023 Bericht. Der Kostenanteil kupferkaschierter Laminate (CCL) is referenced from Prismark Partners’ industry analysis, und die Prozessfähigkeitsparameter sind von Underwriters Laboratories zertifiziert (UL LLC). Formelableitungen entsprechen den IPC-2141A-Standardspezifikationen für starre Leiterplatten (Leiterplatte) Design.