Im Bereich der Analogie Schaltungsdesign, Betriebsverstärker, Präzisionswiderstände, und Kondensatoren beanspruchen oft das Rampenlicht. Die wahre Determinante der Systemleistungsgrenzen ist jedoch der verborgene Mastermind, der hinter den Kulissen arbeitet: Die Leiterplatte (Leiterplatte). Diese stille Stiftung trägt alle Komponenten während der Regierung Signalintegrität, Geräuschunterdrückung, Und Systemzuverlässigkeit durch jeden Millimeter Spur, jede dielektrische Schicht, und jede Erdungsentscheidung.

PCB -Materialwissenschaft: Dekodieren von Hochfrequenzleistung über FR-Bewertungen hinaus

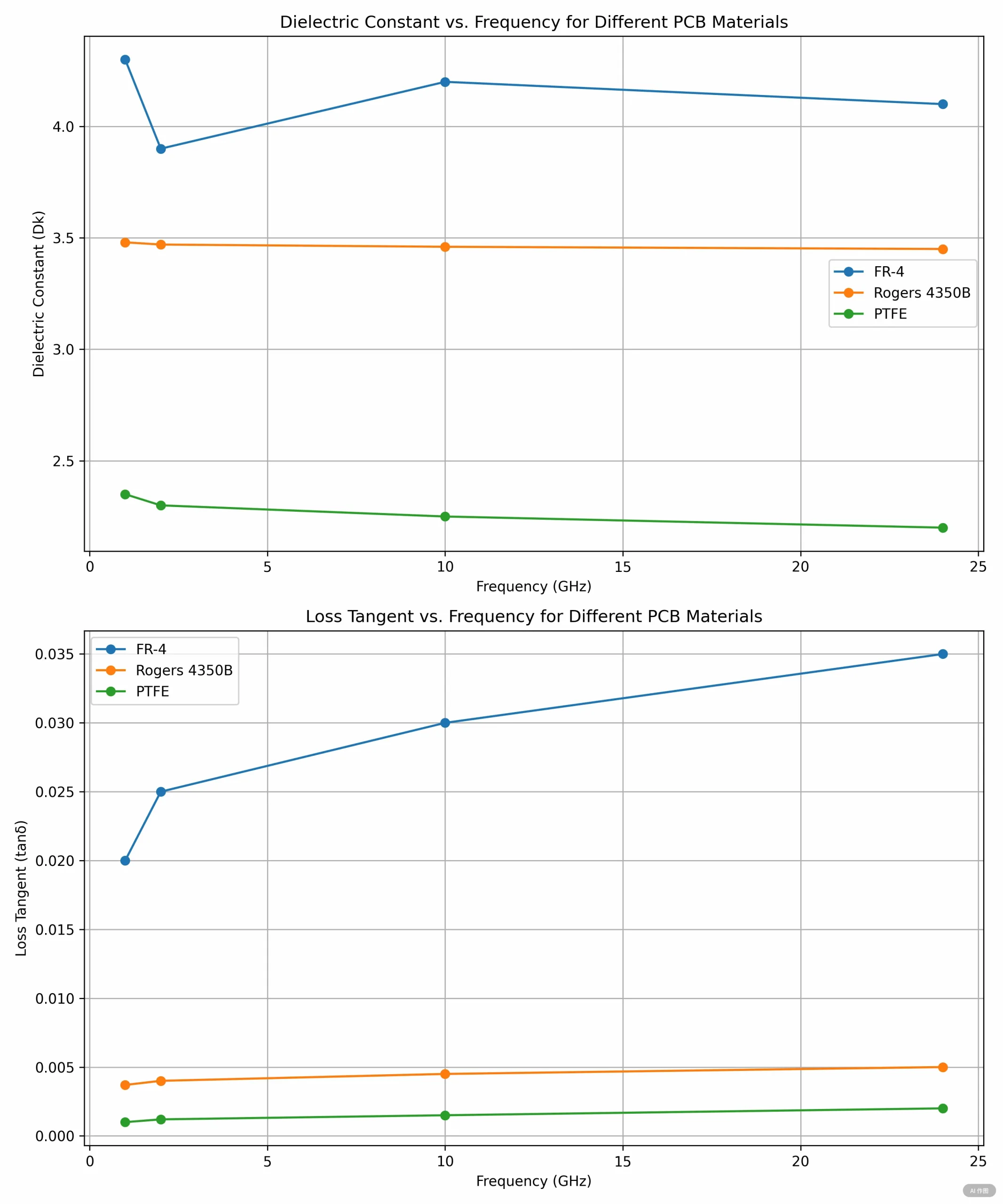

Bei diskutieren PCB -Materialien, FR-4-Entflammbarkeitswerte sind lediglich der Prolog. Für Hochgeschwindigkeitsanaloge Schaltungen, Dielektrizitätskonstante (Dk) Und Dissipationsfaktor (Tan & Dgr;) sind die unsichtbaren Hände, die das Signalschicksal formen.

Signalausbreitungsgeschwindigkeit (v) wird bestimmt von:

v = c / √(ε_r)

Wo * c * = Lichtgeschwindigkeit, E_R = Relative Permittivität. FR-4s ε_r schwankt zwischen 4.2-4.8, sich bis zu 5% Signalverzögerungsvariation. Kritischer, seine Verlustmerkmale - bei 10 GHz, Standard FR-4 zeigt Tan- & Dgr; = 0,02, Gleichstellung zu 0.5DB -Signalverlust pro Zoll.

Feuchtigkeits-Temperatur-Zusammenspiel beweist sich in Präzisionsschaltungen besonders tödlich:

-

1% Feuchtigkeitsabsorption reduziert den Oberflächenwiderstand von FR-4 um drei Größenordnungen

-

15% DK -Drift bei 85 ° C Verschiebungen Filterzentrum Frequenzen katastrophal

Experte Einsicht: Medizinische PCBs mit Rogers 4350b (E_r = 3,48 ± 0,05) pflegen <2% DK -Variation von -40 ° C bis +150 ° C -kritisch für lebenserhaltende Überwachungsgeräte.

PCB -Stackup -Architektur: Technische aktuelle Pfade & EMI -Abschirmung

Einzel-/Doppelschichtbeschränkungen

Jenseits von 10 MHz Signalen, 1.6mm doppelseitige Bretter zeigen Erdungsschwächen der Erdungsschicht. Zwischenschichtkapazität:

C = (ε_0 * ε_r * A) / d

Standard 1,6 -mm -Boards erreichen nur 35PF/in² - unzureichend für >100MHz -Rauschunterdrückung.

Vierschichtige Stackup Revolution

Dedizierte Kraft-/Bodenebenen transformieren Impedanzkontrolle:

-

0.2MM Dielektrik

-

Der Widerstand der Bodenebene fällt auf 1/100. Einschicht ab

-

Strahlungsgeräuschdämpfung verbessert sich um 40 dB

Erdungsstrategien: Festlegung analog-digitaler Abgrenzung

Ebene Isolationskritikalität

Überlappende digitale/analoge Bodenebenen erzeugen kapazitive Rauschkanäle:

C_coupling = (ε * A_overlap) / d

Sogar 0,1 mm² Überlappung in 1,6 mm Brettern erzeugt eine 0,3-PF-Kopplungskapazität-genug, um 100-MHz-Taktrauschen in analoge Signale auf μV-Ebene zu injizieren.

Sternsteinprinzip

Ein-Punkt-Erdung beseitigt mathematisch Grundschleifen:

V_noise = -dΦ/dt = -2πf * B * A

Wo B = magnetische Flussdichte, A = Schleifenbereich. Konvergierende Pfade an einem Punkt minimieren den Schleifenbereich.

Komponentenfrequenzmaskierung: Wenn Widerstände Induktoren werden

Resistive Parasitics

0805 Filmwiderstände enthalten ~ 2NH -parasitäre Induktivität. Bei 100 MHz:

X_L = 2πfL = 1.26Ω

Überschreiten typische Widerstandswerte, grundsätzlich verändern das Verhalten des Schaltkreises.

Kapazitive Selbstresonanzfalle

Kondensatorimpedanz folgt:

|Z| = √[R_ESR² + (X_L - X_C)²]

Standard 10 μf Tantal-Kondensatoren selbst resonieren bei 300 kHz, Outperformiert durch 0,1 μF -Keramik bei 10 MHz:

Routing -Geometrie: Die EM -Katastrophe von 90 ° Biegung

Rechtwinkelspuren wirken als verborgene Antennen in Hochgeschwindigkeiten PCB -Layouts:

-

Effektiv erhöhen die Spurlänge durch 26%

-

Eckkapazität verursacht Impedanzdiskontinuitäten

-

30 dB effizienter ausstrahlen als 45 ° -Bücken

Vias bieten gleiche Gefahren. Eine parasitäre Induktivität von 0,3 mm Viacasitär:

L ≈ 5.08h [ln(4h/d) + 1] (pH)

Wo * h * = Brettdicke (mm), *D* = Lochdurchmesser (mm). Bei 1 GHz, Single via in 1,6mm Board erzeugt 1,6 Ω -Reaktanz.

Endgültige Verteidigung: Von der Nano-Reinigung bis zu Faraday-Gehäusen

Ionische Kontaminationskontrolle

Hoch-Impedanzknoten erfordern unten ionische Rückstände:

<1.56 μg/cm² (IPC J-STD-001 Class 3)

Ultraschallreinigung mit DI -Wasser erreicht <0.3μg/cm².

EMI -Abschirmung Effektivität

Faraday Cage Performance folgt:

SE(dB) = 20log[(Z_0)/(4Z_s)] + 20log(e^(t/δ))

Wo D = Hauttiefe. 1MM Aluminium bietet eine 120 -dB -Dämpfung bei 1 GHz, Aber 0,1 mm Lücken verschlechtern dies auf 30 dB.

Die Offenbarung des unsichtbaren Architekten

Daten zeigen eine verblüffende Wahrheit: 68%+ Schaltungsfehler stammen aus PCB -Designfehler. Einmal als bloße Komponententräger angesehen, PCBs sind eigentlich Missionskritische Systemarchitekten.

In 10 -GHz -Schaltungen:

-

F-4-Dielektrizitätsverlust kann 15 dB Signalenergie verbrauchen

-

0.5mm gemahlene Sprünge induzieren 300mV gemahlene Sprung

-

Mikroskopische Flussreste erzeugen Leckagepfade

Die Designrevolution beginnt mit dem Paradigmenwechsel: Klassifizieren Sie PCBs von Kostenartikeln nach Kernfunktionselemente. Wenn Sie Ihren nächsten Op-Amper auslegen:

-

Diese Verbesserung von 0,1 dB Lärm lebt in Laminat -DK -Werten

-

Diese 3Ps -Timing -Ränder befinden sich in der Dicke der Bodenebene

Elevate this “invisible architect” from backstage to center stage, Und Ihre analogen Schaltungen werden Leistungsbarrieren zerstören.