Im Bereich von Hochgeschwindigkeits-PCB-Design und RF -Schaltungen, Impedanzkontinuität ist für die Signalintegrität von entscheidender Bedeutung. Mismatch für charakteristische Impedanz kann zu einer Signalreflexion führen, Klingeln, und Verzerrung, Schwere Auswirkungen auf die Systemleistung. Dieser Artikel befasst sich mit den Ursachen der Impedanzdiskontinuität und bietet branchengefahrte Lösungen, mit denen Ingenieure optimieren können PCB -Designs.

Charakteristische Impedanz und ihre Bedeutung verstehen

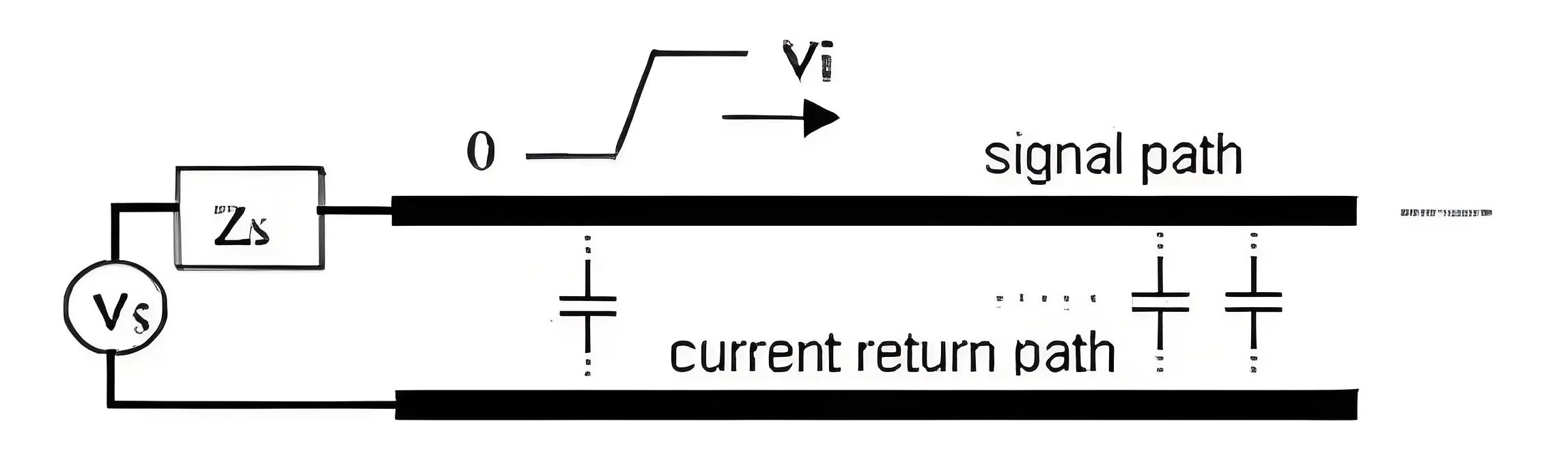

Charakteristische Impedanz ist ein Kernkonzept in Hochfrequenz-Leiterplatte Signalübertragung. Gemäß dem IPC-2141A-Standard, als Signal verbreitet sich entlang einer Übertragungsleitung, Zwischen der Signallinie und der Referenzebene wird ein elektrisches Feld gebildet, Erstellen eines sofortigen Stroms. Wenn die Übertragungsleitung einheitlich ist, Es wird ein äquivalenter Widerstand gebildet, definiert als das Verhältnis von Spannung zu Strom (Z = v/i). Dies ist die charakteristische Impedanz.

Wenn sich die charakteristische Impedanz entlang des Übertragungsweges ändert, Signalreflexion tritt am Punkt der Diskontinuität auf. Diese Reflexion kann eine Signalverzerrung verursachen, Timingfehler, und elektromagnetische Störung (EMI) Probleme. Laut IEEE -Forschung, eine Impedanzabweichung überschritten 10% kann die Signalintegrität stark beeinträchtigen.

Schlüsselfaktoren, die die charakteristische Impedanz beeinflussen

Die charakteristische Impedanz wird hauptsächlich durch vier Parameter beeinflusst: Dielektrizitätskonstante (Dk), Substratdicke (H), Spurenbreite (w), und Kupferdicke (T). Die charakteristische Impedanzformel für eine Microstrip -Linie kann als angenähert werden:

Z0 = (87 / √(εr + 1.41)) * ln(5.98H / (0.8w + T))

Wobei εr die relative dielektrische Konstante des Substrats ist. Diese Formel, abgeleitet vom IPC-2141-Standard, ist für vorläufige Berechnungen geeignet, Für das tatsächliche Design sollten jedoch professionelle Impedanzberechnungsinstrumente verwendet werden.

Fünf gemeinsame Impedanzdiskontinuitätsprobleme und ihre Lösungen

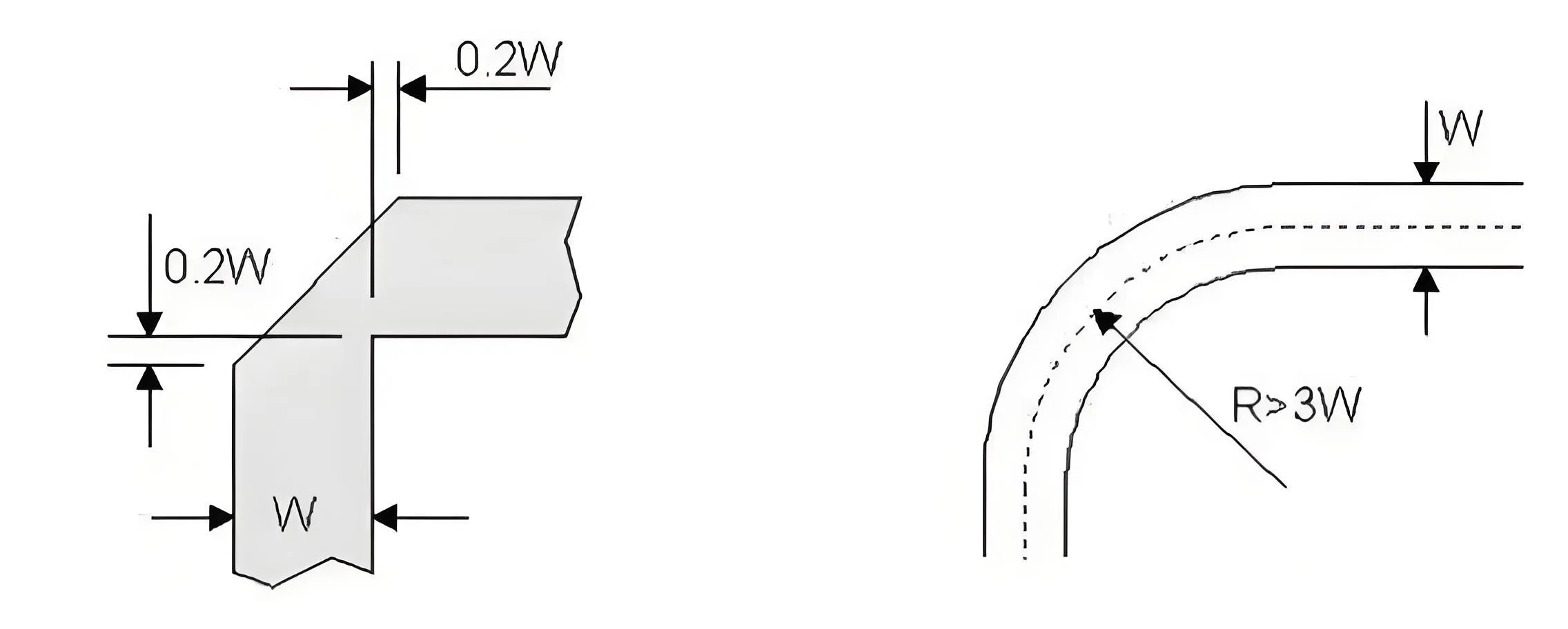

1. Plötzliche Veränderungen der Spurenbreite und sich verjüngendes Liniendesign

Viele HF -Komponenten haben kleine Paketgrößen, mit SMD -Pad -Breiten möglicherweise so klein wie 12 Mils, Während HF -Signalspuren häufig Breiten oben erfordern 50 Mils. Dieser Größenunterschied führt zu einer signifikanten Impedanzdiskontinuität.

-

Lösung: Verwenden Sie sich verjüngte Linien für Übergänge; Vermeiden Sie abrupte Veränderungen der Breite. Die Verjüngung sollte glatt sein, und seine Länge sollte nicht übermäßig sein. Gemäß den IPC-2221-Richtlinien, Die sich verjüngende Neigung sollte zwischengehalten werden 1:3 Und 1:5 Um eine allmähliche Impedanzänderung zu gewährleisten.

2. Optimierung der Übertragungsleitungs -Ecke

Der rechtwinklige Biegungen in HF-Signalspuren erhöht die effektive Spurenbreite, Dies führt zu Impedanzdiskontinuität und Signalreflexion.

Lösung: Müster oder abgerundete Ecken auftragen. Der Radius einer abgerundeten Ecke sollte R erfüllen > 3W (wo w die Spurbreite ist) Diskontinuität effektiv reduzieren. Eine 45 ° Gehrte Ecke ist eine weitere effektive Methode, mit der Gehrungslänge typischerweise größer als 1.5 mal die Spurbreite.

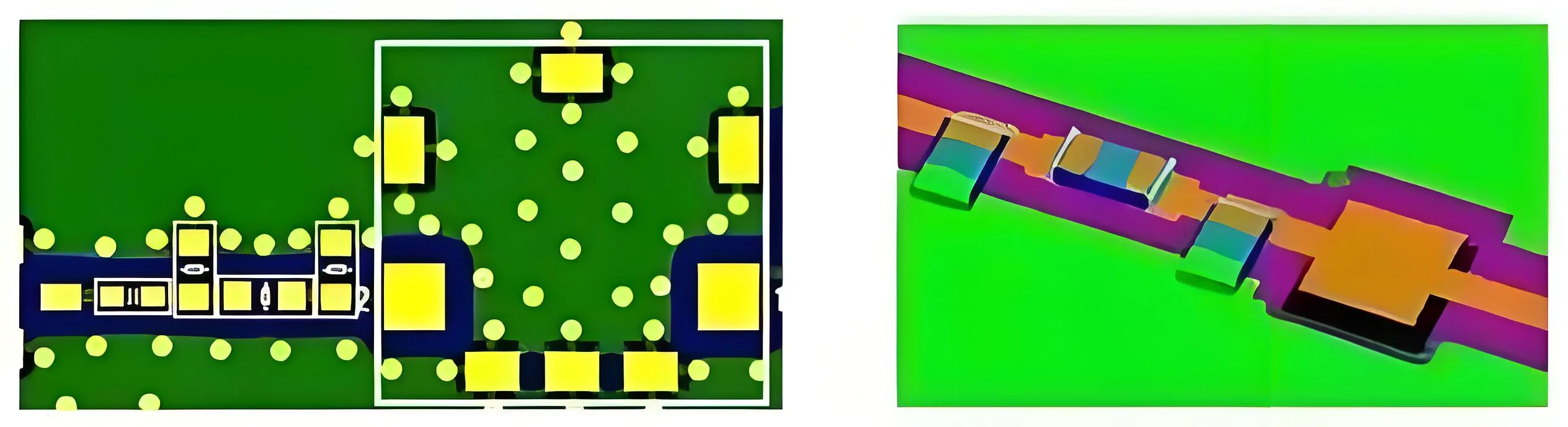

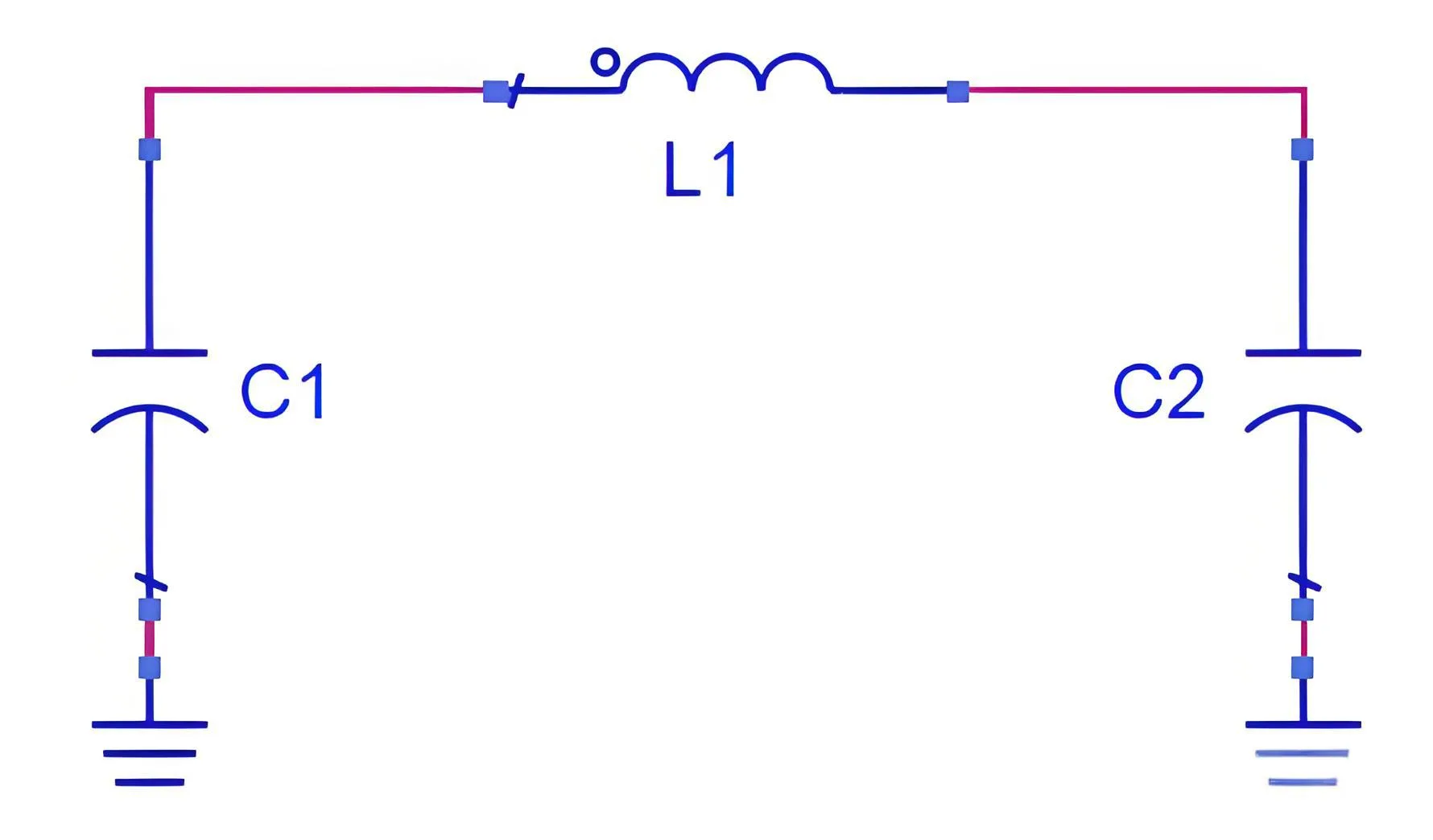

3. Minderung der kapazitiven Wirkung großer Pads

Wenn ein großes Komponentenkissen auf einer 50-Ohm-Mikrostreifenlinie platziert wird, Es führt eine parasitäre Kapazität ein, Störung der charakteristischen Impedanz.

Lösung: Kombinieren Sie zwei Verbesserungsmethoden: Erhöhen Sie die Dicke der Microstrip -Substrat und erzeugen Sie einen Clearance (oder “ausgeschnitten”) in der Erdungsebene unter dem Pad, um den kapazitiven Effekt zu verringern. Die Freigabefläche sollte sich mindestens ausdehnen 20 Mils jenseits des Pads von allen Seiten, um eine ausreichende Isolation zu ermöglichen.

4. Optimierte PCB über das Design

VIAS ist eine Hauptquelle für Impedanzdiskontinuität aufgrund ihrer parasitären Parameter, die Hochgeschwindigkeitssignalübertragung beeinflussen.

* Per parasitäre Kapazitätsformel:

C = (1.41 * εr * T * D1) / (D2 – D1)

*Wobei T Board -Dicke ist, D1 ist der Via Pad -Durchmesser, D2 ist der Anti-Pad-Durchmesser, und εr ist die dielektrische Konstante.*

* Per parasitäre Induktivitätsformel:

L = 5.08 * H * [ln(4H / D) + 1]

Wo H die Via Länge ist (Stublänge), und D ist der Bohrendurchmesser.

-

Lösungen:

-

Verwenden Sie die VIC-in-Pad-Technologie, um die Pad-Größe zu minimieren.

-

Optimieren Sie den Anti-Pad-Durchmesser (Typischerweise 10-20 Mils größer als die Via Pad).

-

Verwenden Sie das Back-Drilling, um den nicht funktionsfähigen über Stub zu entfernen.

-

Für Signale von mehr als 1 GHz, Führen Sie Simulation und Optimierung mithilfe von Tools wie HFSS und Optimetrics durch.

-

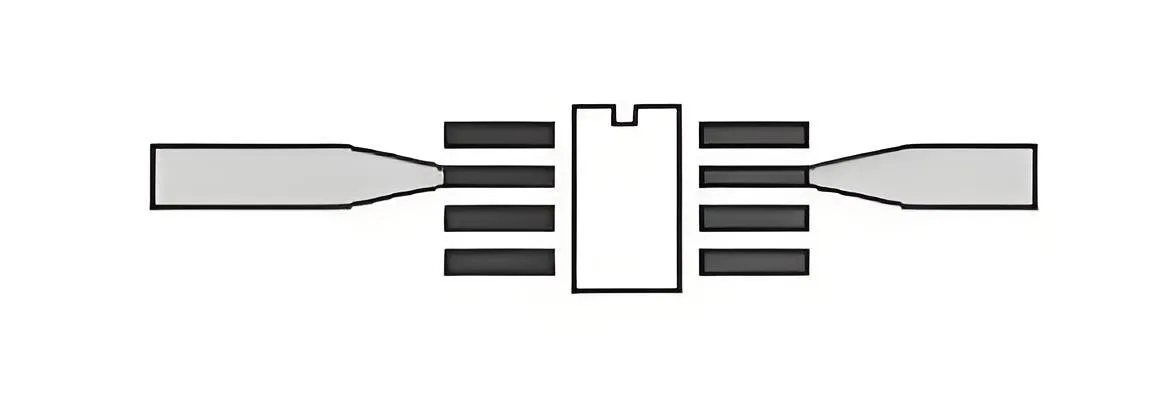

5. Durchleitungs-Koaxial-Stecker-Optimierung

Durch Koaxialanschlüsse durch die LOLE stellen ähnliche Impedanzdiskontinuitätsprobleme als VIAS auf.

-

Lösung: Wenden Sie die gleichen Optimierungstechniken an, die für VIAS verwendet werden, einschließlich Via-in-Pad, richtiger Fanout, und Optimierung des Anti-Pad-Durchmessers. Erdungspräparat sollte gleichmäßig um den Stecker platziert werden (mindestens 4) Um eine ausgezeichnete Bodenkontinuität zu gewährleisten.

Fortgeschrittene PCB -Fertigungstechnologien zur Impedanzkontrolle

Die moderne PCB -Herstellung bietet verbesserte Fähigkeiten zur Impedanzkontrolle:

-

Streng kontrollierte Laminierung: Sorgt für eine gleichmäßige Substratdicke mit Toleranzen innerhalb von ± 10%.

-

Laser Direct Imaging (LDI): Bietet eine sehr präzise Steuerung der Spurenbreite, mit Genauigkeit bis ± 0,2 mil.

-

Auswahl der Oberfläche: Auswahl der richtigen Oberflächenbeschaffung (z.B., ZUSTIMMEN, Eintauchen Silber) hilft, die Auswirkungen auf die Impedanz zu minimieren.

Laut IPC-6012d, Impedanzkontrollverträglichkeit für die Klasse 3 (Hochzuverlässige) Produkte sollten innerhalb von ± 10% gehalten werden. Einige anspruchsvolle Anwendungen erfordern noch engere Toleranzen von ± 5% oder strenger.

Entwurfsprüfung und Testempfehlungen

Um die Kontinuität der Impedanz zu gewährleisten, Implementieren Sie die folgenden Maßnahmen:

-

Vor-Layout-Simulation: Führen Sie Impedanzberechnungen mit Tools wie Si9000 oder polaren Instrumenten durch.

-

Post-Layout-Simulation: Überprüfen Sie die Berechnungen mit tatsächlichen Stapelparametern.

-

TDR -Tests: Verwenden Sie ein Zeitdomänenreflexionometer, um die tatsächlichen Impedanzwerte nach der Produktion zu messen.

-

Querschnittsanalyse: In regelmäßigerer Prüfungsleitungsfunktionen durch Überprüfung der tatsächlichen dielektrischen Dicke und der Spurenbreite.

Abschluss

Impedanzdiskontinuität im PCB -Design ist unvermeidlich, Die Auswirkungen können jedoch durch wissenschaftliche Entwurfsmethoden und fortschrittliche Fertigungstechniken minimiert werden. Der Schlüssel zur Behandlung dieses Problems liegt in der Verständnis der Grundursachen für Impedanzvariationen und die Anwendung geeigneter Designstrategien. Für Hochgeschwindigkeits- und Hochfrequenzanwendungen, Es ist ratsam, mit erfahrenen Lieferanten zusammenzuarbeiten, wie UGPCB, die hochmoderne Produktionsanlagen und umfangreiche Fachkenntnisse zur Impedanzkontrolle besitzen. Solche Lieferanten sind in der Lage, PCB -Herstellung zu liefern und PCBA-Montage Dienste, die strenge Leistungsanforderungen entsprechen.

Wenn Sie nach einer professionellen PCB -Fertigung suchen und Leiterplatte Dienstleistungen, Kontaktieren Sie uns für ein sofortiges Angebot und einen technischen Support. Unser Engineering -Team wird umfassende Impedance -Lösungen von Design bis zur Produktion anbieten, Stellen Sie sicher, dass Ihr Produkt eine optimale Leistung erzielt.

UGPCB-LOGO

UGPCB-LOGO

Sie lassen es mit Ihrer Präsentation eigentlich so einfach erscheinen, aber ich

Ich finde, dass es sich bei diesem Thema tatsächlich um etwas handelt, von dem ich glaube, dass ich es nie verstehen würde.

Es erscheint mir zu komplex und extrem weit gefasst.

Ich freue mich auf Ihren nächsten Beitrag, Ich werde versuchen, den Dreh rauszubekommen!