A mere 0.5mm² crack in a BGA solder pad can brick a premium smartphone into a “white-screen paperweight” – while conventional underfill encapsulation merely disguises this critical PCB reliability threat. Da entwickeln sich Smartphones schnell zu ultradünnen Designs und Hochleistungsspezifikationen, BGA Pad Cracking has become the Damocles’ sword hanging over Leiterplatte Herstellung. Wenn a $1,000+ Mobiltelefon Leiterplattenbestückung wird aufgrund von Mikroverrückungen oder Marktrenditeschriften Schrott 30% aus Typ V Frakturen, Wir müssen fragen: Ist unteraberdlich die ultimative Lösung?

1. BGA Pad Cracking: Der unsichtbare Mörder der Elektronik

H3: 1.1 Versagensdefinition & Fünf Bruchtypen

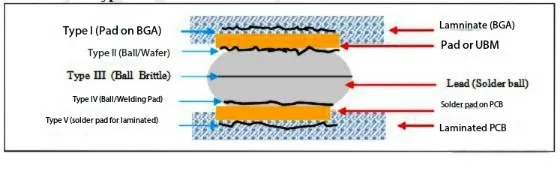

BGA Pad Cracking bezieht sich auf die Trennung zwischen IC -Chips und PCB -Pads unter mechanischer/thermischer Spannung. Fünf Bruchtypen werden nach Ort klassifiziert:

| Typ | Ausfallort | Prävalenz | Hauptauslöser |

|---|---|---|---|

| Typ I | Chip -Substrat Schicht | 12% | Tenblement -Tests, mechanischer Schock |

| Typ II | BGA Pad-Solder-Schnittstelle | 18% | Thermalradfahren |

| Typ III | Bleifreier Lötball | 25% | Tropfenaufprall, thermischer Schock |

| Typ IV | Löten-PCB-Pad-Gelenk | 28% | Reflow -Profil -Nichtübereinstimmung |

| Typ v | Pad-Substrat-Trennung | 17% | Strukturelle Verformung, Materialverschlechterung |

1.2 Stealth Natur & Zerstörerische Auswirkungen

Traditionelle SMT -Inspektion erkennt <5% von Pad -Rissen aufgrund von:

-

Mikro-Crack-Größen (5-50μm) verdeckt in mehrschichtigen PCBs

-

Elektrische Kontinuität wird oft trotz Brüche beibehalten

-

Unterfüllmasken Risse, ohne die Ausbreitung zu stoppen, Erfordernde destruktive Entfernung während der Nacharbeit

2. Ursachenanalyse über den PCBA -Workflow hinweg

2.1 Materieller Herkunft: Kupferfolie -Kristallstruktur -Divergenz

Experimentelle Daten zeigen: Copper foil with specialized “grape-like” nodular structures delivers 18.5% höhere Haftung als herkömmliche Kristalle.

2.2 PCB -Substrat Einschränkungen: FR4s thermische Ausdauerkrise

Bleifreie Lötanforderungen Spitzentemperaturen von 248 ° C (+33° C gegen traditionelle Prozesse). Standard FR4 TG von 130-140 ° C. Ursachen:

-

Z-Achse CTE >300 ppm/° C.

-

T288 Delaminierungszeit <3 min (Industrie erfordert >5 min)

Kritische Formel: Wärmelspannung = e × α × ΔT

Wo:

σ = thermische Spannung (MPA), E = elastischer Modul (GPA),

α = CTE (ppm/° C.), ΔT = Temperaturänderung (°C)

*High-CTE-Substrate erzeugen 1,8 × mehr Spannung bei ΔT = 100 ° C*

2.3 PCB-Design Fallstricke: Übersehene mechanische Spannung

Analyse von 7,000 Fehlgeschlagene Einheiten in russischen Märkten Shows:

-

0.80MM -Boards fehlten 3,2 × mehr als 1,00 mm Bretter

-

T-Card-Slots erhöhten das PCBA-Rissrisiko durch 47%

-

Große Komponenten unter BGA -Zonen verursachten eine asymmetrische thermische Verformung

3. Kritische PCB -Prozesssteuerungsdurchbrüche

3.1 PCB -Fertigungsoptimierungsmatrix

| Verfahren | Konventionell | Optimiert | Verbesserung |

|---|---|---|---|

| Kupferfolie | Standardknoten | Traubenartige Kristalle | Adhäsion ↑ 18,5% |

| Dicke der Überlieferung | 18-23μm | ≥30 μm | Zugfeste ↑ 32% |

| Oberflächenvorbereitung | Gürtelscheiben | Mikro-Echung + Spray | Kupferverlust ↓ 60% |

| Lötmaskenöffnung | Kreisförmig | Hexagonal | Einfügen von Fluss ↑ 40% |

3.2 Reflow -Profilrevolution

Fehlerwurzel: Standard -Reflow verbringt nur 12S -Kühlung von 190 ° C → 130 ° C, schnelle Kontraktion verursachen.

Lösung: Erweitern Sie die Verweilzeit über TG durch 150%, Verringerung des thermischen Stresses durch 35%.

4. Umfassende PCBA -Lösungsdatenbank

4.1 Designinnovationen

-

Pad -Geometrie: Periphere Pads in oval umwandeln (lange Achse +0,1 mm)

-

Stackup -Design: Fügen Sie lokalisierte Kupferbilanzschichten unter BGAs hinzu

-

Freigaberegel: Groß sein Komponenten Innerhalb von 3 mm von BGA -Zonen

4.2 Material -Upgrade -Pfad

-

Geben Sie FR4 mit TG ≥ 170 ° C an

-

Kontrollkupferfolie RZ kontrollieren (Rauheit) bei 3,5-5,0 μm

-

Adopt Low-CTE (<2.5%) High-Tougness-Harzsysteme

4.3 Prozesssteuerung Redline

-

Kupferbeschichtung ≥ 30 μm (validiert)

-

OSP -Panelabstand >5mm (Vorbeugung von Säure -Fangen)

-

Testanlagendruck ≤ 7 kg/cm², Lebensdauer <500k Zyklen

-

150-180° C Reflow Zone wohnen ≥ 90 Sekunden

5. Zukünftige Technologie -Roadmap

Als HDI-Leiterplatten Vorwärts in Richtung 0,4 mm Dicke voranschreiten und BGA -Pads unter 0,2 mm schrumpfen, Durchbrüche erforderlich:

-

Kupferbehandlung im Nano-Maßstab: Magnetron-ausgeprägte Adhäsionsschichten

-

CTE-Adaptive Substrate: Temperaturresponsive Polymerverbundwerkstoffe

-

KI -Prozessüberwachung: Echtzeit-Lötkollotengesundheitsvorhersage in Echtzeit

Abschluss: Zuverlässigkeit ist in entworfen

BGA Pad Cracking bildet Zuverlässigkeitsausfall auf Systemebene. Nach-Implementierungsergebnisse:

-

Tanbling -Testpassrate: 82% → 99.6%

-

Marktrendite: ↓ 70%

-

Kostensenkung: $1.20/Vorstand über die Eliminierung der Unterfüllung

*Erinnern: Ein Anstieg der Adhäsion pro Pad um 0,1 kgf liefert exponentielle Zuverlässigkeitsgewinne. Dies überträgt die Verfeinerung der Prozessverfeinerung-sie verkörpert das ultimative Streben nach Null-Defekt-Fertigung.*

Im mikroskopischen Bereich von Lötkissen, Traubenähnliche Kupferkristalle weben Schutznetzwerke im Nano-Maßstab, während führende Kugeln in hexagonalen Maskenöffnungen Präzisionstänze durchführen. Die Elektronik -Zuverlässigkeitsrevolution beginnt mit unerschütterlichem Engagement für alle 0,01 mm.