En el reino del análogo diseño de circuito, amplificadores operativos, resistencias de precisión, y los condensadores a menudo reclaman el centro de atención. Sin embargo, el verdadero determinante de los límites de rendimiento del sistema es la mente maestra oculta que funciona detrás de escena: el Placa de circuito impreso (tarjeta de circuito impreso). Esta base silenciosa lleva todos los componentes mientras rige Integridad de señal, supresión de ruido, y confiabilidad del sistema a través de cada milímetro de rastreo, Cada capa dieléctrica, y cada decisión de base.

PCB Materials Science: Decodificación de rendimiento de alta frecuencia más allá de las clasificaciones FR

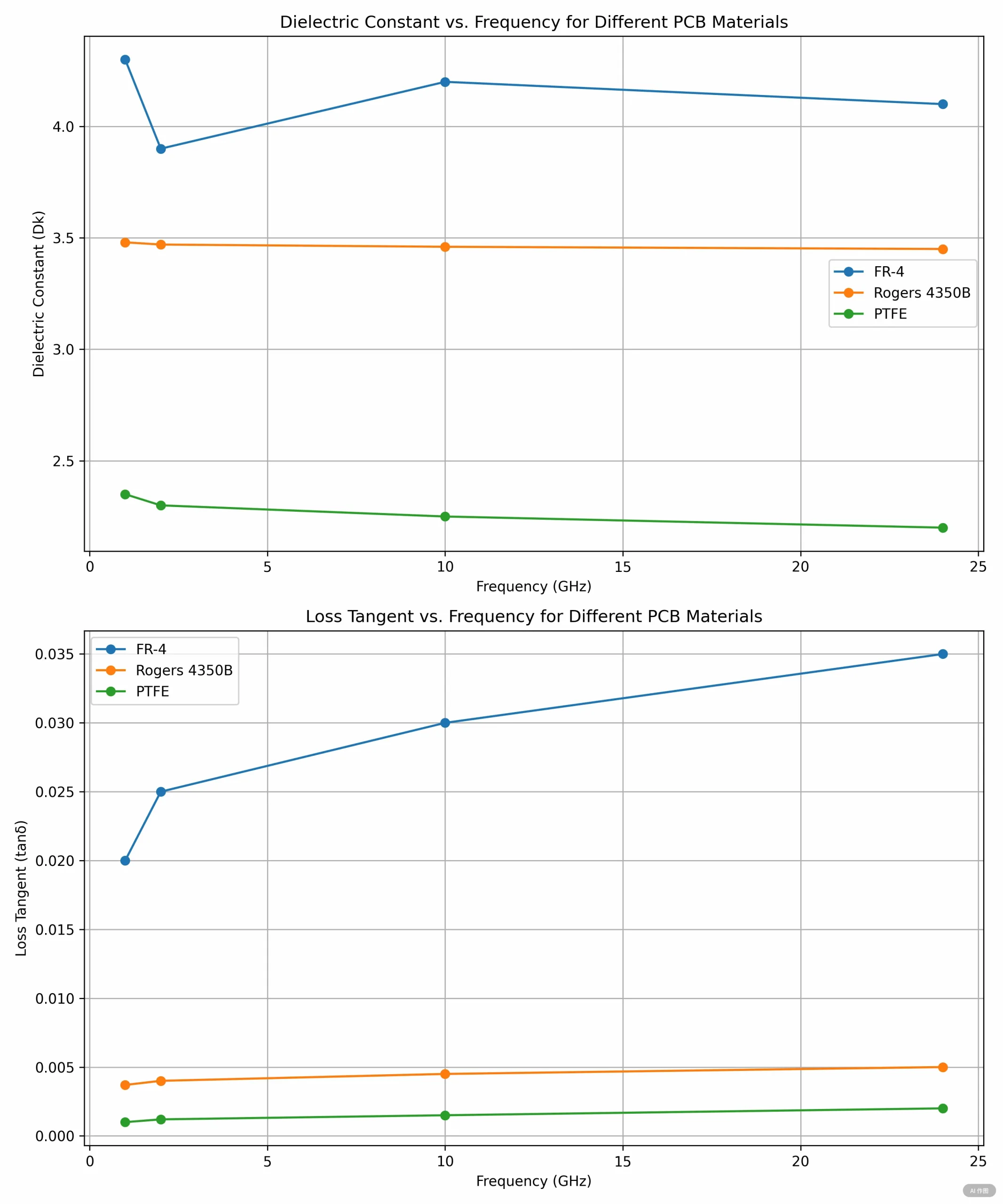

Al discutir Materiales de PCB, Las clasificaciones de inflamabilidad FR-4 son simplemente el prólogo. Para circuitos analógicos de alta velocidad, Constante dieléctrica (Dk) y Factor de disipación (tanδ) ¿Son las manos invisibles que forma el destino de la señal.

Velocidad de propagación de la señal (V) está determinado por:

v = c / √(ε_r)

Donde * c * = velocidad de la luz, E_R = Permitividad relativa. FR-4's ε_R fluctúa entre 4.2-4.8, causando 5% Variación de retraso de la señal. Más críticamente, sus características de pérdida: a 10 GHz, El FR-4 estándar exhibe Tanδ = 0.02, equivalente a 0.5Pérdida de señal de DB por pulgada.

Interacción de temperatura humedad resulta particularmente letal en los circuitos de precisión:

-

1% La absorción de humedad reduce la resistencia de la superficie FR-4 en tres órdenes de magnitud

-

15% Dk Drift a 85 ° C desplazamientos del centro de filtro frecuencias catastróficas

Insight de expertos: PCB médicos usando Rogers 4350B (E_r = 3.48 ± 0.05) mantener <2% Variación DK de -40 ° C a +150 ° C -Crítico para el equipo de monitoreo de mantenimiento de la vida.

Arquitectura de pila PCB: Ingeniería de rutas actuales & EMI blindaje

Limitaciones de una sola/doble capa

Más allá de las señales de 10MHz, 1.6Las tablas de doble cara mm revelan debilidades de capa de conexión a tierra. Capacitancia entre capas:

C = (ε_0 * ε_r * A) / d

Las placas estándar de 1.6 mm logran solo 35pf/in², insuficientes para >100Supresión de ruido de MHz.

Revolución de pilas de cuatro capas

Power/planos de tierra dedicados Transformar el control de impedancia:

-

0.2Capacitancia de impulso de Dielectrics MM a 280pf/in²

-

La resistencia del plano de tierra cae a 1/100 de una sola capa

-

La atenuación de ruido irradiada mejora en 40 dB

Estrategias de conexión a tierra: Establecer la demarcación analógica-digital

Crítica de aislamiento del plano

Los planos de tierra digitales/analógicos superpuestos crean canales de ruido capacitivos:

C_coupling = (ε * A_overlap) / d

Incluso la superposición de 0.1 mm² en tableros de 1.6 mm genera una capacitancia de acoplamiento de 0.3pf, suficiente para inyectar ruido de reloj de 100 MHz en señales analógicas de nivel de μV.

Principio de tierra de la estrella

La conexión a tierra de un solo punto elimina los bucles de tierra matemáticamente:

V_noise = -dΦ/dt = -2πf * B * A

Dónde B = densidad de flujo magnético, A = área de bucle. Rutas convergentes en un punto minimiza el área de bucle.

Enmascaramiento de frecuencia de componentes: Cuando las resistencias se convierten en inductores

Parasítica resistiva

0805 Las resistencias de la película contienen ≈2nh inductancia parásita. A 100MHz:

X_L = 2πfL = 1.26Ω

Exceder los valores de resistencia típicos, alterar fundamentalmente el comportamiento del circuito.

Trampa de auto-resonancia capacitiva

La impedancia del condensador sigue:

|Z| = √[R_ESR² + (X_L - X_C)²]

Los condensadores de tantalio estándar 10 μF auto-resonado a 300 kHz, superado por la cerámica de 0.1 μF a 10MHz:

Enrutamiento de geometría: La catástrofe de EM de 90 ° Bend

Las trazas de ángulo rectándote actúan como antenas ocultas en alta velocidad Diseños de PCB:

-

Aumentar efectivamente la longitud de traza por 26%

-

La capacitancia de la esquina causa discontinuidades de impedancia

-

Irradiar 30dB de manera más eficiente que las curvas de 45 °

VIA presenta peligros iguales. Una inductancia parasitaria de 0.3 mm vía:

L ≈ 5.08h [ln(4h/d) + 1] (pH)

Donde * h * = grosor del tablero (milímetros), *D* = diámetro del agujero (milímetros). A 1 GHz, Single Via en la placa de 1.6 mm genera una reactancia de 1.6Ω.

Defensas finales: Desde nano-limpieza hasta faraday recintos

Control de contaminación iónica

Los nodos de alta impedancia requieren residuos iónicos a continuación:

<1.56 μg/cm² (IPC J-STD-001 Class 3)

La limpieza ultrasónica con agua DI logra <0.3μg/cm².

EMI Efectividad de blindaje

El rendimiento de la jaula de Faraday sigue:

SE(dB) = 20log[(Z_0)/(4Z_s)] + 20log(e^(t/δ))

Dónde d = Profundidad de la piel. 1El aluminio MM proporciona una atenuación de 120 dB a 1 GHz, Pero los huecos de 0.1 mm degradan esto a 30 dB.

La revelación del arquitecto invisible

Los datos revelan una verdad sorprendente: 68%+ Las fallas del circuito se originan en fallas de diseño de PCB. Una vez visto como meros portadores de componentes, Los PCB son en realidad Arquitectos del sistema de misión crítica.

En circuitos de 10 GHz:

-

La pérdida dieléctrica FR-4 puede consumir energía de señal de 15dB

-

0.5Los saltos de tierra mm inducen un rebote en el suelo de 300 mv

-

Los residuos de flujo microscópico crean rutas de fuga

La revolución del diseño comienza con el cambio de paradigma: Reclassify PCB de los artículos de costo a elementos funcionales centrales. Al exponer su próximo amplificador operacional:

-

Esa mejora de ruido de 0.1dB vive en los valores de DK laminado

-

Esos márgenes de tiempo de 3PS residen en el grosor del plano de tierra

Elevate this “invisible architect” from backstage to center stage, y sus circuitos analógicos destrozarán las barreras de rendimiento.