Introducción: La guerra a escala de milímetro en el diseño de PCB DDR5

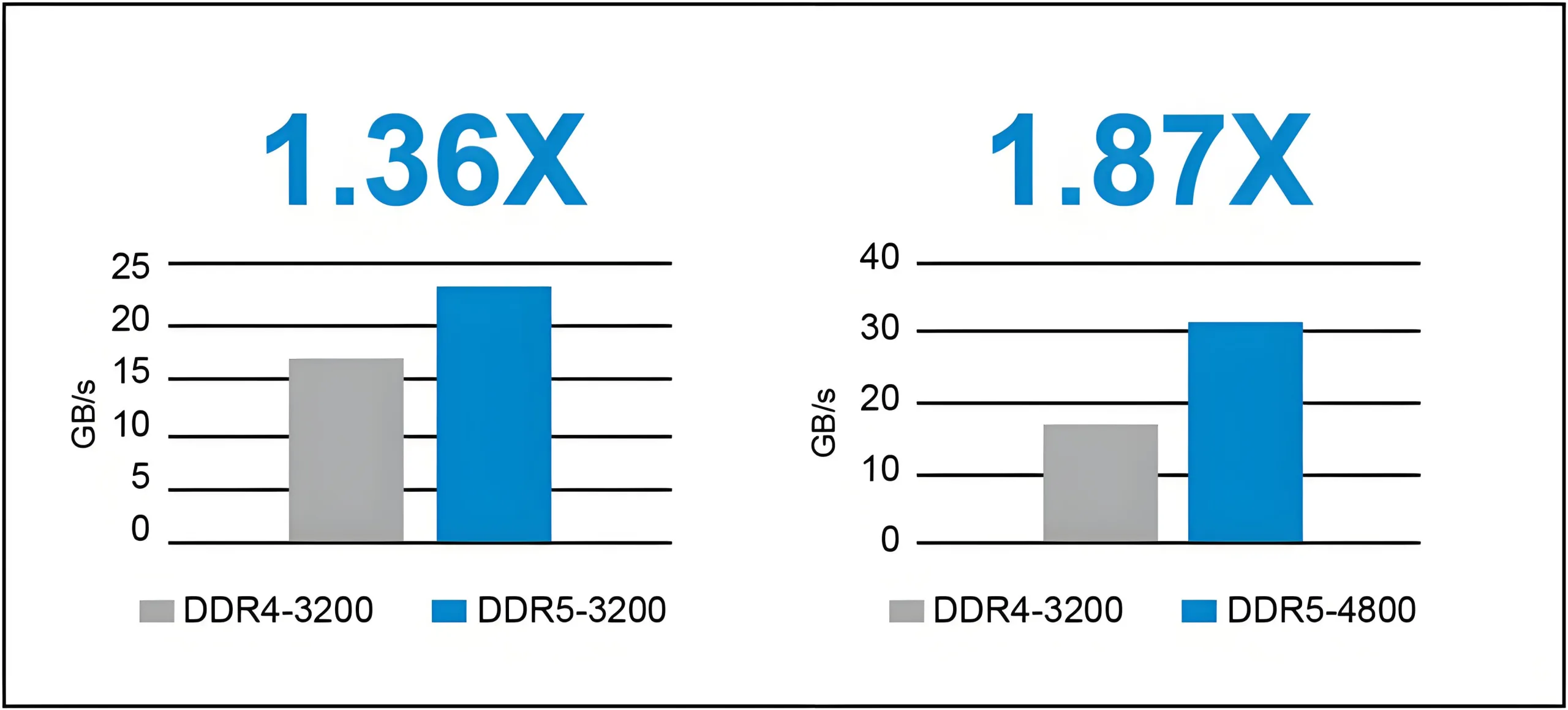

El salto de DDR4 a DDR5 marca un cambio de paradigma: Las tasas de señal surgen de 3,200 Mt/s a 6,400 MT/s mientras los voltajes de funcionamiento se desploman a 1.1V. Este desafío dual se transforma tarjeta de circuito impreso Enrutamiento desde ingeniería de conectividad simple en guerra de precisión a escala de milímetro. Los datos de la industria revelan que 80% de las fallas de diseño DDR5 se originan en problemas de enrutamiento, con 90% prevenible a través de la simulación previa a la capa. Este artículo disecciona cinco trampas críticas de enrutamiento DDR5, Apoyado por datos empíricos y estudios de casos, Entrega de soluciones procesables para profesionales de PCB.

1. DDR5 Características físicas: Por qué fallan los métodos tradicionales de diseño de PCB

1.1 Velocidad de señal y revolución de ancho de banda

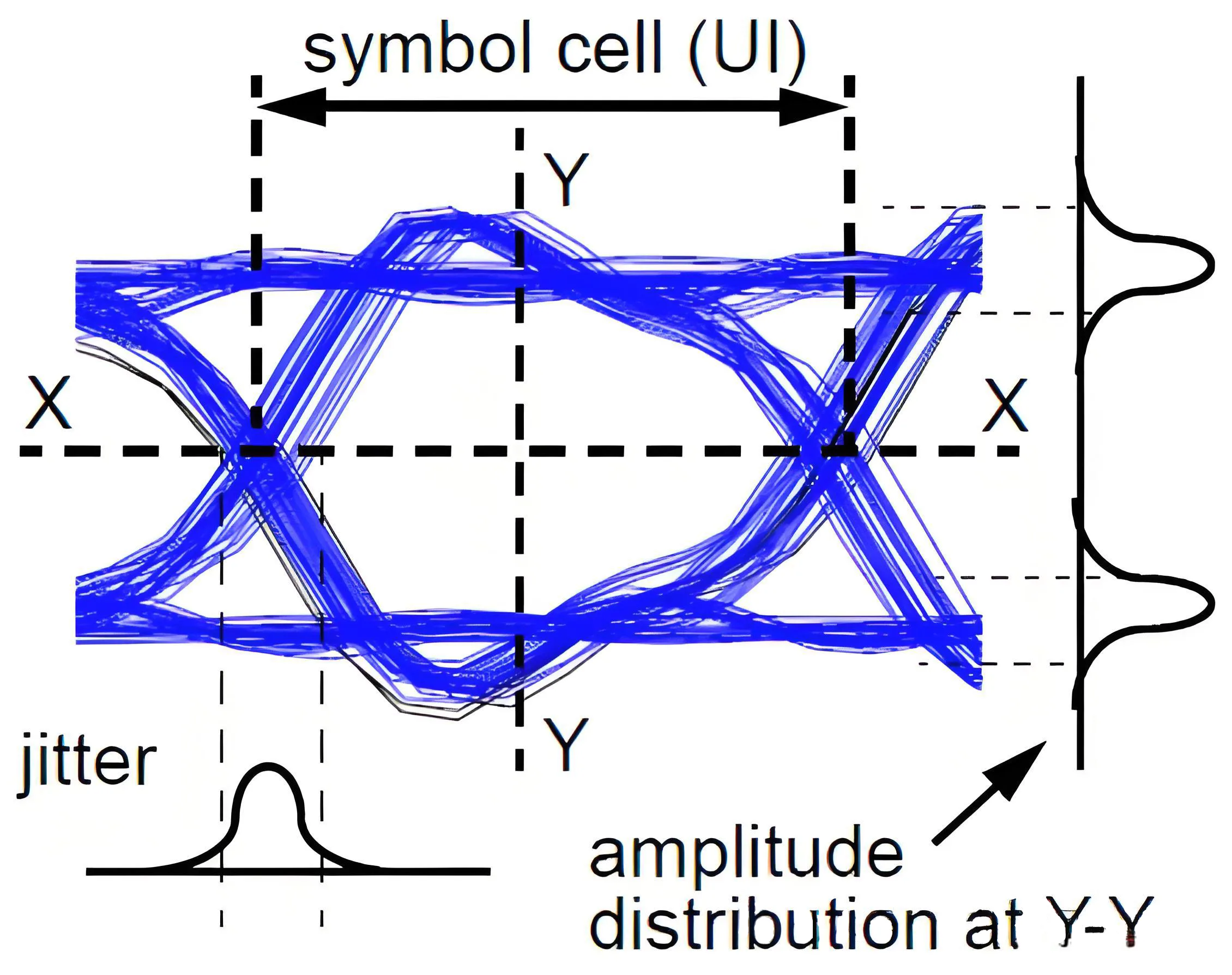

Para DDR5-6400, la frecuencia de reloj efectiva alcanza 3,200 megahercio, con tasas de borde tan rápido como 0.5 PD (20-80% tiempo de subida). Esto desencadenante:

-

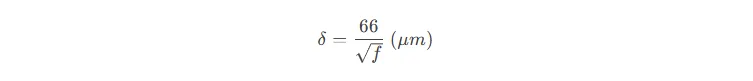

Efecto de la piel agravado: Las corrientes de alta frecuencia se concentran en superficies de conductores, reducir el espesor efectivo de cobre para 0.66 μm a 10 GHz.

-

Escalada de pérdida dieléctrica: Sustratos FR4 exhibir una tangente de pérdida (df) de 0.02 en 10 GHz, causa >3 atenuación de la señal DB/pulgada.

Validación de fórmula (Profundidad de la piel):

En F = 10 GHz, Δ≈0.66 μm,Dejando Cobre tradicional de 1oz (35 μm) con <2% utilización.

2. Cinco campos minados y contramedidas de enrutamiento de DDR5

2.1 Campo de minas 1: Error de tiempo: el umbral de supervivencia de ± 15ps

Impacto: Un desajuste de 5 millas introduce un retraso de ± 12ps, colapso del ancho del ojo horizontal por 30%.

Estudio de caso: Un diseño de GPU sufrió degradación de 10−12 a 10−7 Debido a 8 mil DQ/DQS sesgo.

Soluciones:

-

3D Compensación de enrutamiento: Reemplace los meandros de 90 ° con serpentinas de 45 °, reduciendo la capacitancia parásita por 30%.

-

Calibración de tiempo dinámico: Realizar simulaciones de Monte Carlo (Cadencia Sigrity) cubriendo ± 10% de variaciones de proceso.

Fórmula (Margen de tiempo):

tmargen= Tciclo-(tco+tvuelo+tEstar nervioso)

Para DDR5-6400 (tciclo= 0.3125 ), Alertas del sistema activada cuando tmargen<50 PD.

2.2 Campo de minas 2: Discontinuidad de impedancia: el tsunami de la señal de 5Ω

Riesgo: A través de causas de desajuste de impedancia >15 Pérdida de retorno de DB, colapso de la altura del ojo vertical por 40%.

Datos: Cada uno no optimizado a través de agrega 0.2 Pérdida de inserción de DB @5 GHz.

Soluciones:

-

A través de la revolución: Implementar vias láser-ciego (≤4mil) con compensación antipad, Limitar la variación de impedancia a ± 3Ω.

-

Optimización de la almohadilla: Use almohadillas elípticas (1.5:1 relación de aspecto) para reducir los efectos capacitivos por 20%.

Fórmula (A través del modelo de impedancia):

Zvia≈87ϵr pastel(5.98H/(0.8D1+D2))

Dónde : espesor dieléctrico, D1: a través del diámetro, : diámetro de la almohadilla.

2.3 Campo de minas 3: Retraso de la capa cruzada: el efecto de mariposa de 0.1ps/mm

Efecto de tejido de fibra: Variación constante dieléctrica (Δϵr = 0.3) por periodicidad de fibra de vidrio causa 0.6 PS/pulgada de retraso sesgo.

Soluciones:

-

Alineación del eje z: Señales de ruta del grupo de byte a ángulos de ± 45 ° para cancelar la anisotropía dieléctrica.

-

Compensación de la capa cruzada: PRELOAD SUSTRACIÓN DK/DF DATOS en herramientas EDA para la corrección de retraso automático.

2.4 Campo de minas 4: Power Ripple: la reacción de la cadena nuclear de 1 mv

Sensibilidad: 50MV Ripple a 1.1V El suministro aumenta la fluctuación del controlador por 20%.

Simulación: La impedancia objetivo de PDN debe ser ≤2 MΩ@100 MHz - 5x más estricta que los diseños tradicionales.

Soluciones:

-

3D matriz de condensadores: Desplegar 0.1 μF (0402) + 10NF (0201) condensadores cerca de ICS, cubierta 10 KHz - 2 GHz.

-

Pilares de microcopper: Incrustar pilares de 200 μm de diámetro bajo BGAS, inductancia de bucle de corte por 30%.

2.5 Campo de minas 5: Interrupción del camino de retorno: la bomba EMI invisible

Riesgo de EMI: Los planos de referencia rotos generan ruido en modo común, excediendo los límites de EMI por 10 db.

Soluciones:

-

Costura de tierra: VIA VIAS DEL TIERRA (≤0.1o) cada 100 mil entre las capas de señal.

-

Puente de plano dividido: Use condensadores enterrados (p.ej., AVX 0402B) para un acoplamiento de 10 nf a través de divisiones de potencia.

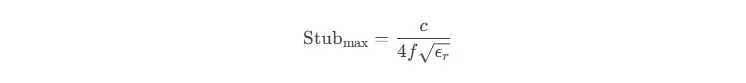

3. DDR5 Design Reglas de oro: Fórmulas y cadenas de herramientas

3.1 A través de la limitación de stub:Para DDR5-6400 (F = 3.2 GHz) en FR4: Talónmáximo≤14.7 mm.

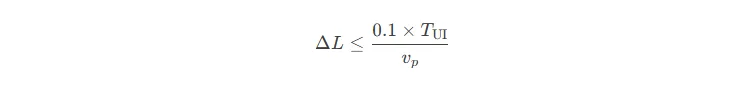

3.2 Tolerancia diferencial de pares:

Con tUi= 0.3125 ns y Vpag= 6 pulgadas/: Δl≤1.9 mil.

3.3 Objetivo de impedancia PDN:

Para ondas de 50 mv y corriente transitoria 10A: Zobjetivo≤5 MΩ.

4. Reingeniería de procesos de diseño de PCB: De prueba y error a simulación impulsado

4.1 Planificación de topología:

-

VIAS modelo en HFSS; optimizar las dimensiones de antipad.

-

Extracto de la impedancia de pila a través de siwave; construir bibliotecas s-parámetros.

4.2 Ejecución de enrutamiento:

-

Habilitar los controles de impedancia en tiempo real en Allegro; Violaciones de flota automática.

-

Implementar la topología de Fly-by con una inclinación intragrupal de ≤2 mil.

4.3 Validación:

-

Realizar pruebas de diagrama de ojos (Anuncios de teclas) con ≥70 mv altura del ojo.

-

Medir las curvas TDR; limitar la variación de impedancia a ± 5%.

Conclusión: El “De tres cuerpos” Ley del diseño DDR5

Bajo GHz-velocidad, Montículo nuic, y limitaciones de micrones, El diseño de PCB DDR5 entra en un “mecánica cuántica” era. La victoria en la guerra de la integridad de la señal exige la convergencia de la ciencia material (Sustratos de DK bajo), procesos avanzados (MSAP), y dominio de simulación.

UGPCB LOGO

UGPCB LOGO