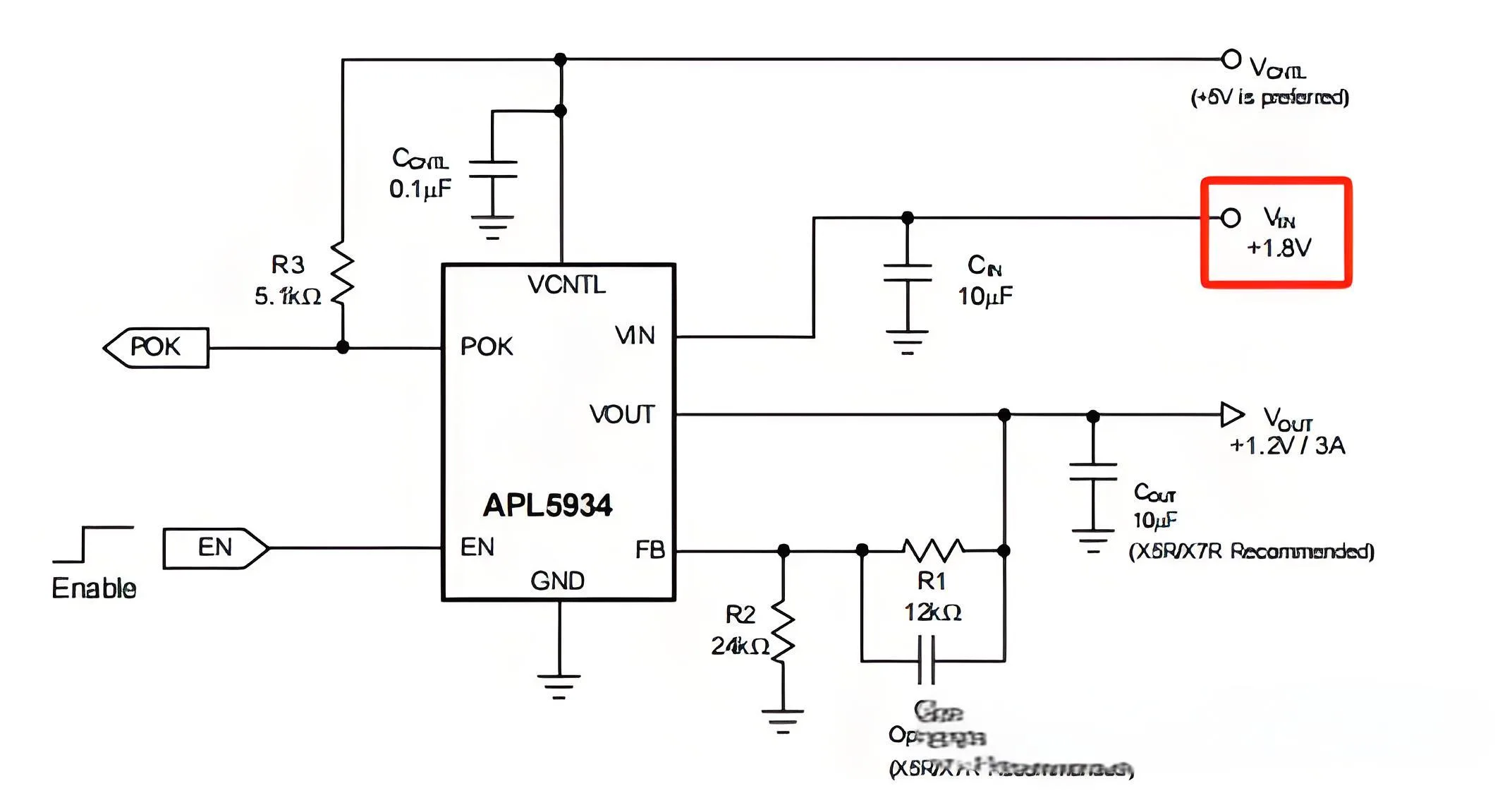

En el proceso de ensamblaje de montaje en superficie de PCBA, varios componentes electrónicos fallan a menudo. Hoy, compartimos un caso de estudio sobre el análisis de falla de un regulador lineal 3A, explicando cómo mirar más allá de la superficie e identificar rápidamente la falla.

1) Descripción de falla del chip: Vin tiene un cortocircuito a tierra..

Vin tiene un cortocircuito a tierra..

2) Análisis de fallas del dispositivo: El chip experimentó un EOS (Sobreestrés eléctrico) falla confirmada por pruebas intravenosas con Vin en cortocircuito a tierra.

La prueba intravenosa confirma el cortocircuito de Vin a tierra.

No se observaron anomalías obvias en la apariencia ni en el escaneo acústico., pero la radiografía reveló sospechas de daños por quemaduras.

Se sospecha que fue quemado

Al abrir la tapa, Se descubrió que el desgaste de EOS del chip era más severo en el pin VCNTL que en Vin..

El EOS del chip se ha quemado

El EOS del chip se ha quemado

3) Análisis de causa raíz: Se sospecha que el estrés por sobretensión introducido por VCNTL causó la falla del chip.. El pin VCNTL se define como un pin de entrada., que potencialmente podría experimentar estrés por sobretensión.

VCNTL introduce una tensión eléctrica excesiva que conduce a fallos

Un análisis más detallado reveló que la morfología del metal a lo largo del enlace VCNTL-VIN parecía derretida., y medir el IV entre VCNTL y VIN mostró un cortocircuito. Por lo tanto, el chip falló debido a un estrés de sobretensión introducido por VCNTL. El análisis del diagrama de bloques lógicos del chip relacionó el fenómeno de falla con su función lógica.

Diagrama lógico del chip

La eliminación de la capa superior de metal aclaró que la falla del chip fue causada por una sobretensión introducida por VCNTL..

VCNTL introduce una tensión eléctrica excesiva que conduce a fallos.

VCNTL introduce una tensión eléctrica excesiva que conduce a fallos.

4) Confirmación a nivel de tablero: Después del análisis, Se confirmó que el daño a otros dispositivos periféricos en la placa provocó que la tensión de voltaje en el pin VCNTL excediera su valor de especificación.. Por eso, this chip was a “victim.”

EOS es el fenómeno más común encontrado en el análisis de fallas.. Identificar la causa raíz a través de los síntomas de falla de EOS es un desafío y requiere que los analistas tengan un pensamiento lógico claro y un amplio conocimiento..