Dominar el control de impedancia de PCB: Estrategias avanzadas para el diseño de circuitos de alta velocidad

Cifra 1: Trazas críticas controladas por impedancia en el diseño de PCB multicapa

El papel crítico del control de la impedancia en la electrónica moderna

Por qué los asuntos de coincidencia de impedancia en diseños de alta frecuencia

En sistemas digitales de alta velocidad que funcionan arriba 1 GHz, tarjeta de circuito impreso Las trazas se transforman de conductores simples a líneas de transmisión complejas donde la impedancia característica (Z₀) se vuelve primordial. Cuando se producen desajustes z₀ entre componentes, Los reflejos de la señal pueden alcanzar 35% de poder incidente, causando la distorsión de la forma de onda y los errores de tiempo que paralizan el rendimiento del sistema.

Consecuencias clave del mal control de impedancia:

- Degradación de la integridad de la señal: La degradación del tiempo de elevación hasta 40% En interfaces DDR4

- Espigas de radiación emi: Las líneas no coincidentes pueden aumentar las emisiones radiadas en 15-20 dB

- Problemas de integridad de poder: Las discontinuidades de la ruta de retorno crean rebote de tierra

Conceptos de impedancia fundamental

Fórmula de impedancia característica para microstrip:

Z₀ = frac{87}{\sqrt{E_R + 1.41}} \ln izquierda(\FRAC{5.98h}{0.8W. + t}\bien)

Dónde:

- ε_r = constante dieléctrica (FR4: 4.2-4.7, Rogers 4350b: 3.48)

- H = grosor dieléctrico (milímetros)

- W = ancho de rastreo (milímetros)

- T = grosor de cobre (onz)

Cálculo de pares diferenciales:

Z_{diferencia} = 2z₀ izquierda(1 - 0.48e^{-0.96S/H}\bien)

S = espaciado de par, H = altura dieléctrica

Cinco pilares de ingeniería de impedancia de PCB

1. Matriz de selección de materiales

| Tipo de material | ε_r @10ghz | Pérdida tangente | Índice de costos |

|---|---|---|---|

| FR-4 | 4.5 | 0.02 | $ |

| Rogers 4350b | 3.48 | 0.0037 | $$$ |

| Isla I -RA | 3.45 | 0.0031 | $$$$ |

| Compuesto ptfe | 2.2-3.0 | 0.0009 | $$$$$ |

Mesa 1: Comparación de laminado de alta frecuencia

2. Principios de arquitectura de pila

Apilamiento HDI óptimo de 12 capas para señales de 25 Gbps:

- L1: Señal (0.5onz)

- L2: Suelo

- L3: Señal (3.5Mil dieléctrico)

- L4: Fuerza

- L5: Señal (De alta velocidad)

- L6: Suelo

… Reflejar estructura simétrica

Parámetros críticos:

- Tolerancia al espesor dieléctrico: ± 10% máximo

- Aspereza de cobre: <2μm rms para >10GHz

- Laminación secuencial para la continuidad de la impedancia

3. Metodologías de cálculo avanzado

Proceso de validación de impedancia de tres pasos:

- Estimación inicial:

Usar fórmula empírica:W pid frac{100h}{\sqrt{E_R}} \patio (\texto{50Ω microstrip}) - Simulación de precisión:

- Polar SI9000 para estructuras de múltiples capas

- Rogers MWI-2017 para líneas de RF/microondas

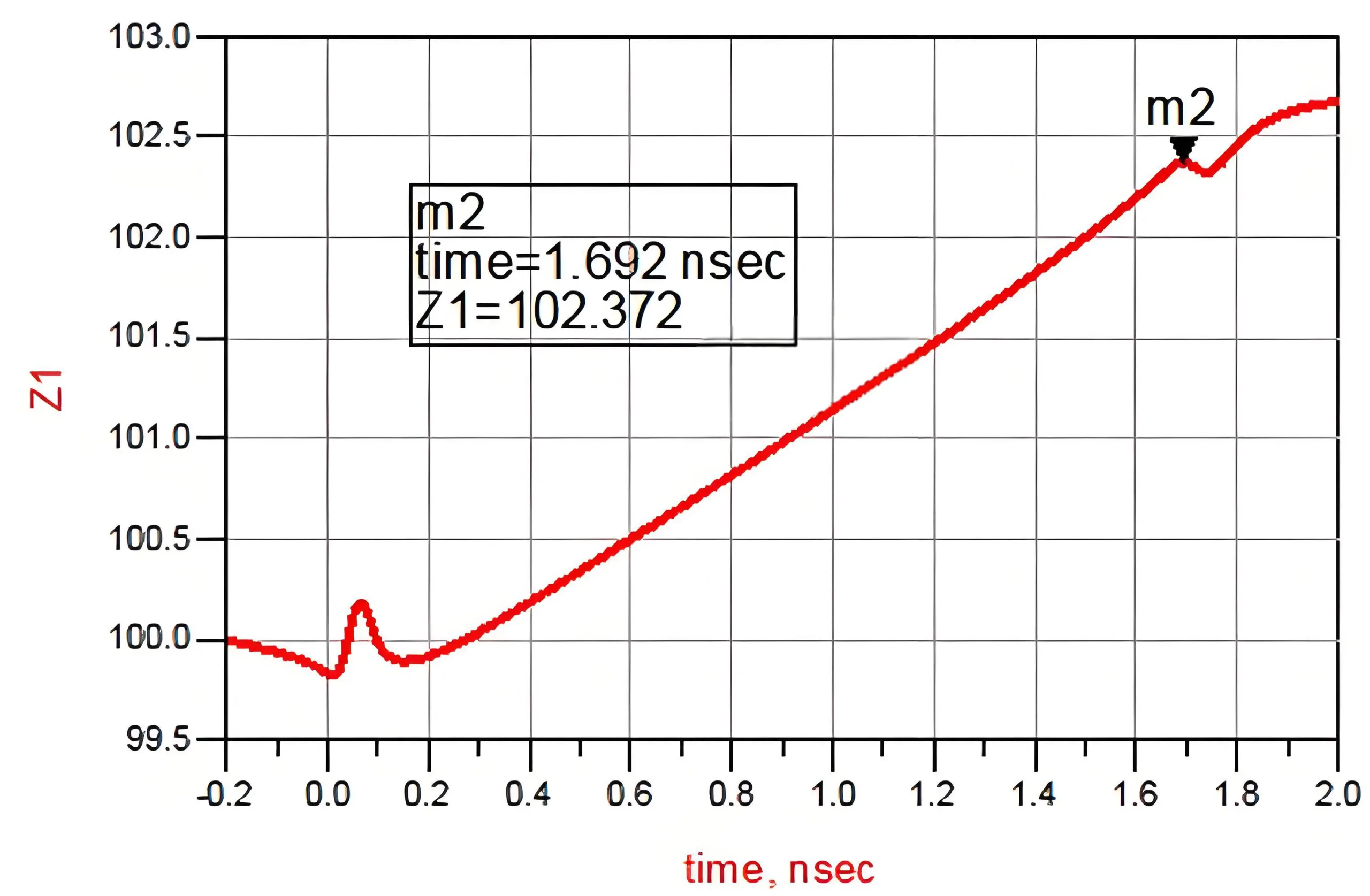

- Verificación de postproducción:

TDR Medidas con <5% tolerancia

4. Controles del proceso de fabricación

Factores de tolerancia crítica:

| Parámetro | Tolerancia típica | Impacto en Z₀ |

|---|---|---|

| Ancho de grabado | ± 0.5mil | ± 3Ω |

| Espesor dieléctrico | ± 10% | ± 8Ω |

| Peso de cobre | 0.2oz | ± 2Ω |

| Soldermasta | 0.3-0.5mil | ± 1.5o |

Datos de los estándares IPC-2141A

Estrategias de mitigación:

- Use obras de arte compensadas (0.75× factor de grabado)

- Implementar inspección óptica automatizada (AOI)

- Especificar cupones de prueba de impedancia controlada

5. Ecosistema de herramientas de vanguardia

Soluciones de software líderes en la industria:

- Polar Instruments Si9000E

- 2D solucionador de campo con 47 modelos de línea de transmisión

- Procesamiento por lotes para diseños complejos

- Rogers MWI-2017

- Especializado para diseños de microondas de hasta 110 GHz

- Base de datos de material integrada con 50+ sustratos

- Cadencia Sigrity Aurora

- 3D Em Simulación con <2% margen de error

- Verificación de cumplimiento DDR5/PCIE6.0

- Perfilador de impedancia de altium

- Visualización de impedancia en tiempo real

- Validación automatizada de apilamiento

Pautas de diseño prácticas para ingenieros

Reglas de oro para diseños de primer tiempo derecho

- 3W Regla para el control de la diafonía:

S ≥ 3 × W Quad (\texto{Donde s = espaciado de traza}) - Prioridades de coincidencia de longitud:

- Parejas diferenciales: <5MIL MISMATRA INTRA-PAIR

- Señales de autobús: <100PS Delay Sesgo

- A través de técnicas de optimización:

- Use un diámetro de 8-12mil para señales de 10 Gbps

- Fondo <15% de tiempo de ascenso

- Estrategias de terminación:

Tipo Solicitud Costo de energía Serie 22Ω Fin de la fuente Bajo Paralelo 50Ω Punto final Alto AC capacitivo Interfaces de memoria DDR Medio

Tendencias futuras en la gestión de la impedancia

Impacto en las tecnologías emergentes

- 5G MMWAVE Desafíos:

- 28/39Las bandas de GHz requieren tolerancia de ± 1Ω

- Ablación láser para control de ancho de línea de 2 μm

- Integración de empaque avanzada:

- 3D ic con coincidencia de impedancia de tsv

- Sustrato híbrido Diseños de PCB-Flex

- Optimización de impedancia impulsada por la IA:

- Redes neuronales que predicen variaciones de fabricación

- Diseño generativo para soluciones de múltiples restricciones

Tomar medidas para obtener una cotización

UGPCB Tiene una posición de liderazgo en ambos PCB (Placa de circuito impreso) y PCBA (Conjunto de placa de circuito impreso) sectores, convirtiéndolo en un líder de la industria. UGPCB cuenta con un equipo de diseño de PCB altamente experimentado que se destaca en el control de impedancia de PCB, clasificación a la vanguardia de la industria. Si tiene alguna pregunta o requisito de diseño relacionado con la impedancia de PCB, Póngase en contacto con nuestro personal técnico profesional para obtener soporte técnico o para tomar medidas y solicitar una cotización competitiva hoy.