Disposition des circuits imprimés: Le champ de bataille critique pour les performances du système électronique

La disposition PCB transcende la connectivité du circuit physique, déterminant fondamentalement l'intégrité du signal, Performance EMC, et la rentabilité. UGPCB Données confirme: Les dispositions optimisées réduisent le rayonnement EMI par 30% (IEC 61000-4-2 conforme) et augmenter l'efficacité énergétique par 22%. Pour des signaux dépassant les 5 Gbit / s, La tolérance à l'impédance doit être contrôlée dans ± 5% (Formule: Z₀ = √(L/C)), exigeant une conception de pile de PCB rigoureuse et une sélection de matériaux.

7 Technologies de base: Méthodologie de mise en page de l'UGPCB

-

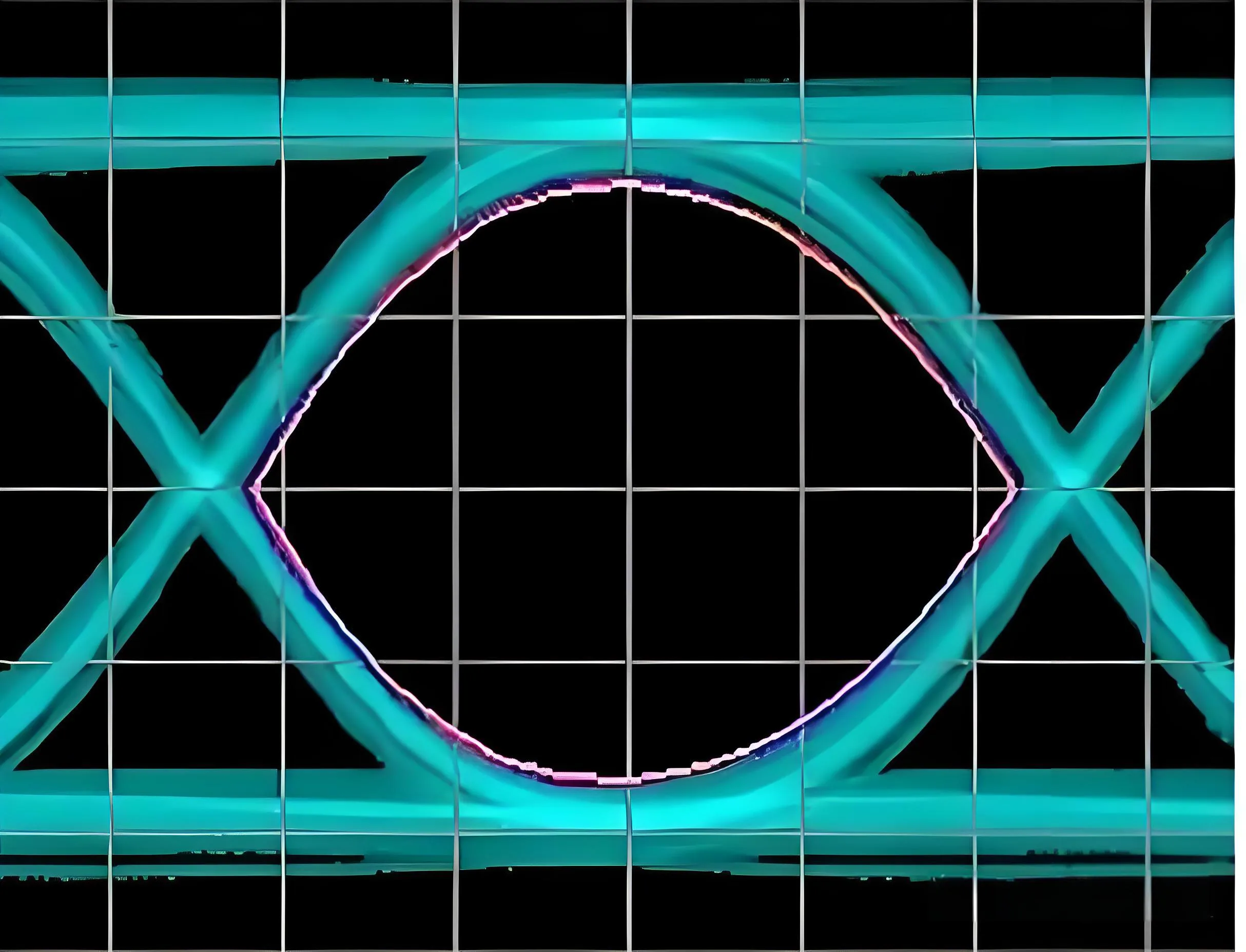

Manipulation du signal à grande vitesse (1.5-28Gbit/s)

-

Correspondance de longueur de paire différentielle: ± 5mil précision

-

Contrôle des pertes: Est tombé 6 substrat (Ne sait pas= 3,7, Df= 0,002) pour 28 Gbit / s signaux

-

-

Innovation de l'intégrité du pouvoir

Impédance PDN optimisée via la simulation 3D EM:Formule d'impédance cible: Z_target = (V × Ripple%) / (I × 50%)

Étude de cas: Solution de puissance du noyau GPU a réduit la fluctuation de tension de 120 mV à 35 mV

-

Stratégie de partitionnement de signal mixte

-

Espacement numérique / analogique: ≥8 × épaisseur de planche

-

Solutions automobiles: Placement des composants AEC-Q100 avec ISO 26262 certification

-

Solutions de point de douleur de l'industrie

Défis de conception de l'IDH dans l'électronique grand public

| Défi | Solution UGPCB | Résultat |

|---|---|---|

| 0.2MM Microvia Fill | Forage laser + placage d'impulsion | 99% taux de rendement |

| 5G Interférence Wi-Fi | 3D conception de blindage | 40% basse |

Réussite: 48-Conception de la carte mère du serveur de couche

-

Spécifications clés:

-

Couches de signalisation: 32

-

Paires différentielles: 287 sets

-

Contrôle de synchronisation: ± 12ps

-

-

Résultat démontré:

*”PCIe 4.0 la perte de signal réduite de -8,2 dB à -5,3 dB, accélérer la production de masse par 11 weeks”*

- Témoignage client HPC

Pourquoi choisir les services de mise en page de l'UGPCB?

-

Équipe d'experts: Ingénieurs avec 10+ years’ experience averaging 800+ conceptions à grande vitesse

-

Support de bout en bout:

-

Conception schématique → SIMULATION SI / PI → Optimisation de mise en page → Validation DFM → CO-CO-MODIER PCBA

-

-

Contrôle des coûts: 15% Économies de matériaux grâce à une planification optimale de couches