Mastering PCB Impedance Control: Stratégies avancées pour la conception de circuits à grande vitesse

Chiffre 1: Traces critiques à impédance dans la conception de PCB multicouche

Le rôle critique du contrôle de l'impédance dans l'électronique moderne

Pourquoi la correspondance d'impédance est importante dans les conceptions à haute fréquence

Dans les systèmes numériques à haut débit fonctionnant ci-dessus 1 GHz, PCB Les traces se transforment des conducteurs simples à des lignes de transmission complexes où l'impédance caractéristique (Z₀) devient primordial. Lorsque des décalages z₀ se produisent entre les composants, Les réflexions du signal peuvent atteindre 35% de pouvoir incident, provoquant des erreurs de distorsion et de synchronisation de la forme d'onde qui paralysent les performances du système.

Conséquences clés d'un mauvais contrôle d'impédance:

- Dégradation de l'intégrité du signal: Rise de dégradation du temps jusqu'à 40% Dans les interfaces DDR4

- Pics de rayonnement EMI: Les lignes incompatibles peuvent augmenter les émissions rayonnées de 15 à 20 dB

- Problèmes d'intégrité de l'énergie: Les discontinuités du chemin de retour créent un rebond au sol

Concepts d'impédance fondamentale

Formule d'impédance caractéristique pour microruban:

Z₀ = frac{87}{\sqrt{e_r + 1.41}} \ln gauche(\fracter{5.98H}{0.8W + T}\droite)

Où:

- ε_r = constante diélectrique (FR4: 4.2-4.7, Rogers 4350b: 3.48)

- H = épaisseur diélectrique (mm)

- W = largeur de trace (mm)

- T = épaisseur de cuivre (once)

Calcul de la paire différentielle:

Z_{difficulté} = 2z₀ gauche(1 - 0.48e ^{-0.96S / h}\droite)

S = espacement des paires, H = hauteur diélectrique

Cinq piliers d'ingénierie d'impédance PCB

1. Matrice de sélection de matériaux

| Type de matériau | ε_r @ 10GHz | Perte tangente | Indice des coûts |

|---|---|---|---|

| FR-4 | 4.5 | 0.02 | $ |

| Rogers 4350b | 3.48 | 0.0037 | $$$ |

| I -RA ISLAND | 3.45 | 0.0031 | $$$$ |

| PTFE Composite | 2.2-3.0 | 0.0009 | $$$$$ |

Tableau 1: Comparaison des stratifiés à haute fréquence

2. Principes d'architecture d'empilement

Stackup HDI optimal à 12 couches pour les signaux de 25 Gops:

- L1: Signal (0.5once)

- L2: Sol

- L3: Signal (3.5mil diélectrique)

- L4: Pouvoir

- L5: Signal (Grande vitesse)

- L6: Sol

… Structure symétrique miroir

Paramètres critiques:

- Tolérance à l'épaisseur diélectrique: ± 10% maximum

- Rugosité en cuivre: <2μm RMS pour >10GHz

- Laminage séquentiel pour la continuité de l'impédance

3. Méthodologies de calcul avancées

Processus de validation d'impédance en trois étapes:

- Estimation initiale:

Utilisez une formule empirique:W pid frac{100H}{\sqrt{e_r}} \quadruple (\texte{50Ω microrubanque}) - Simulation de précision:

- Polar SI9000 pour les structures multicouches

- Rogers MWI-2017 pour les lignes RF / micro-ondes

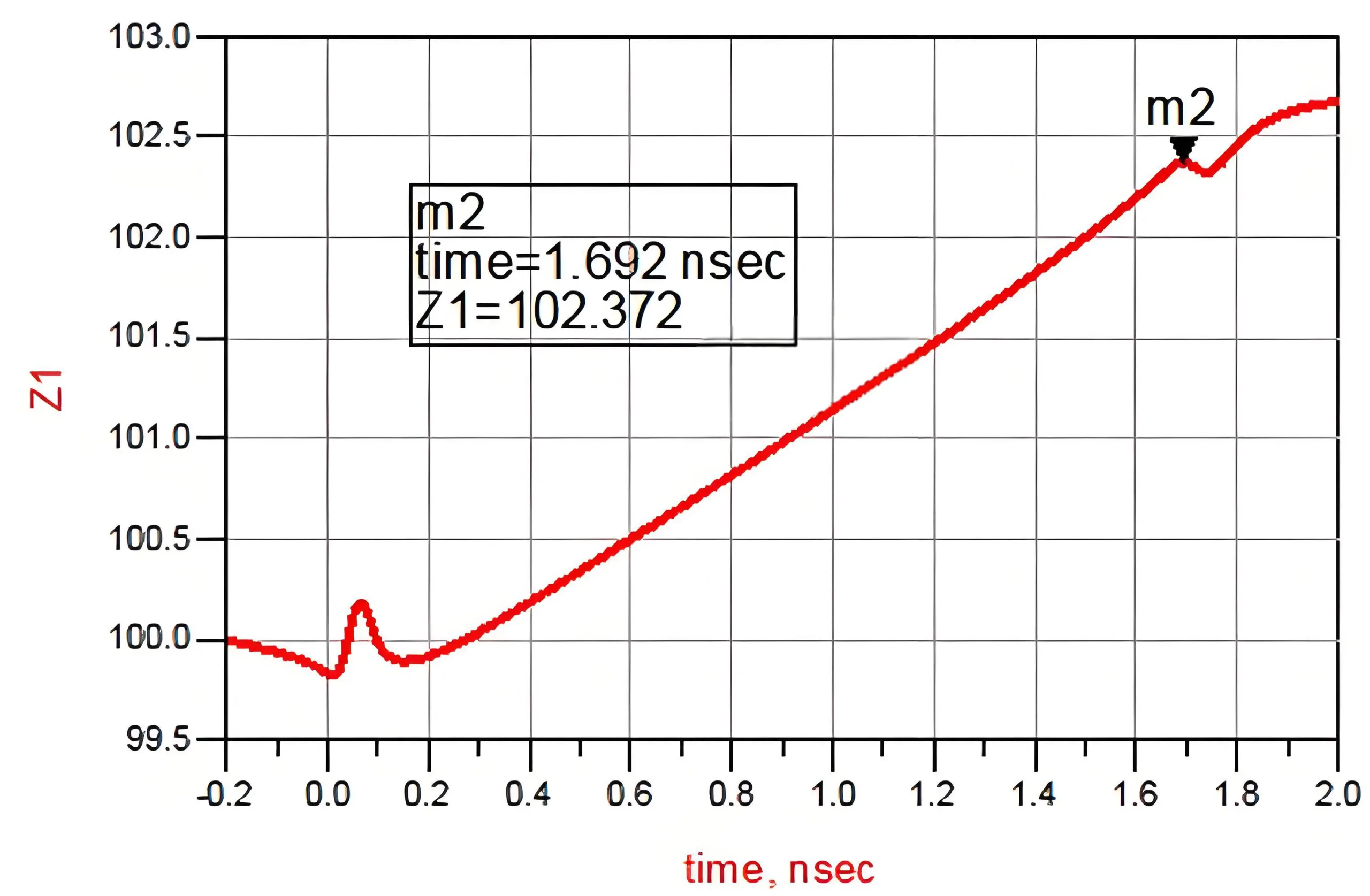

- Vérification post-production:

Mesures TDR avec <5% tolérance

4. Contrôles de processus de fabrication

Facteurs de tolérance critiques:

| Paramètre | Tolérance typique | Impact sur Z₀ |

|---|---|---|

| Largeur de gravure | ± 0,5mil | ± 3Ω |

| Épaisseur diélectrique | ± 10% | ± 8Ω |

| Poids en cuivre | 0,2 oz | ± 2Ω |

| Masque de soudure | 0.3-0.5mil | ± 1,5o |

Données des normes IPC-2141A

Stratégies d'atténuation:

- Utiliser des illustrations compensées (0.75× facteur de gravure)

- Implémenter une inspection optique automatisée (Zone d'intérêt)

- Spécifiez les coupons de test d'impédance contrôlée

5. Écosystème d'outils de pointe

Solutions logicielles de pointe:

- Instruments polaires SI9000E

- 2D solveur de terrain avec 47 Modèles de ligne de transmission

- Traitement par lots pour des conceptions complexes

- Rogers MWI-2017

- Spécialisé pour les conceptions micro-ondes jusqu'à 110 GHz

- Base de données de matériaux intégrés avec 50+ substrats

- Cadence Sigrity Aurora

- 3D simulation avec <2% marge d'erreur

- Vérification de la conformité DDR5 / PCIE6.0

- Prodileur d'impédance altium

- Visualisation d'impédance en temps réel

- Validation automatisée de l'empilement

Lignes directrices de conception pratiques pour les ingénieurs

Règles d'or pour les conceptions des nouveaux droits

- 3W Règle pour le contrôle de la diaphonie:

S ≥ 3 × W Quad (\texte{Où s = trace d'espacement}) - Priorités de correspondance de longueur:

- Paires différentielles: <5MIL inadéquat intra-paire

- Signaux de bus: <100ps de retard biaisé

- Via des techniques d'optimisation:

- Utilisez 8-12mil de diamètre pour les signaux de 10 Gops

- Doublage pour la longueur du talon <15% du temps de montée

- Stratégies de résiliation:

Taper Application Coût de l'énergie Série 22Ω Fin de source Faible Parallèle 50Ω Point final Haut AC capacitif Interfaces de mémoire DDR Moyen

Tendances futures de la gestion de l'impédance

Impact des technologies émergentes

- 5G mmwave défis:

- 28/39Les bandes GHz nécessitent une tolérance ± 1Ω

- Ablation laser pour un contrôle de largeur de ligne de 2 μm

- Intégration avancée des emballages:

- 3D ic avec correspondance d'impédance TSV

- Substrat hybride PCB-flex conceptions

- Optimisation d'impédance dirigée par l'IA:

- Réseaux de neurones prédisant les variations de fabrication

- Conception générative pour les solutions multi-contraintes

Prendre des mesures pour obtenir un devis

UGPCB occupe une position principale dans les deux PCB (Circuit imprimé) et PCBA (Assemblage de la carte de circuit imprimé) secteurs, En faire un leader de l'industrie. L'UGPCB possède une équipe de conception de PCB hautement expérimentée qui excelle dans le contrôle de l'impédance PCB, classement à la pointe de l'industrie. Si vous avez des questions ou des exigences de conception liées à l'impédance PCB, Veuillez contacter notre personnel technique professionnel pour un support technique ou pour prendre des mesures et demander un devis compétitif dès aujourd'hui.