Padroneggiare il controllo dell'impedenza del PCB: Strategie avanzate per la progettazione di circuiti ad alta velocità

Figura 1: Tracce critiche controllate dall'impedenza nella progettazione di PCB multistrato

Il ruolo critico del controllo dell'impedenza nell'elettronica moderna

Perché l'impedenza corrisponde ai progetti ad alta frequenza

In sistemi digitali ad alta velocità che operano sopra 1 GHz, PCB Le tracce si trasformano da semplici conduttori a linee di trasmissione complesse in cui impedenza caratteristica (Z₀) diventa fondamentale. Quando si verificano disallineamenti Z₀ tra i componenti, Le riflessioni del segnale possono raggiungere 35% di potere incidente, causando errori di distorsione della forma d'onda e tempistica che paralizzano le prestazioni del sistema.

Conseguenze chiave di scarso controllo dell'impedenza:

- Degrado dell'integrità del segnale: Rise il degrado del tempo fino a 40% Nelle interfacce DDR4

- Picchi di radiazione EMI: Le linee non corrispondenti possono aumentare le emissioni irradiate di 15-20 dB

- Problemi di integrità del potere: Le discontinuità del percorso di ritorno creano rimbalzo del terreno

Concetti di impedenza fondamentali

Formula di impedenza caratteristica per microstrip:

Z₀ = frac{87}{\sqrt{e_r + 1.41}} \ln a sinistra(\frac{5.98H}{0.8W + T}\Giusto)

Dove:

- ε_r = costante dielettrica (FR4: 4.2-4.7, Rogers 4350b: 3.48)

- H = spessore dielettrico (mm)

- W = Larghezza della traccia (mm)

- T = spessore del rame (oz)

Calcolo della coppia differenziale:

Z_{Diff} = 2Z₀ a sinistra(1 - 0.48e^{-0.96SH}\Giusto)

S = spaziatura delle coppie, H = altezza dielettrica

Cinque pilastri di ingegneria dell'impedenza del PCB

1. Matrix di selezione del materiale

| Tipo di materiale | ε_r @10ghz | Tangente perdita | Indice dei costi |

|---|---|---|---|

| FR-4 | 4.5 | 0.02 | $ |

| Rogers 4350b | 3.48 | 0.0037 | $$$ |

| Isola I-Tera | 3.45 | 0.0031 | $$$$ |

| Composito PTFE | 2.2-3.0 | 0.0009 | $$$$$ |

Tavolo 1: Confronto in laminato ad alta frequenza

2. Principi dell'architettura Stackup

Stackup HDI a 12 strati ottimale per segnali da 25 Gbps:

- L1: Segnale (0.5oz)

- L2: Terra

- L3: Segnale (3.5mil dielettrico)

- L4: Energia

- L5: Segnale (Ad alta velocità)

- L6: Terra

… Struttura simmetrica specchio

Parametri critici:

- Tolleranza di spessore dielettrico: ± 10% massimo

- Rugosità di rame: <2μM RMS per >10GHz

- Laminazione sequenziale per la continuità dell'impedenza

3. Metodologie di calcolo avanzate

Processo di validazione dell'impedenza in tre fasi:

- Stima iniziale:

Usa la formula empirica:W pid frac{100H}{\sqrt{e_r}} \Quad (\testo{50Ω microstrip}) - Simulazione di precisione:

- Polar SI9000 per strutture multistrato

- Rogers MWI-2017 per linee RF/Microonde

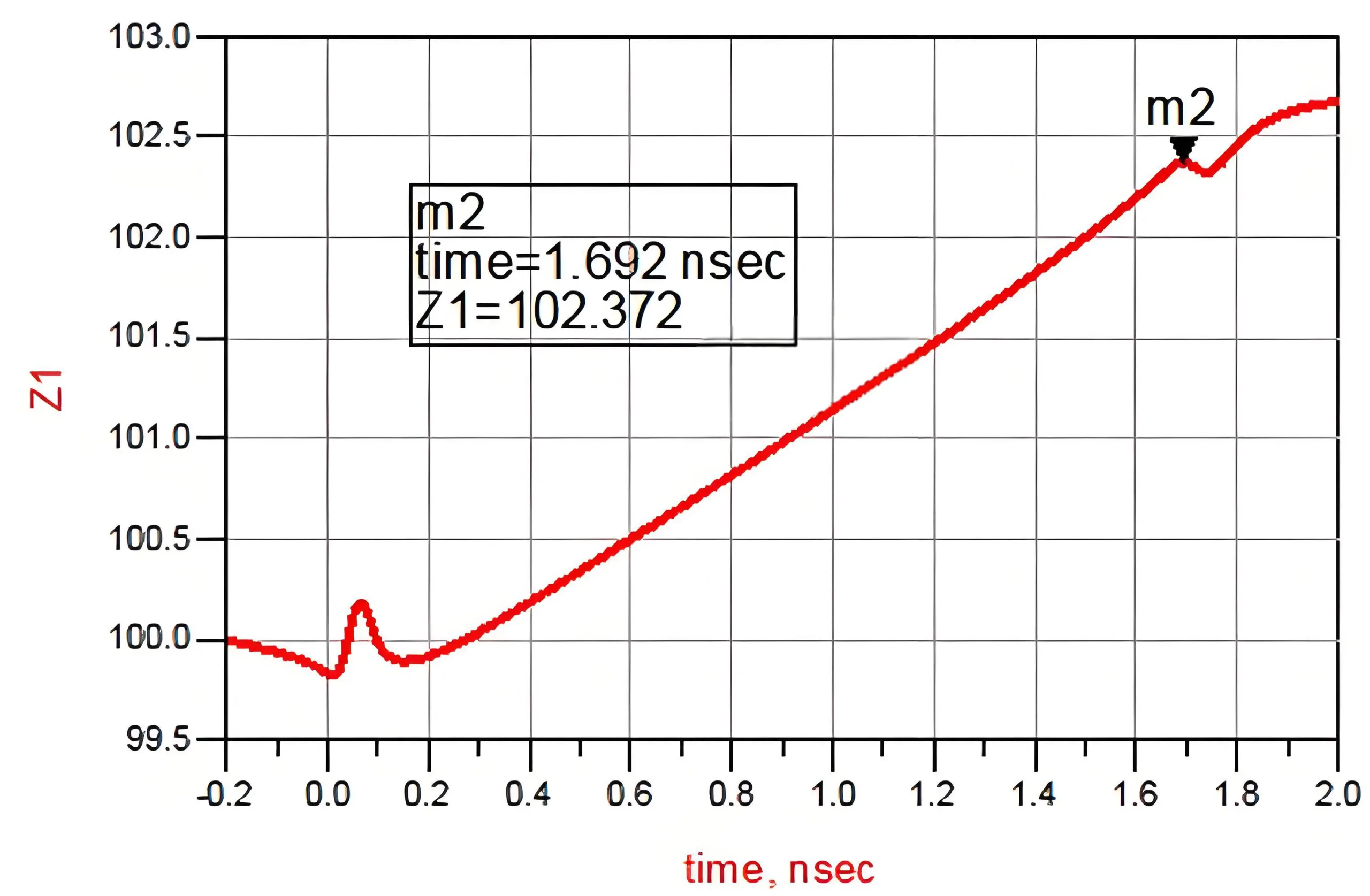

- Verifica post-produzione:

Misurazioni TDR con <5% tolleranza

4. Controlli di processo di produzione

Fattori di tolleranza critica:

| Parametro | Tolleranza tipica | Impatto su Z₀ |

|---|---|---|

| Larghezza di incisione | ± 0,5 mil | ± 3Ω |

| Spessore dielettrico | ± 10% | ± 8Ω |

| Peso di rame | 0,2 once | ± 2Ω |

| Maschera di saldatura | 0.3-0.5mil | ± 1,5o |

Dati dagli standard IPC-2141A

Strategie di mitigazione:

- Usa opere d'arte compensate (0.75× fattore di incisione)

- Implementare l'ispezione ottica automatizzata (AOI)

- Specificare i coupon di test di impedenza controllati

5. Ecosistema di strumenti all'avanguardia

Soluzioni software leader del settore:

- Strumenti polari Si9000E

- 2D Solver di campo con 47 Modelli di linea di trasmissione

- Elaborazione batch per progetti complessi

- Rogers MWI-2017

- Specializzato per disegni a microonde fino a 110 GHz

- Database di materiali integrati con 50+ substrati

- Cadence Sigrity Aurora

- 3D em simulazione con <2% margine di errore

- DDR5/PCIE6.0 Controllo della conformità

- Profiler di impedenza di Altium

- Visualizzazione dell'impedenza in tempo reale

- Convalida automatica dello stackup

Linee guida per la progettazione pratica per gli ingegneri

Regole d'oro per i progetti della prima destra

- 3W Regola per il controllo del crosstalk:

S ≥ 3 × W Quad (\testo{Dove s = tracce spaziatura}) - Priorità di corrispondenza della lunghezza:

- Coppie differenziali: <5Mil Intrap-Pair Mismatch

- Segnali di autobus: <100PS Delay Skew

- Tramite tecniche di ottimizzazione:

- Utilizzare il diametro di 8-12 mil per i segnali da 10 Gbps

- Retrodrilling per la lunghezza del mozzicone <15% di tempo di ascesa

- Strategie di terminazione:

Tipo Applicazione Costo di potenza Serie 22Ω End fonte Basso Parallelo 50Ω End-point Alto AC capacitivo Interfacce di memoria DDR Medio

Tendenze future nella gestione dell'impedenza

Le tecnologie emergenti impatto

- 5G MMWAVE Sfide:

- 28/39Le bande GHZ richiedono tolleranza ± 1Ω

- Ablazione laser per controllo della larghezza della linea 2μm

- Integrazione di imballaggi avanzati:

- 3D ic con corrispondenza dell'impedenza TSV

- Substrato ibrido Design PCB-Flex

- Ottimizzazione dell'impedenza guidata dall'IA:

- Reti neurali che prevedono variazioni di produzione

- Design generativo per soluzioni multi-vincoli

Agisci per ottenere una citazione

UGPCB Mantiene una posizione di primo piano in entrambi i PCB (Circuito stampato) e PCBA (Gruppo a circuito stampato) settori, renderlo un leader del settore. UGPCB vanta un team di progettazione PCB di grande esperienza che eccelle nel controllo dell'impedenza del PCB, classifica in prima linea nel settore. In caso di domande o requisiti di progettazione relativi all'impedenza del PCB, Si prega di contattare il nostro personale tecnico professionale per il supporto tecnico o per agire e richiedere un preventivo competitivo oggi.