半導体チップは次のように機能します “脳” デジタル時代の, チップパッケージは保護として機能します “鎧” そして “ニューラルネットワーク。” 脆弱なシリコンが死ぬことを超えて, 重要な熱管理を可能にします, 電気接続, および信号伝送. かさばる穴のパッケージから、超薄いウェーハレベルのソリューションまで, パッケージングの進化により、エレクトロニクスの小型化とパフォーマンスの向上が促進されました - 記念碑的な技術の物語.

パッケージングテクノロジーの分類

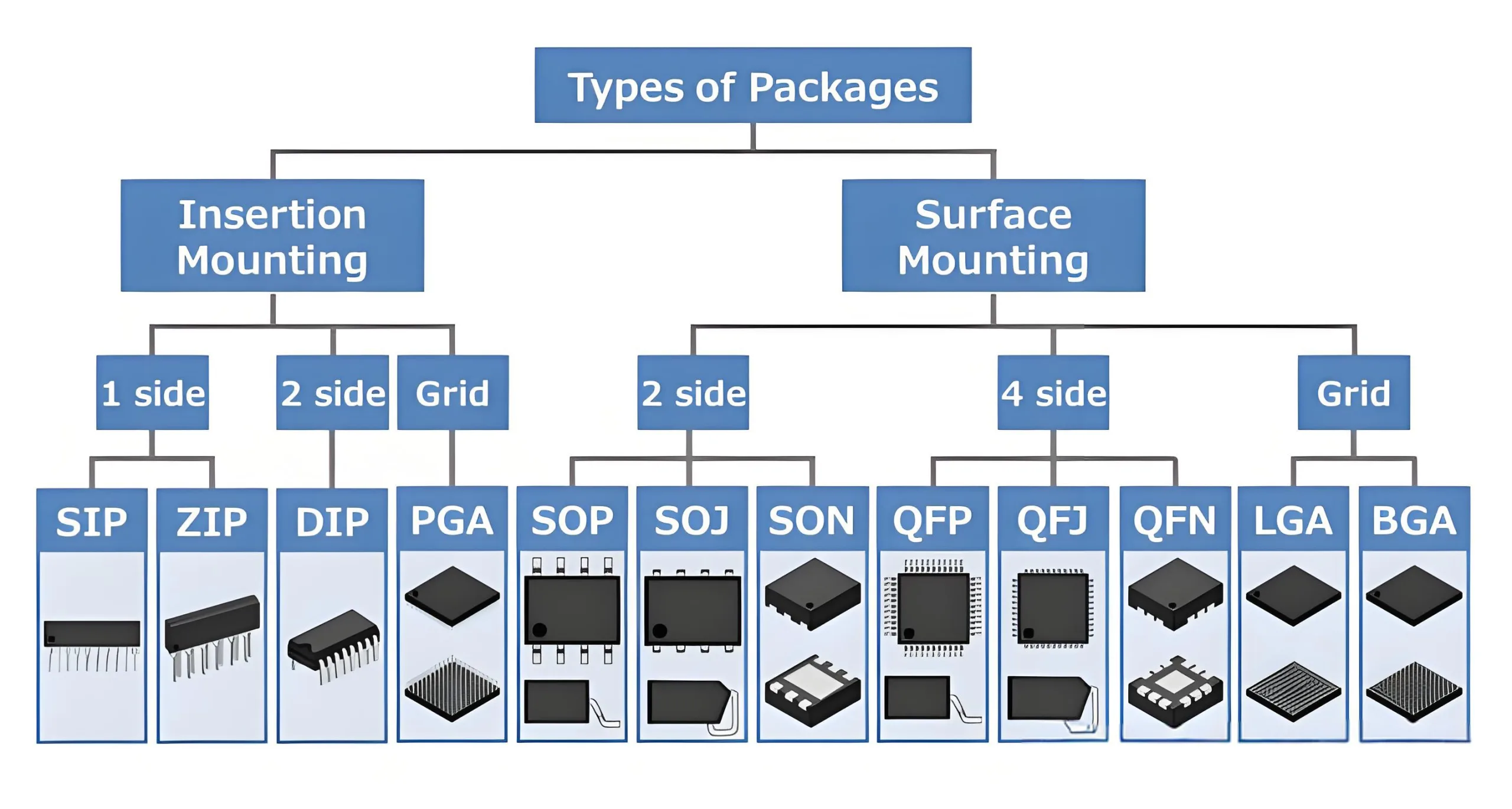

取り付け方法によって

-

スルーホールパッケージ (tht):

に挿入されたピン プリント基板 はんだ付けのためのメッキスルーホール. 早期の技術を表します. -

表面マウントテクノロジー (SMT):

PCBパッドに直接はんだ付けされたコンポーネント. より高い密度と自動アセンブリを有効にします.

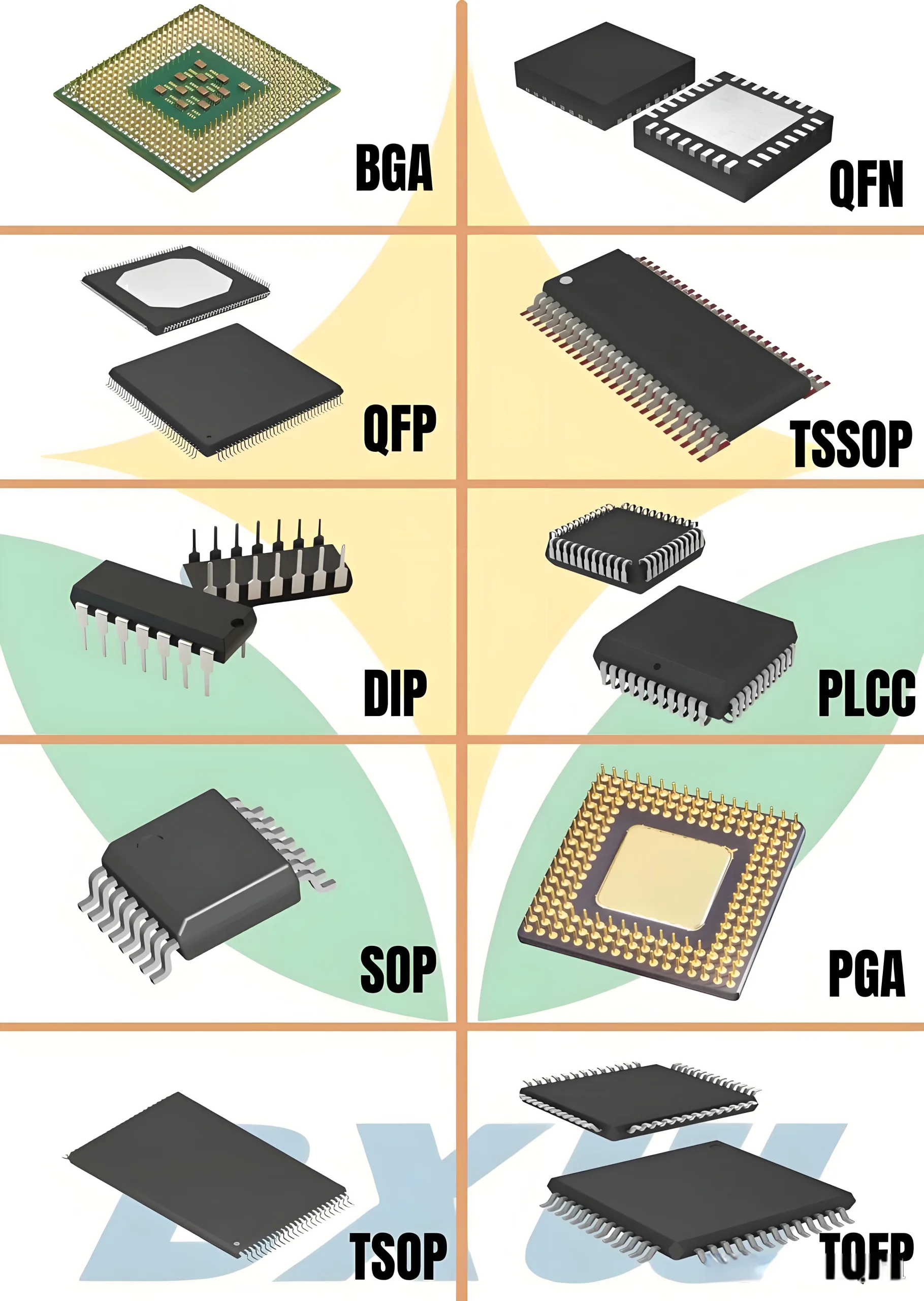

ピン構成によって (密度の進行)

単列→デュアルロー→クワッド側→エリアアレイ

スルーホール時代

do/to: 離散コンポーネントの基礎

-

DO-41ダイオード: Ø2.7mm×5.2mm

-

TO-220トランジスタ: ≤50W電源散逸を処理します

-

熱抵抗: R<サブ>そして</サブ> = (T<サブ>j</サブ> – T<サブ>a</サブ>)/p

どこ R<サブ>そして</サブ> =ジャンクション間の熱抵抗

sip/zip: シングルインラインの革新

-

一口: 3-16 ピン, 抵抗器/低電力ダイオードの費用対効果

-

ジップ: 40% Zigzag PIN配置を介したSIPよりも高いピン密度

-

アプリケーション: 初期メモリモジュール, 電圧レギュレーター

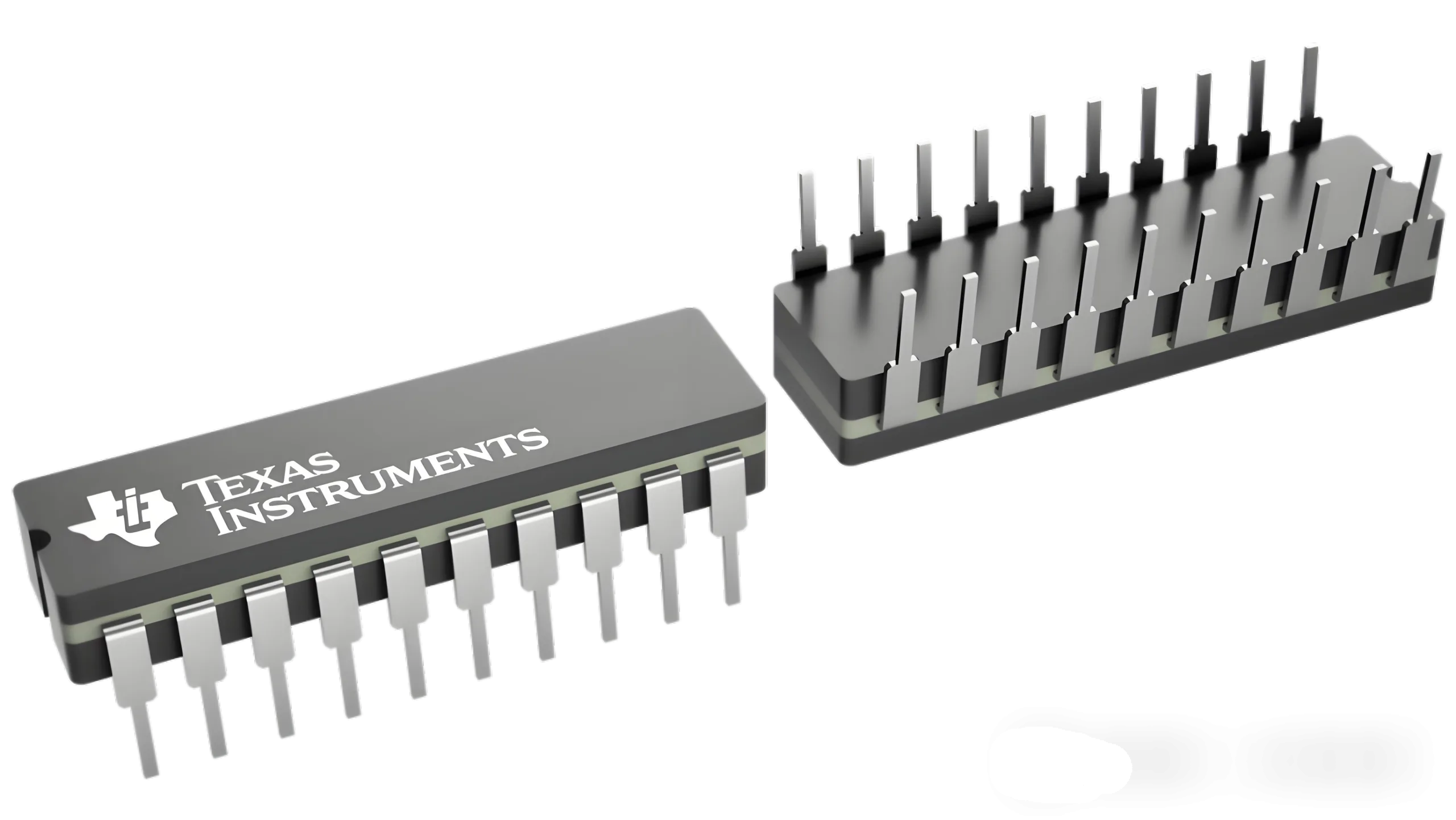

浸漬: IC革命

-

ピンピッチ: 2.54mm (0.1″) 標準

-

1980S市場シェア: >70% ICパッケージの

-

熱性能:

セラミックディップ: 20-30 w/m・k導電率

プラスチックディップ: 0.2-0.3 w/m・k

PGA: 高性能コンピューティングパイオニア

-

ピン密度: 3×ディップよりも高い

-

アプリケーション: インテル 80386/80486 CPU

-

挿入力: 30-100 ニュートン

SMT革命

SOD/SOT: 離散コンポーネントの小型化

-

SOD-323: 1.7mm×1.25mm

-

SOT-23熱抵抗: 〜250°C/W

-

リフロープロファイル: ピーク温度235-245°C

ガルウィングリード: SOPファミリー

-

ピンピッチの進化:

1.27mm (SOP) →0.8mm (SSOP) →0.65mm (tssop) -

デリバティブパッケージ:

SOP→SSOP→TSOP→TSSOP→VSSOP -

熱強化: HSSOPは熱抵抗を減らします 40%

Jリード構成: 観察

-

機械的強度: 30% より高いストレス抵抗

-

電気制限: 0.8-1.2NH寄生インダクタンス

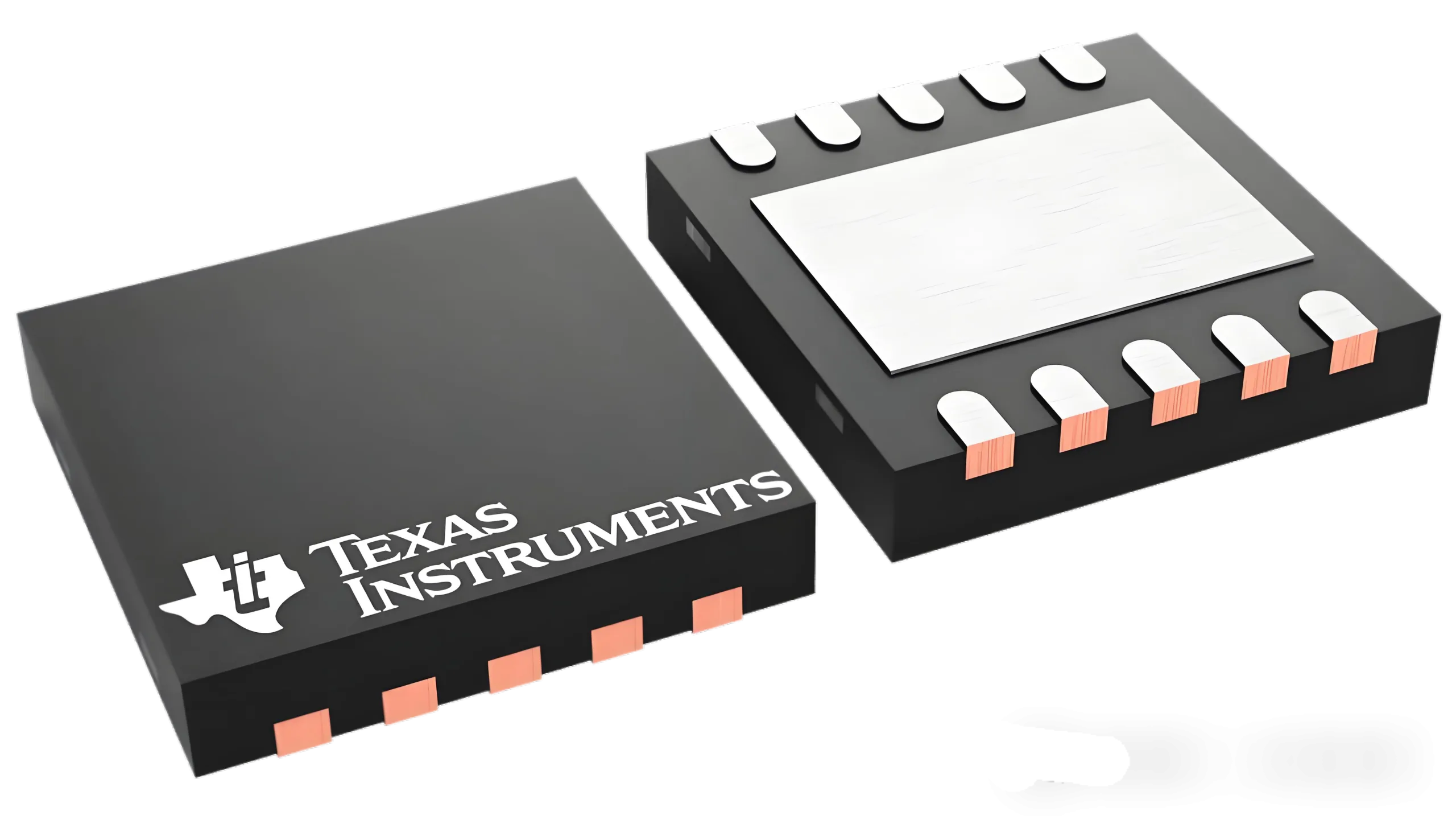

リードレスブレークスルー: 息子/dfn

-

スペース効率: >50% SOPよりも改善

-

熱性能: 15サーマルパッド付き°C/W

-

小型化制限:

x2son: 0.6mm×0.6mm×0.32mm

小型化の背後にある物理学

3つの中核的な課題は、パッケージのスケーリングを管理します:

-

熱管理:

Q =haΔt

サイズの縮小 (↓a) より高い対流係数が必要です (↑h) -

熱応力制御:

s = ertht

ここでCTE (a) 不一致はストレスを引き起こします -

信号の完全性:

鉛インダクタンス *L≈2L(ln(2L/D)-1) nh*

小型化により、インダクタンスが減少します 30%

次のフロンティア: 高度なパッケージ

X2SONが0.6mmのスケールにヒットすると, イノベーションはにシフトします:

-

3D 包装: TSV対応の垂直統合

-

不均一な統合: マルチノードダイアセンブリ

-

フォトニクス: シリコンフォトニクスの共同設計

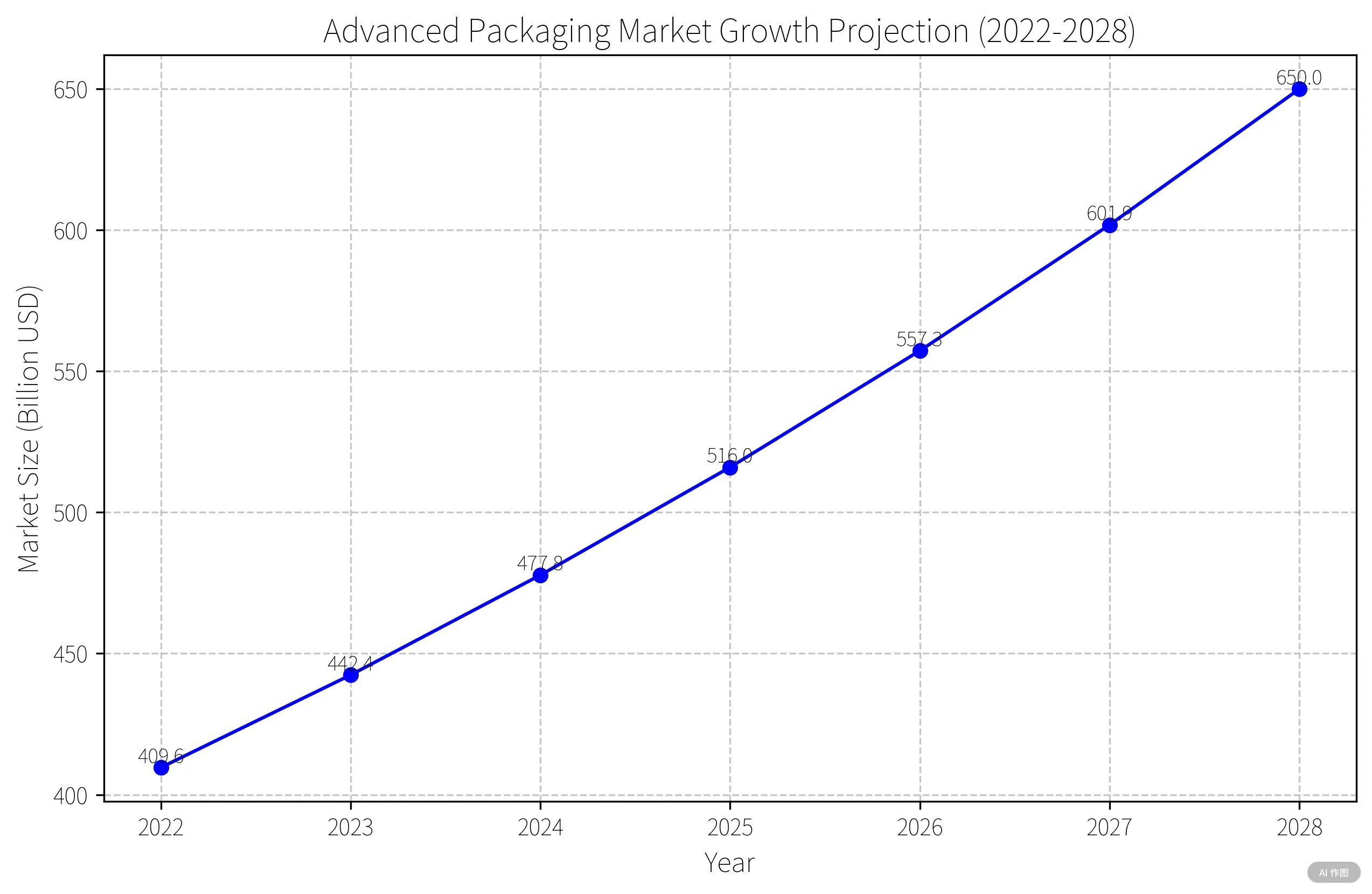

市場予測 (Yoledéveloppement):

8% CAGRを通過します 2028 →650億ドルの市場

パッケージングは今、システムのパフォーマンスを批判的に定義します - 単なる保護をはるかに超えています.

結論

DIPの2.54mmピッチからX2SONの0.6mmフットプリントまで, パッケージの進歩は、継続的に電子機器を再定義します. すべてのスリムなスマートフォンと5Gデバイスは、これらの目に見えないイノベーションに依存しています. AIと量子コンピューティングが出現します, チップパッケージは、ナノスケールの境界を押し続けます.

*次にシリーズ:

BGA/CSP/WLCSPテクノロジー

3D 包装 & TSV相互接続

高度な包装材料科学

乞うご期待!*

UGPCBのロゴ

UGPCBのロゴ