パッケージングテクノロジーのすべての顕微鏡的進歩は、エレクトロニクスの物理的境界を再形成します.

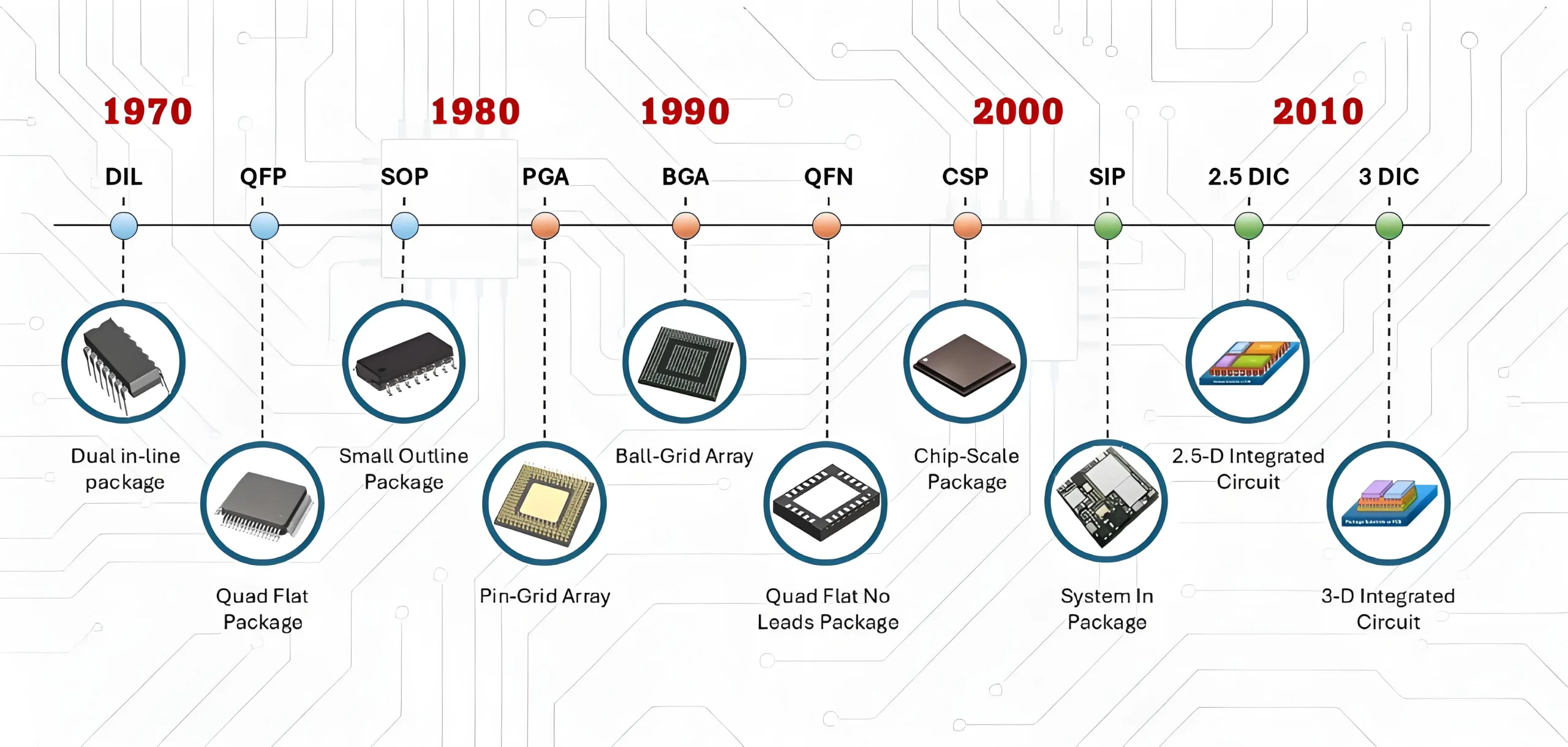

先週 チップパッケージの進化: DIPからX2SONまで - 小型化がエレクトロニクスをどのように再形成したか, スルーホールパッケージの時代を探りました (浸漬) そして、どのように表面マウントデバイス (SOP, 観察, 息子) 開始されたデバイスの小型化. これらのテクノロジーは最新のパッケージングの基礎を築きました, の 小型化革命 続けます. 今日, クワッドフラットからウェーハレベルのCSPまでの高密度パッケージを調べ、そしてそれらの影響 プリント基板設計 制限.

Quad-Flatパッケージ: 空間密度のバランス

Quad-Flatパッケージ (MF, PLCC/QFJ, QFN) 4つのパッケージエッジすべてを利用することにより、より高いI/O密度に対する重要な進化を表します.

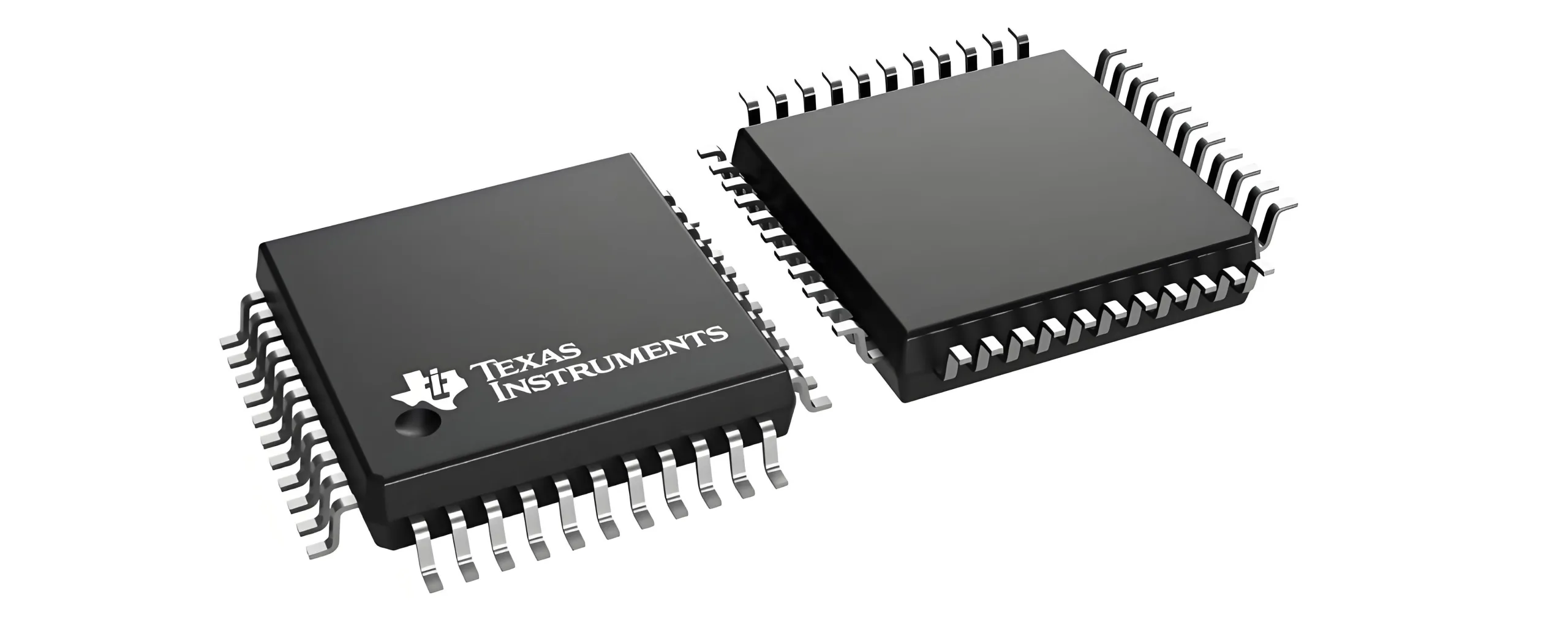

MF: カモメ層密度の先駆者

MF (クワッドフラットパッケージ) 象徴的な機能 “ガルウィング” (L字型) すべての側面から伸びるリード. その ピンピッチ (0.4mm/0.5mm/0.65mm) 指示します PCBルーティング 密度とはんだ精度.

QFPバリアント:

-

サイズ/厚さ: LQFP (控えめ), TQFP (薄い), VQFP (非常に薄い)

-

材料: PQFP (プラスチック), MQFP (金属)

-

熱強化: HQFP, HLQFP, HTQFP, HVQFP

-

保護: BQFP (バンペッド - コーナーパッドは曲がったリードを防ぎます)

熱管理は重要です. 接合部からアンビエントへの熱抵抗式 θja= (TJ -Ta)/p (どこ TJ=ジャンクション温度, 面=周囲温度, p=パワー) 熱散逸設計を管理します.

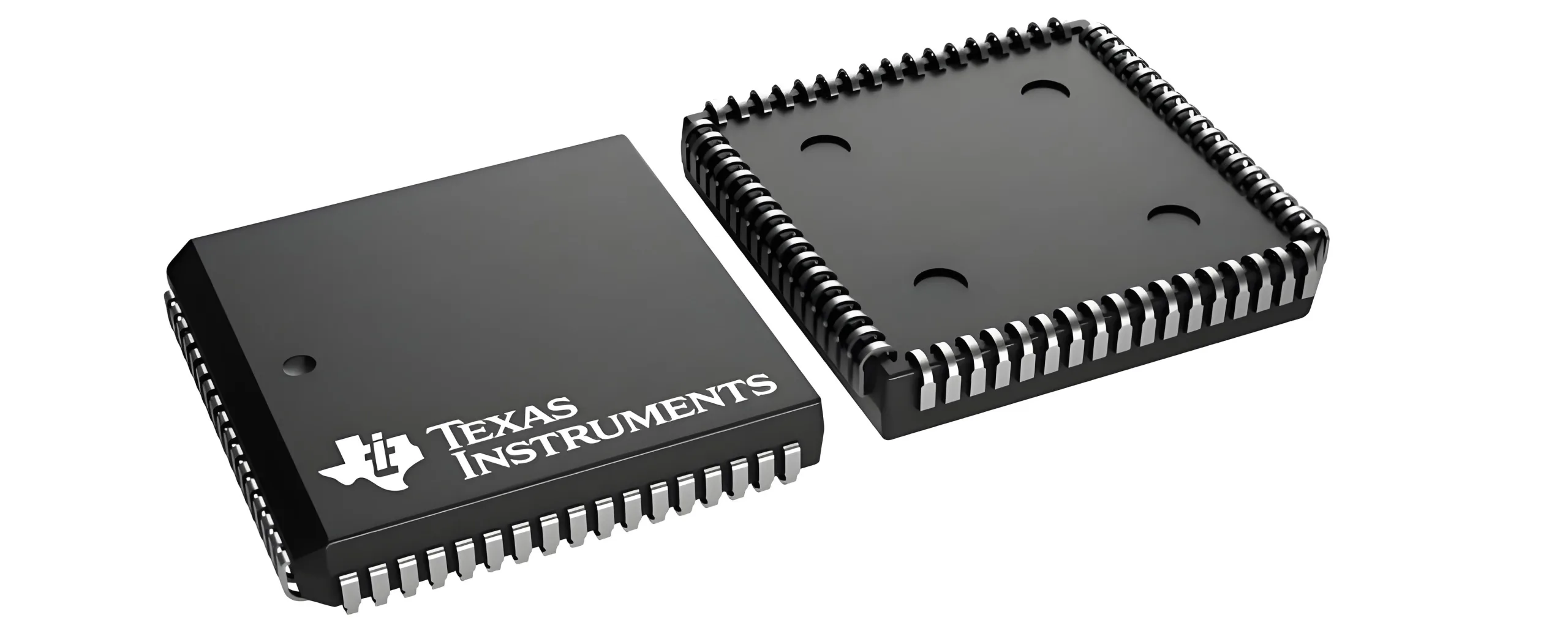

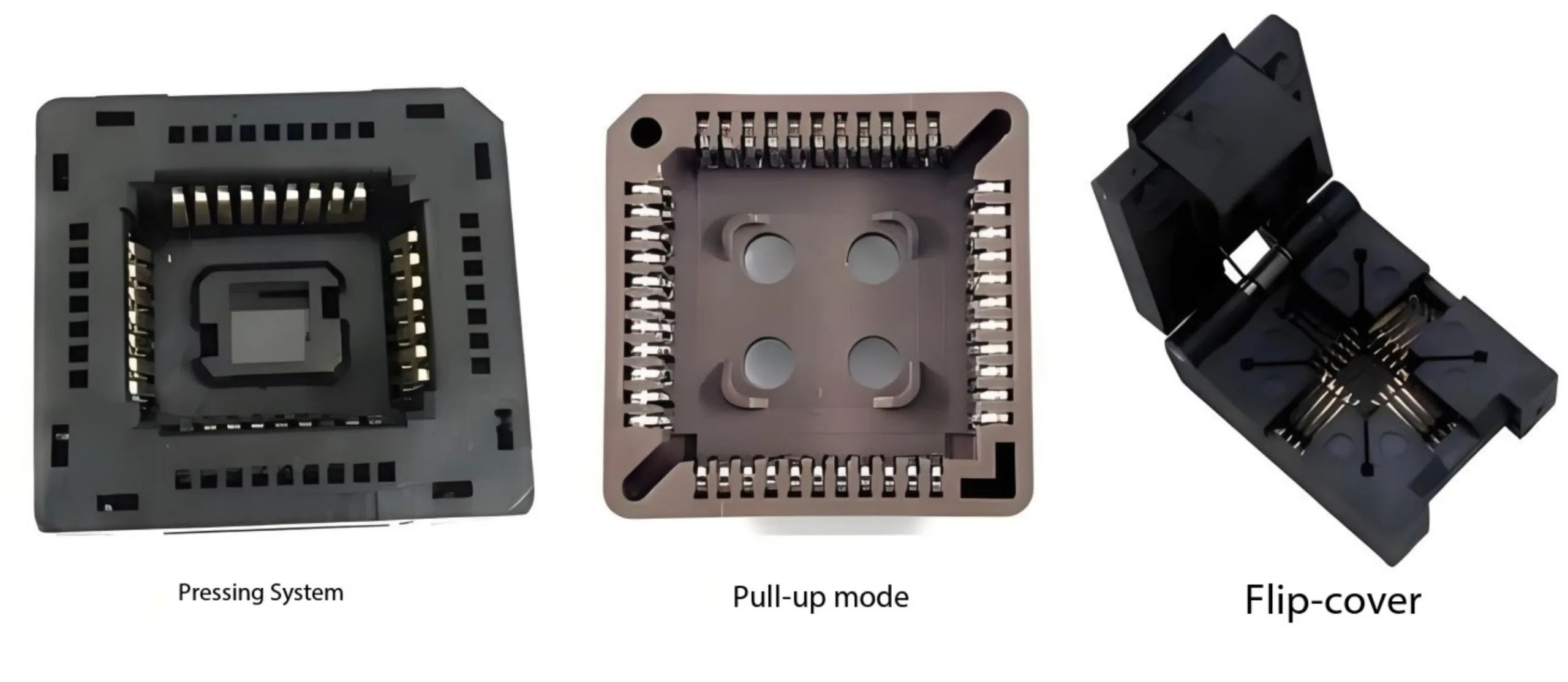

PLCC/QFJ: Jリードを介した安定性

PLCC (プラスチック鉛チップキャリア) またはQFJ (クアッドフラットJリード) 振動/熱応力に対する機械的安定性のために、下向きのJ字型リードを使用します.

標準化の利点: PLCC/QFJのユニバーサルテストソケットとの高い互換性は、生産テストを合理化します. QFJは技術的には正確ですが, “PLCC” 業界が育てたままです.

QFN: 鉛のない小型化のブレークスルー

QFN (Quad Flat No-Lead) 外部リードを排除します, 経由で接続します:

-

露出したパッド (ep): への直接サーマルパス プリント基板 銅

-

濡れた側面: サイドウォールはんだ付け可能なパッド

重要な利点:

-

ウルトラコンパクト: 40% QFPよりも小さい

-

電気的優位性: 短い経路は寄生性インダクタンスを減らします (l≈μ・l/w)

-

熱効率: 低いθja対. 同じサイズのQFP

厚さの進化: LQFN→UQFN→VQFN→WQFN→X1QFN→X2QFN. LCC (LPCC/LCCC) そのリードレスセラミック/プラスチックバリアントです.

配列パッケージ: 密度制限の革新

Quad-FlatがI/Oの制限に到達したとき, 配列パッケージ (地方自治体, BGA) 2D相互接続密度を有効にします.

地方自治体: 精密弾性接続

地方自治体 (ランドグリッドアレイ) 正確に整列した金属接点を使用します (例えば。, LGA775: 775 連絡先) ソケットピンと交尾.

コア値:

-

ソケット性: CPUのアップグレード/メンテナンス

-

低インダクタンス: 短い信号パス

-

高い信頼性: CPUに最適です (Intel/amd)

制限: 高いソケットコスト/サイズは、コンパクトなデバイスでBGAを支持します. 注記: LGAは直接SMTはんだ付けできます.

BGA: はんだボールの支配

BGA (ボールグリッドアレイ) はんだボールマトリックスを介して接続します. ボールピッチ (0.3–1.0mm; <0.2FBGAのMM) 重要です.

変革的利点:

-

高密度: >1,000 私/私たち (対. QFPの〜300)

-

宇宙節約: 30%+ 面積削減と. MF

-

電気/サーマル: 低信号遅延; ボールは熱を伝導します

-

自己調整: 表面張力エイズアセンブリ

BGAファミリー:

-

材料: PBGA (プラスチック), CBGA/CABGA (セラミック)

-

サイズ/ピッチ: NFBGA/FBGA (ファインピッチ), Tinybga, DSBGA/WCSP (ダイサイズ), LFBGA/VFBGA (薄い)

-

統合:

-

FCBGA (フリップチップ): マイクロバンプを介した直接的な原動力接続

-

ポップ (パッケージのパッケージ): 垂直スタッキング (例えば。, 論理 + メモリ)

-

PG-WF2BGA: ファンアウトウェーハレベルのパッケージ

-

課題: X線検査 (axi), 複雑なリワーク, CTEマッチング プリント基板材料.

配列パッケージの比較

| 特徴 | PGA (ピングリッドアレイ) | 地方自治体 (ランドグリッドアレイ) | BGA (ボールグリッドアレイ) |

|---|---|---|---|

| 繋がり | 剛性ピン | 平面連絡先 | はんだボール |

| 重要な強さ | ソケットの信頼性 | 密度 + ソケット可能 | 最大密度/最小サイズ |

| 信号遅延 | 最高 | 中くらい | 最低 |

| アプリケーション | レガシーCPU/産業 | デスクトップ/サーバーCPU | モバイル/GPU/SOC |

| PCBスペース | 大きい | 中くらい | コンパクト |

チップスケール & ウェーハレベルのパッケージ: 身体的な制限に近づいています

CSP: サイズの境界を再定義します

CSP (チップスケールパッケージ) キーメトリック: パッケージサイズ≤1.2×ダイサイズ (対. 2–5×従来の場合). 本質的に小型化されたBGA (FBGA/VFBGA) 細かいピッチで (0.2–0.5mm).

価値: ウェアラブル/センサーの究極の小型化.

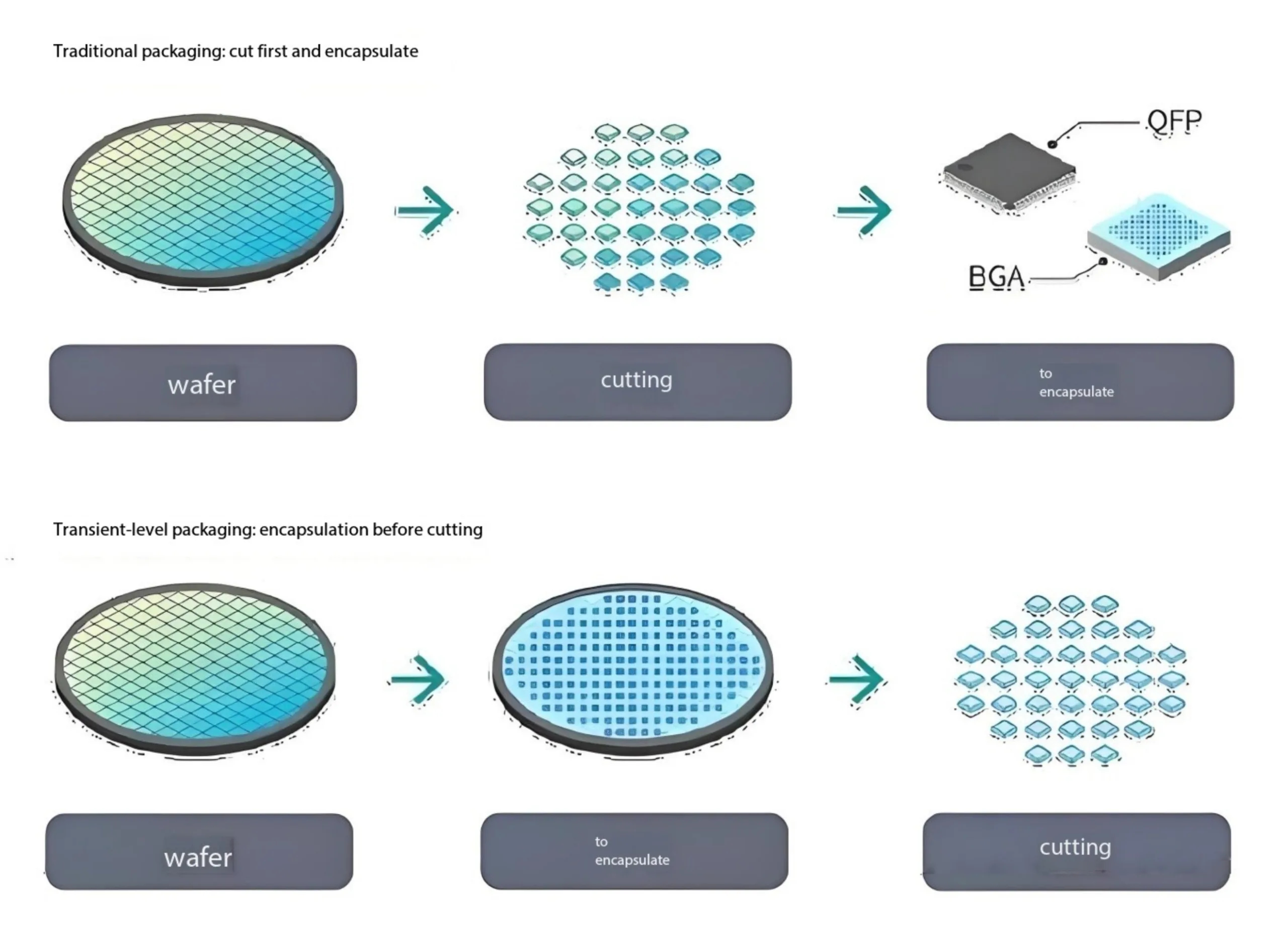

WLCSP: ウェーハレベルの革命

WLCSP/ウェーハレベルのパッケージは、すべてのステップを完了します (RDL, ボール) ダイシングの前にウェーハに.

破壊的な利点:

-

最小サイズ: ≈ダイ寸法

-

コスト削減: 30-50% 安く (基質/成形はありません)

-

ピークパフォーマンス: 最短の相互接続, 最低の寄生虫

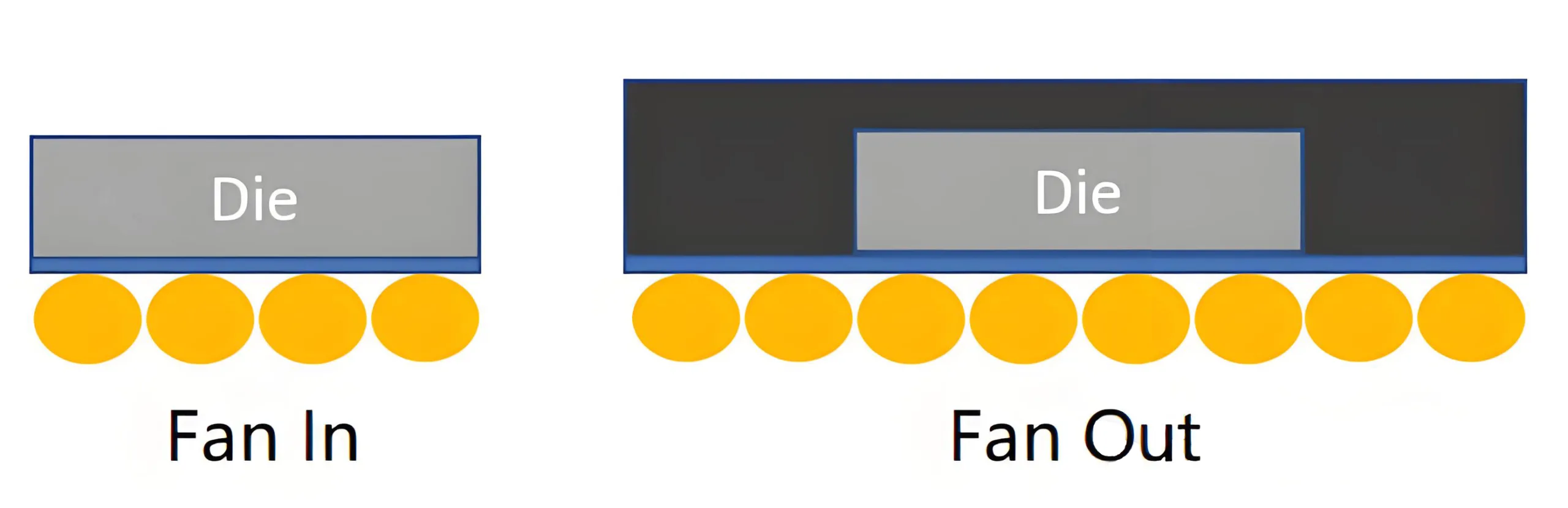

WLCSPタイプ:

-

ファンインWLCSP:

-

ダイエリア内のボール

-

パッケージサイズ=ダイサイズ

-

センサー/PMICの低コスト

-

-

ファンアウトWLCSP (例えば。, TSMC情報, Samsung fo-plp):

-

ボールはダイを超えて伸びています

-

パッケージサイズ > ダイサイズ

-

より高いI/O密度, マルチチップ統合

-

プレミアムSOCS/RFモジュール用

-

ビジュアルID: カプセル化されていないシリコン (対. 樹脂成形DFN).

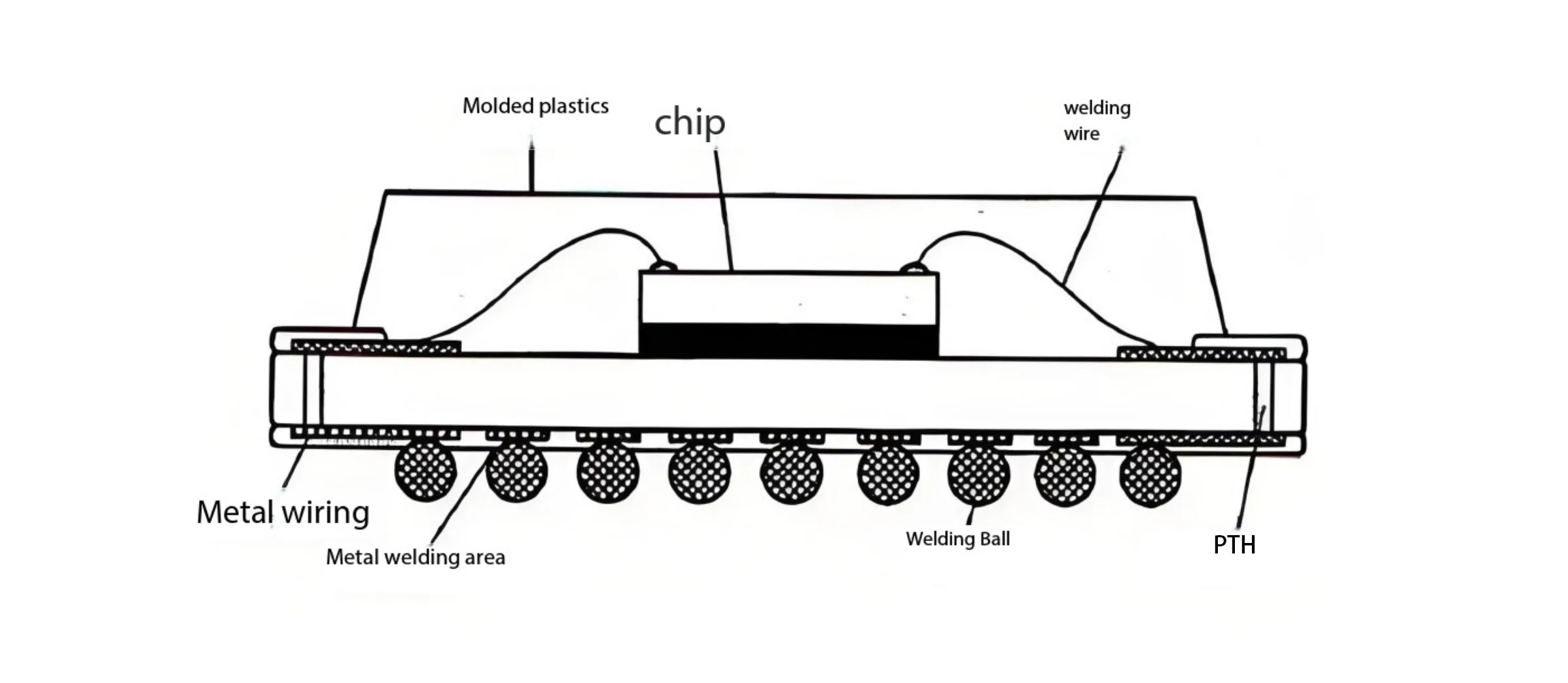

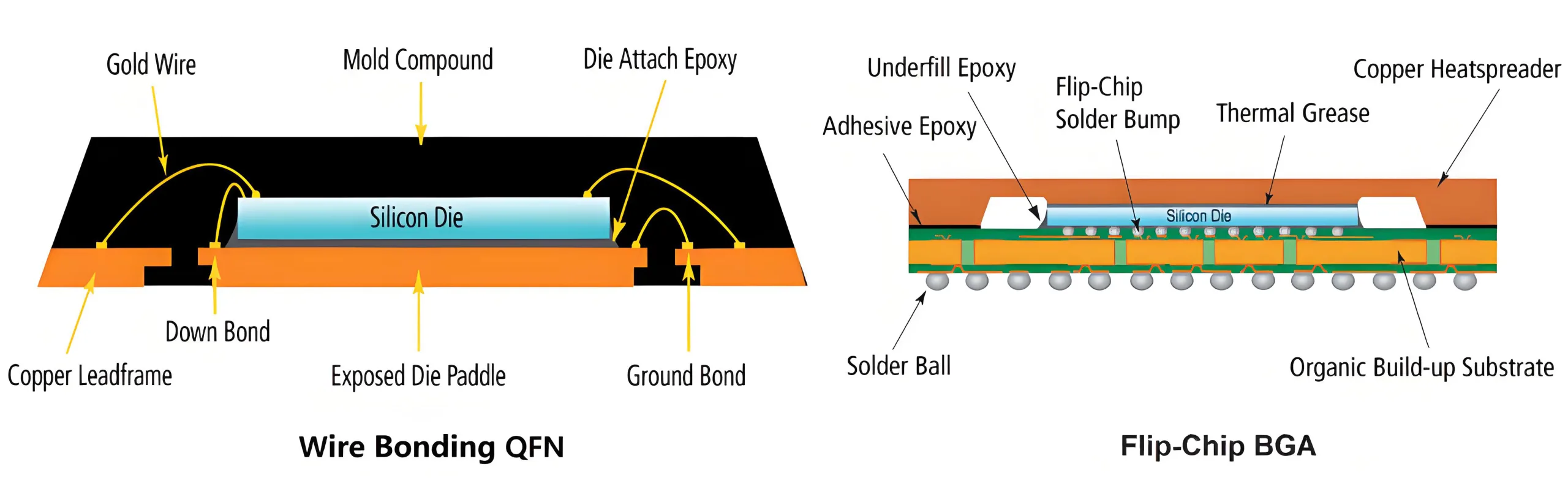

包装形態 & 結合技術

外部パッケージフォーム (QFP/BGA/WLCSP) 内部結合は本質的にリンクされています:

-

ワイヤーボンディング:

-

成熟, 低コスト

-

QFP/QFN/ミッドレンジBGAを支配します

-

ワイヤーを持っている/付き; 中程度のI/O

-

-

フリップチップ:

-

ダイは、マイクロバンプスを介して顔を下ろします

-

最短の相互接続, 最も低いインダクタンス

-

FCBGA/WLCSP/高性能CSPに不可欠

-

結論 & 将来のフロンティア

QFPからLGA/BGAへ、そして最後にCSP/WLCSP, チップパッケージの進化はaです 宇宙圧縮のクロニクル, パフォーマンスの向上, コストの最適化. 各小型化の跳躍は、PCB設計を再形成します, 多層 HDI, および高度な材料.

次のフロンティア: TSVのようなテクノロジー (スルーシリコン経由), SiP (システムインパッケージ), 2.5D/3D ICは、3D不均一な統合を有効にするようになりました, PCB設計を新しい次元に押し込む - 次の記事で調査する.

10億のトランジスタが標高の大きいサイズのパッケージに収まる場合, 分子スケールでの電子工学の戦い.

UGPCBのロゴ

UGPCBのロゴ

情報を共有していただきありがとうございます.

おお、このブログは素晴らしいです、あなたの記事を読むのが本当に好きです. これからも良い絵を描き続けてください! あなたは知っています, 多くの人がこの情報を探しています, あなたは彼らを大いに助けることができます.