PCB 레이아웃: 전자 시스템 성능을위한 중요한 전장

PCB 레이아웃은 물리적 회로 연결을 초월합니다, 기본적으로 신호 무결성을 결정합니다, EMC 성능, 비용 효율성. UGPCB 데이터가 확인됩니다: 최적화 된 레이아웃은 EMI 방사선을 줄입니다 30% (IEC 61000-4-2 준수) 전력 효율성을 높이십시오 22%. 5Gbps를 초과하는 신호의 경우, 임피던스 공차는 ± 5% 이내에 제어해야합니다. (공식: z₀ = √(l/c)), 엄격한 PCB 스택 업 디자인 및 재료 선택 요구.

7 핵심 기술: UGPCB의 레이아웃 방법론

-

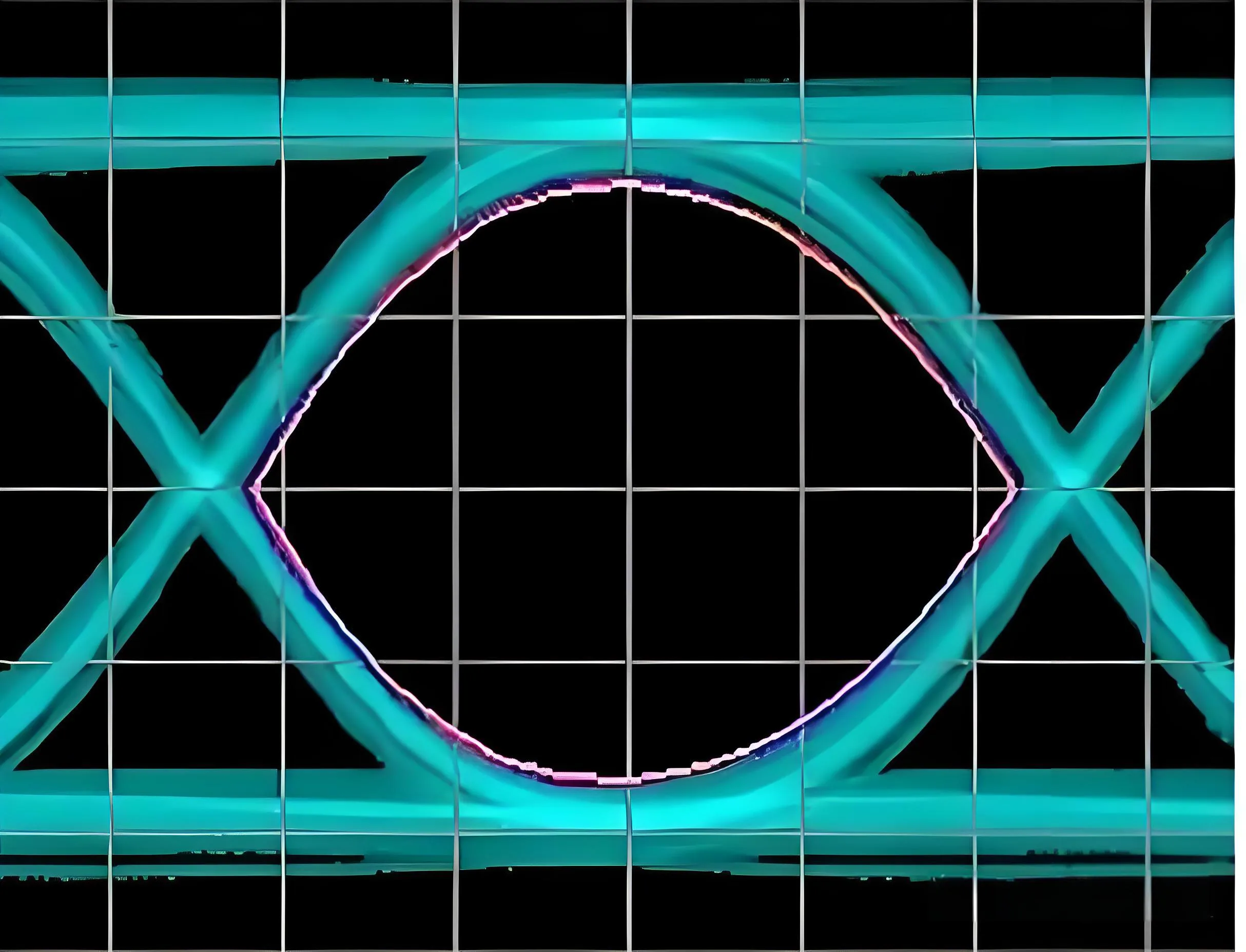

고속 신호 처리 (1.5-28Gbps)

-

차동 쌍 길이 일치: ± 5mil 정밀도

-

손실 제어: 쓰러뜨리다 6 기판 (DK= 3.7, Df= 0.002) 28Gbps 신호의 경우

-

-

파워 무결성 혁신

3D EM 시뮬레이션을 통해 최적화 된 PDN 임피던스:대상 임피던스 공식: z_target = (V × 리플%) / (i × 50%)

사례 연구: GPU 코어 전력 솔루션 감소 전압 변동 감소는 120MV에서 35MV로

-

혼합 신호 분할 전략

-

디지털/아날로그 간격: ≥8 × 보드 두께

-

자동차 솔루션: ISO를 사용한 AEC-Q100 구성 요소 배치 26262 인증

-

산업 진통제 솔루션

소비자 전자 제품의 HDI 설계 문제

| 도전 | UGPCB 솔루션 | 결과 |

|---|---|---|

| 0.2mm microvia 채우기 | 레이저 드릴링 + 맥박 도금 | 99% 수율 |

| 5G Wi -Fi 간섭 | 3D EM 차폐 디자인 | 40% 더 낮은 BER |

성공 사례: 48-계층 서버 마더 보드 설계

-

주요 사양:

-

신호 레이어: 32

-

차동 쌍: 287 세트

-

타이밍 제어: ± 12ps

-

-

입증 된 결과:

*”PCIe 4.0 신호 손실은 -8.2dB에서 -5.3dB로 감소했습니다, 대량 생산 가속 11 weeks”*

- HPC 클라이언트 평가

UGPCB의 레이아웃 서비스를 선택하는 이유는 무엇입니까??

-

전문가 팀: 엔지니어 10+ years’ experience averaging 800+ 고속 디자인

-

엔드 투 엔드 지원:

-

회로도 설계 → SI/PI 시뮬레이션 → 레이아웃 최적화 → DFM 검증 → PCBA 공동 디자인

-

-

비용 관리: 15% 최적의 계층 계획을 통한 자재 절약