PCB 임피던스 제어 마스터 링: 고속 회로 설계를위한 고급 전략

수치 1: 다층 PCB 설계에서 중요한 임피던스 제어 트레이스

현대 전자 제품에서 임피던스 제어의 중요한 역할

고주파 디자인에서 임피던스 매칭이 중요한 이유

위의 고속 디지털 시스템에서 1 GHz, PCB 트레이스는 단순 도체에서 특징적인 임피던스가있는 복잡한 전송 라인으로 변환 (z₀) 가장 중요합니다. 구성 요소간에 z occur 불일치가 발생할 때, 신호 반사에 도달 할 수 있습니다 35% 사고력의, 시스템 성능을 무너 뜨리는 파형 왜곡 및 타이밍 오류 발생.

불량 임피던스 제어의 주요 결과:

- 신호 무결성 저하: 시간 저하까지 상승하십시오 40% DDR4 인터페이스에서

- EMI 방사선 스파이크: 불일치 라인은 방사선 배출량을 15-20dB로 증가시킬 수 있습니다

- 전력 무결성 문제: 반환 경로 불연속은 접지 바운스를 만듭니다

기본 임피던스 개념

마이크로 스트립의 특징적인 임피던스 공식:

z₀ = frac{87}{\sqrt{E_R + 1.41}} \ln 왼쪽(\frac{5.98시간}{0.8w + 티}\오른쪽)

어디:

- ε_R = 유전 상수 (FR4: 4.2-4.7, 로저스 4350B: 3.48)

- H = 유전체 두께 (mm)

- w = 흔적 너비 (mm)

- t = 구리 두께 (온스)

차동 쌍 계산:

지_{차이} = 2z₀ 왼쪽(1 - 0.48e^{-0.96쉿}\오른쪽)

s = 쌍 간격, H = 유전체 높이

PCB 임피던스 엔지니어링의 5 개의 기둥

1. 재료 선택 매트릭스

| 재료 유형 | ε_R @10GHz | 손실 탄젠트 | 비용 지수 |

|---|---|---|---|

| FR-4 | 4.5 | 0.02 | $ |

| 로저스 4350B | 3.48 | 0.0037 | $$$ |

| I -RA Island | 3.45 | 0.0031 | $$$$ |

| PTFE 복합재 | 2.2-3.0 | 0.0009 | $$$$$ |

테이블 1: 고주파 라미네이트 비교

2. 스택 업 아키텍처 원리

25Gbps 신호에 대한 최적의 12 층 HDI 스택 업:

- L1: 신호 (0.5온스)

- L2: 지면

- L3: 신호 (3.5MIL 유전체)

- L4: 힘

- L5: 신호 (고속)

- L6: 지면

… 미러 대칭 구조

중요한 매개 변수:

- 유전체 두께 내성: 최대 ± 10%

- 구리 거칠기: <2μm RMS >10GHz

- 임피던스 연속성을위한 순차적 라미네이션

3. 고급 계산 방법론

3 단계 임피던스 검증 프로세스:

- 초기 추정:

경험적 공식을 사용하십시오:w pid frac{100시간}{\sqrt{E_R}} \쿼드 (\텍스트{50ω 마이크로 스트립}) - 정밀 시뮬레이션:

- 다층 구조의 경우 극 SI9000

- RF/전자 레인지 라인의 Rogers MWI-2017

- 생산 후 확인:

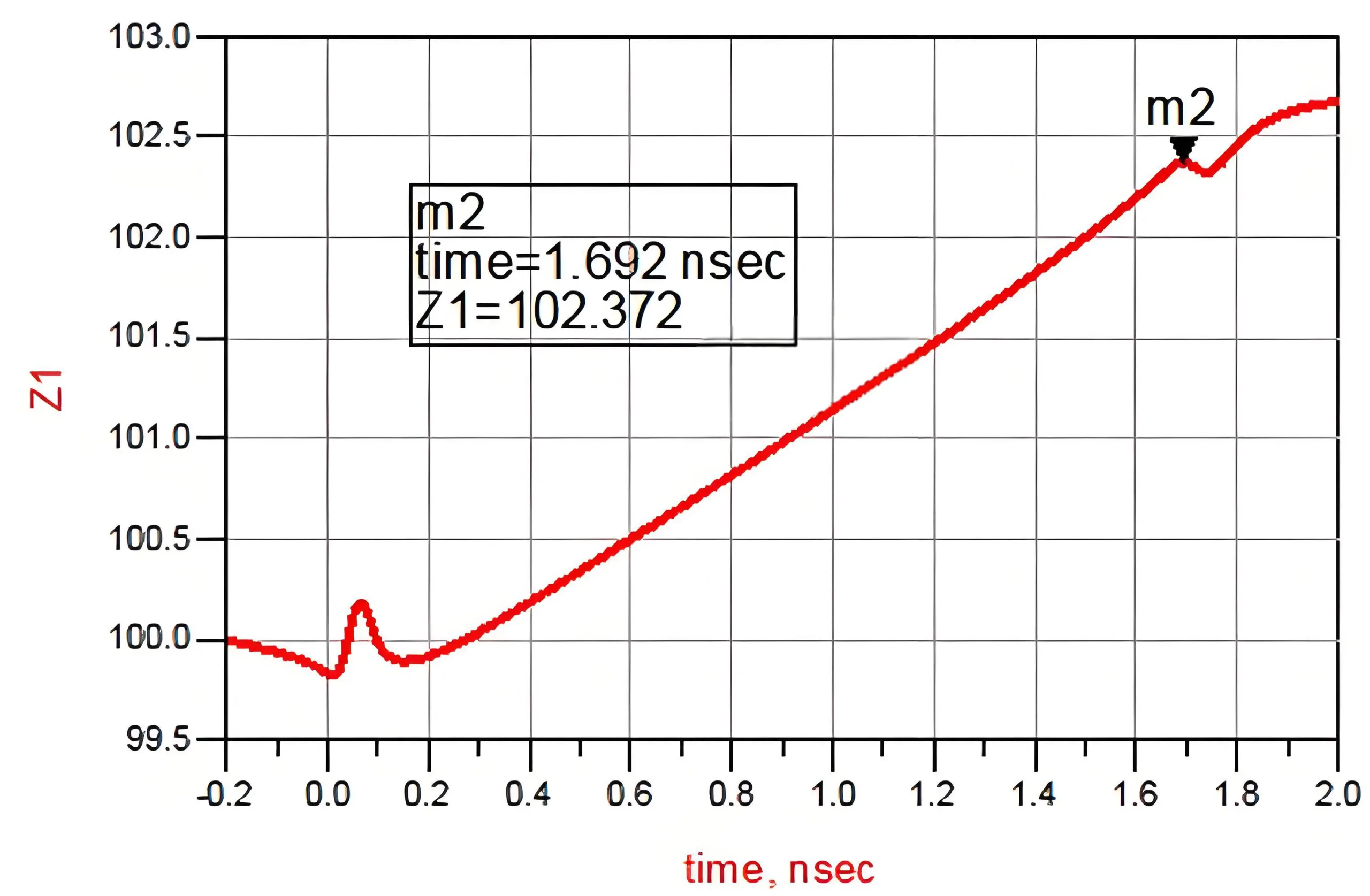

TDR 측정 <5% 용인

4. 제조 공정 제어

중요한 내성 요인:

| 매개 변수 | 전형적인 공차 | z₀에 미치는 영향 |

|---|---|---|

| 에칭 너비 | ± 0.5mil | ± 3Ω |

| 유전체 두께 | ± 10% | ± 8Ω |

| 구리 중량 | 0.2oz | ± 2Ω |

| 솔더 마스크 | 0.3-0.5밀 | ± 1.5o |

IPC-2141A 표준의 데이터

완화 전략:

- 보상 아트 워크를 사용하십시오 (0.75× 에칭 계수)

- 자동화 된 광학 검사를 구현하십시오 (AOI)

- 제어 된 임피던스 테스트 쿠폰을 지정하십시오

5. 최첨단 도구 생태계

업계 최고의 소프트웨어 솔루션:

- 극기 기기 SI9000E

- 2d 필드 솔버 47 전송 라인 모델

- 복잡한 설계를위한 배치 처리

- 로저스 MWI-2017

- 최대 110GHz의 전자 레인지 디자인에 특화되어 있습니다

- 통합 자료 데이터베이스 50+ 기판

- Cadence Sigrity Aurora

- 3d em 시뮬레이션 <2% 오류 마진

- DDR5/PCIE6.0 준수 확인

- Altium 임피던스 프로파일 러

- 실시간 임피던스 시각화

- 자동화 된 스택 up 유효성 검사

엔지니어를위한 실제 설계 지침

최초의 오른쪽 디자인에 대한 황금 규칙

- 3Crosstalk 제어 규칙:

S ≥ 3 × W 쿼드 (\텍스트{여기서 s = 추적 간격}) - 길이 일치 우선 순위:

- 차동 쌍: <5쌍 쌍 내일 불일치

- 버스 신호: <100PS 지연 꼬치

- 최적화 기술을 통해:

- 10Gbps 신호에는 8-12mil 직경을 사용하십시오

- 스터브 길이에 대한 배경 <15% 상승 시간의

- 종료 전략:

유형 애플리케이션 전력 비용 시리즈 22Ω 소스 엔드 낮은 평행 50Ω 엔드 포인트 높은 AC 용량 성 DDR 메모리 인터페이스 중간

임피던스 관리의 미래 추세

새로운 기술에 영향을 미칩니다

- 5G mmwave 도전:

- 28/39GHZ 대역에는 ± 1Ω 공차가 필요합니다

- 2μm 라인 폭 컨트롤을위한 레이저 절제

- 고급 포장 통합:

- 3TSV 임피던스 매칭이있는 D IC

- 하이브리드 기판 PCB-Flex 디자인

- AI 중심 임피던스 최적화:

- 제조 변동을 예측하는 신경망

- 다중 구조 솔루션을위한 생성 설계

견적을 받으려면 조치를 취하십시오

UGPCB 두 PCB에서 선도적 인 위치를 보유하고 있습니다 (인쇄 회로 기판) 및 PCBA (인쇄 회로 보드 어셈블리) 부문, 업계 리더로 만들었습니다. UGPCB는 PCB 임피던스 제어에서 탁월한 숙련 된 PCB 설계 팀을 자랑합니다., 업계의 최전선에서 순위. PCB 임피던스와 관련된 질문이나 설계 요구 사항이있는 경우, 기술 지원을 위해 전문 기술 직원에게 문의하거나 조치를 취하고 오늘 경쟁 견적을 요청하십시오..