ในขอบเขตของอะนาล็อก การออกแบบวงจร, แอมพลิฟายเออร์ปฏิบัติการ, ตัวต้านทานความแม่นยำ, และตัวเก็บประจุมักจะเรียกร้องสปอตไลท์. แต่ปัจจัยที่แท้จริงของขีด จำกัด ประสิทธิภาพของระบบคือผู้บงการที่ซ่อนอยู่ในฉากหลัง: ที่ แผงวงจรพิมพ์ (พีซีบี). รากฐานเงียบนี้มีส่วนประกอบทั้งหมดในขณะที่ปกครอง ความสมบูรณ์ของสัญญาณ, การปราบปรามเสียง, และ ความน่าเชื่อถือของระบบ ผ่านการติดตามทุกมิลลิเมตร, แต่ละชั้นอิเล็กทริก, และทุกการตัดสินใจบนพื้นฐาน.

วิทยาศาสตร์วัสดุ PCB: การถอดรหัสประสิทธิภาพความถี่สูงเกินกว่าการจัดอันดับ FR

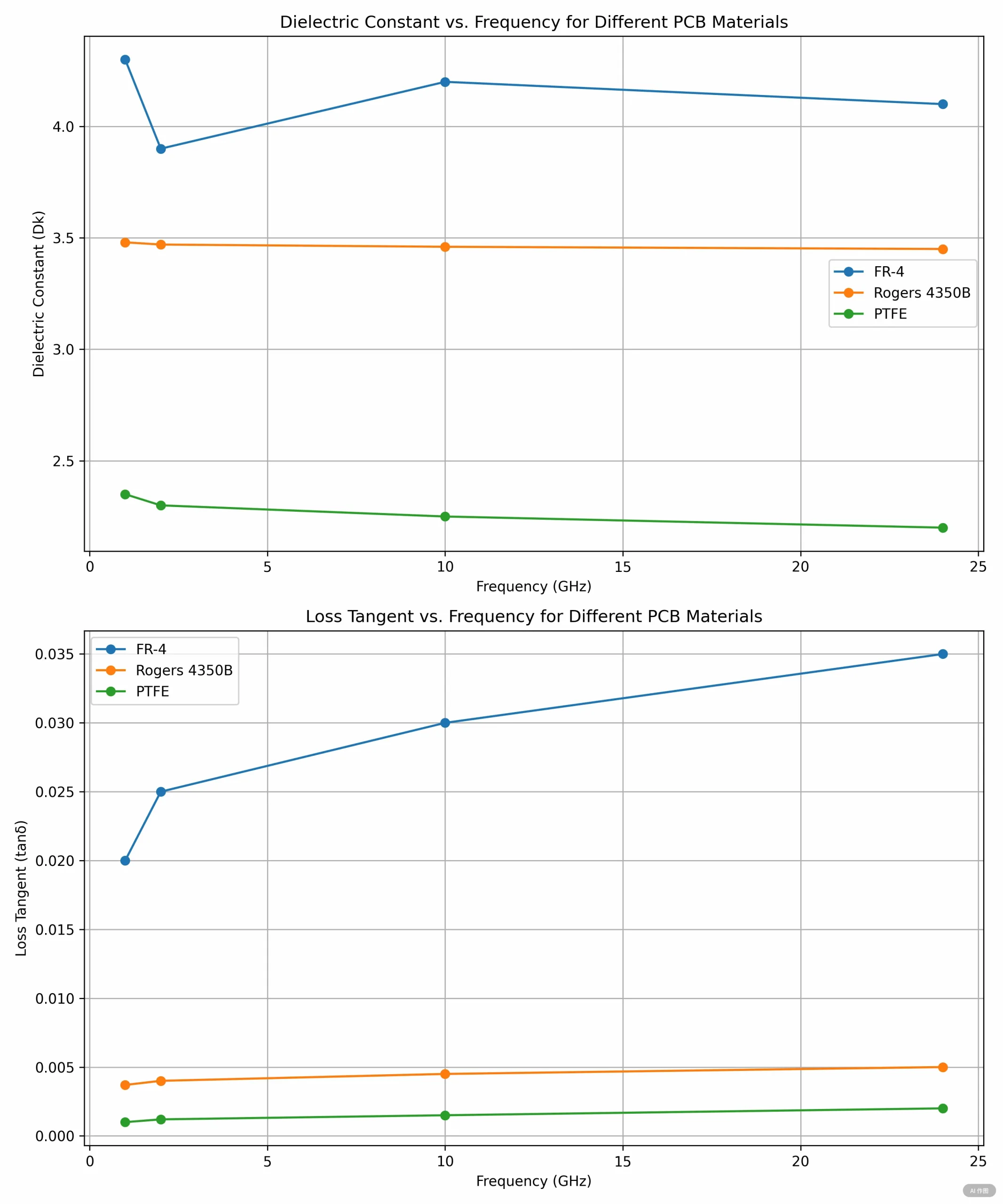

เมื่อพูดคุย วัสดุ PCB, การจัดอันดับ FR-4 การติดเชื้อเป็นเพียงบทนำ. สำหรับวงจรอะนาล็อกความเร็วสูง, ค่าคงที่ไดอิเล็กตริก (ดีเค) และ ปัจจัยการกระจาย (สีแทน) เป็นจุดด่างทางที่มองไม่เห็นด้วยมือ.

ความเร็วการแพร่กระจายสัญญาณ (V) ถูกกำหนดโดย:

v = c / √(ε_r)

โดยที่ * c * = ความเร็วของแสง, e_r = การอนุญาตแบบสัมพัทธ์. ε_rของ FR-4 ผันผวนระหว่าง 4.2-4.8, ก่อให้เกิด 5% การแปรผันของสัญญาณการหน่วงเวลา. วิกฤตมากขึ้น, ลักษณะการสูญเสีย - ที่ 10GHz, มาตรฐาน FR-4 แสดงtanΔ = 0.02, เทียบเท่า 0.5การสูญเสียสัญญาณ db ต่อนิ้ว.

การมีส่วนร่วมของอุณหภูมิความชื้น พิสูจน์ให้เห็นถึงความตายโดยเฉพาะอย่างยิ่งในวงจรความแม่นยำ:

-

1% การดูดซับความชื้นช่วยลดความต้านทานพื้นผิว FR-4 โดยสามคำสั่งของขนาด

-

15% DK ดริฟท์ที่ 85 ° C เลื่อนความถี่ของตัวกรองศูนย์

ข้อมูลเชิงลึกของผู้เชี่ยวชาญ: PCBs ทางการแพทย์โดยใช้ Rogers 4350B (E_R = 3.48 ± 0.05) บำรุงรักษา <2% การเปลี่ยนแปลง DK จาก -40 ° C ถึง +150 ° C -สำคัญสำหรับอุปกรณ์ตรวจสอบที่ยั่งยืนเพื่อชีวิต.

สถาปัตยกรรม PCB Stackup: เส้นทางวิศวกรรมปัจจุบัน & EMI Shielding

ข้อ จำกัด ชั้นเดียว/สองชั้น

สัญญาณเกิน 10MHz สัญญาณ, 1.6บอร์ดสองด้านของ MM เผยให้เห็นจุดอ่อนของชั้นดิน. ความจุ interlayer:

C = (ε_0 * ε_r * A) / d

บอร์ดมาตรฐาน 1.6 มม. ได้รับเพียง 35pf/in² - ไม่เพียงพอสำหรับ >100การปราบปรามเสียงรบกวน MHz.

การปฏิวัติ Stackup สี่ชั้น

ระนาบพลังงาน/พื้นดินโดยเฉพาะแปลงการควบคุมอิมพีแดนซ์:

-

0.2mm dielectrics เพิ่มความจุเป็น 280pf/in²

-

ความต้านทานระนาบกราวด์ลดลงถึง 1/100th ของชั้นเดียว

-

การลดทอนเสียงที่เปล่งประกายดีขึ้นโดย 40dB

กลยุทธ์การต่อสายดิน: การจัดตั้งเขตแดนดิจิตอลแบบอะนาล็อก

การแยกระนาบวิกฤต

ระนาบกราวด์ดิจิตอล/อะนาล็อกที่ทับซ้อนกันสร้างช่องสัญญาณรบกวนแบบ capacitive:

C_coupling = (ε * A_overlap) / d

แม้แต่ 0.1 มม. ²ซ้อนทับในบอร์ด 1.6 มม. ก็ยังสร้างความจุ 0.3pF การมีเพศสัมพันธ์-เพียงพอที่จะฉีดเสียงนาฬิกา 100MHz ลงในสัญญาณอะนาล็อกระดับμv.

หลักการเริ่มต้น

การต่อสายดินจุดเดียวช่วยลดการวนลูปภาคพื้นดินทางคณิตศาสตร์:

V_noise = -dΦ/dt = -2πf * B * A

ที่ไหน ข = ความหนาแน่นฟลักซ์แม่เหล็ก, อัน = พื้นที่วนรอบ. การบรรจบกันที่จุดหนึ่งช่วยลดพื้นที่ลูป.

การปิดบังความถี่ส่วนประกอบ: เมื่อตัวต้านทานกลายเป็นตัวเหนี่ยวนำ

ปรสิตต้านทาน

0805 ตัวต้านทานฟิล์มประกอบด้วย≈2nh parasitic inductance. ที่ 100MHz:

X_L = 2πfL = 1.26Ω

เกินค่าความต้านทานทั่วไป, การเปลี่ยนแปลงพฤติกรรมวงจรโดยพื้นฐาน.

กับดักความกลมกลืนของตัวเอง

ความต้านทานตัวเก็บประจุดังต่อไปนี้:

|Z| = √[R_ESR² + (X_L - X_C)²]

ตัวเก็บประจุ Tantalum 10μFมาตรฐานที่ 300kHz, มีประสิทธิภาพสูงกว่า0.1μfเซรามิกที่ 10MHz:

เรขาคณิต: ความหายนะของ EM ที่ 90 ° Bend

ร่องรอยมุมขวาทำหน้าที่เป็นเสาอากาศที่ซ่อนอยู่ในความเร็วสูง เค้าโครง PCB:

-

เพิ่มความยาวของการติดตามอย่างมีประสิทธิภาพโดย 26%

-

ความจุมุมทำให้เกิดความต้านทานต่อความต้านทาน

-

เปล่งประกาย 30dB ได้อย่างมีประสิทธิภาพมากกว่า 45 °โค้ง

Vias แสดงถึงอันตรายที่เท่าเทียมกัน. การเหนี่ยวนำของกาฝาก 0.3 มม. ผ่าน:

L ≈ 5.08h [ln(4h/d) + 1] (pH)

โดยที่ * h * = ความหนาของบอร์ด (มม), *D* = เส้นผ่านศูนย์กลางของหลุม (มม). ที่ 1GHz, เดี่ยวผ่านบอร์ด 1.6 มม. สร้างปฏิกิริยา1.6Ω.

การป้องกันที่ดีที่สุด: จากการทำความสะอาดนาโนไปจนถึงกรง

การควบคุมการปนเปื้อนของอิออน

โหนดที่มีความต้านทานสูงต้องการสารตกค้างไอออนิกด้านล่าง:

<1.56 μg/cm² (IPC J-STD-001 Class 3)

การทำความสะอาดอัลตราโซนิกด้วยน้ำสำเร็จรูป <0.3μg/cm².

ประสิทธิภาพการป้องกัน EMI

ประสิทธิภาพของกรงฟาราเดย์ตามมา:

SE(dB) = 20log[(Z_0)/(4Z_s)] + 20log(e^(t/δ))

ที่ไหน d = ความลึกของผิวหนัง. 1อลูมิเนียมมม. ให้การลดทอน 120dB ที่ 1GHz, แต่ช่องว่าง 0.1 มม. จะลดลงเป็น 30dB.

การเปิดเผยของสถาปนิกที่มองไม่เห็น

ข้อมูลเปิดเผยความจริงที่น่าตกใจ: 68%+ ความล้มเหลวของวงจรเกิดจากข้อบกพร่องในการออกแบบ PCB. เมื่อมองว่าเป็นเพียงผู้ให้บริการส่วนประกอบ, PCB เป็นจริง สถาปนิกระบบที่มีความสำคัญ.

ในวงจร 10GHz:

-

การสูญเสียอิเล็กทริก FR-4 สามารถใช้พลังงานสัญญาณ 15dB

-

0.5การกระโดดกราวด์มม. ทำให้เกิดการตีกลับพื้น 300mV

-

การตกค้างของฟลักซ์ด้วยกล้องจุลทรรศน์สร้างเส้นทางการรั่วไหล

การปฏิวัติการออกแบบเริ่มต้นด้วยการเปลี่ยนกระบวนทัศน์: จัดประเภท PCBs ใหม่จากรายการต้นทุนเป็น องค์ประกอบการทำงานหลัก. เมื่อวาง op-amp ครั้งต่อไปของคุณ:

-

การปรับปรุงเสียงรบกวน 0.1dB นั้นอาศัยอยู่ในค่า DK ลามิเนต

-

ระยะเวลา 3PS เหล่านั้นอยู่ในความหนาของระนาบพื้นดิน

Elevate this “invisible architect” from backstage to center stage, และวงจรอะนาล็อกของคุณจะทำลายอุปสรรคประสิทธิภาพ.