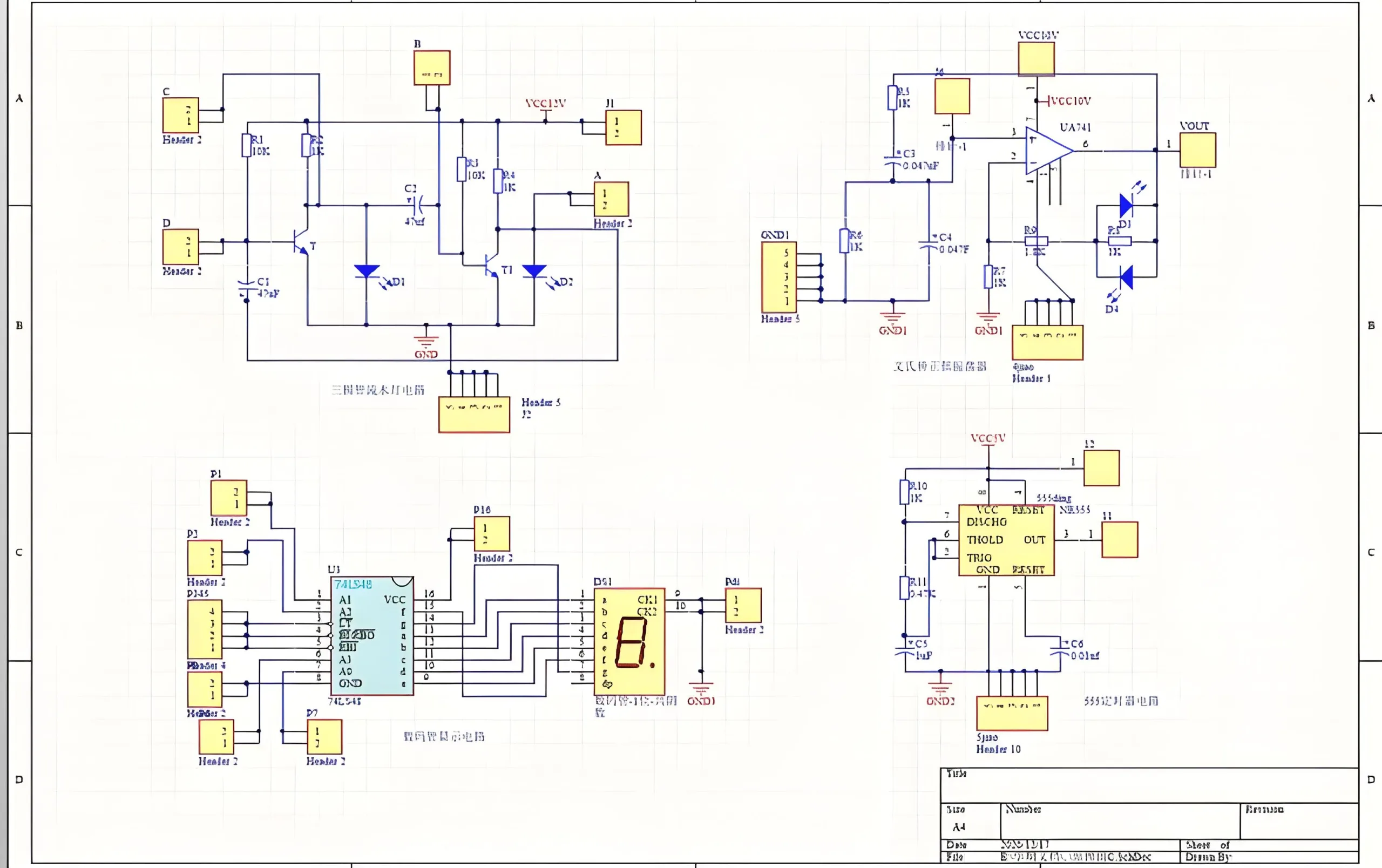

At the convergence of high-speed digital circuits and precision analog systems, an exquisitely designed ثنائي الفينيل متعدد الكلور schematic determines product viability – with 90% of design failures originating from power integrity collapse.

When engineers route the 37th DDR4 length-matched trace in Altium Designer, مقاومة discontinuities hidden in layer stacks silently degrade signal integrity. UGPCB simulation data reveals: PCBs with unoptimized power modules suffer 62% failure rates, while designs implementing our split-plane technology reduce bit error rates to 10⁻¹².

The Essence of Circuitry: Core Principles of PCB Schematics & Evolution

From Wiring Diagrams to Intelligent Systems

Modern schematics have evolved into intelligent engineering ecosystems:

-

Electrical Neural Networks: Incorporate 32 design rules (trace width/spacing/impedance/crosstalk thresholds); UGPCB’s constraint manager synchronizes 12,000+ networks

-

Cross-Domain Collaboration: Allegro SI analysis shows ±18ps timing margin for critical paths in 6-layer لوحات HDI, requiring schematic-PCB-firmware co-optimization

Revolutionary Design Tool Advancements

| Tool Generation | Representative Software | Efficiency Gain | UGPCB Optimization Case |

|---|---|---|---|

| Foundational Design | Protel99SE | 1X Baseline | Legacy library compatibility for project migration |

| تصميم عالي السرعة | Altium Designer | 3.2X | Dynamic length-matching error ≤0.01mm |

| System Design | Cadence Allegro | 5.7X | 40% eye diagram margin improvement at 16Gbps |

UGPCB Case Study: Migration from OrCAD to Allegro increased BGA escape routing success from 74% ل 98%, reducing development cycles by 21 أيام.

Modular Design Methodology: Deconstructing Complex Circuits

Power Integrity: The Critical Differentiator

Topology Selection Formula:

η = \frac{P_{out}}{P_{out} + P_{sw} + P_{cond}} \quad \text{(Target η>92\%)}

UGPCB 3D Power Tree Analysis:

-

Reduced voltage droop from 220mV to 35mV in automotive ECU via LDO placement optimization

-

Hybrid Power Planes: Split/mixed plane techniques decreased ripple by 67%

Precision Control of High-Speed Signal Paths

Impedance Control Equation:

UGPCB Implementation:

-

Differential Pair Compensation: Achieved Skew<2ps in 100G optical modules

-

EM Shielding Walls: 18dB SNR improvement in طبي ثنائي الفينيل متعدد الكلور via digital/analog isolation

Industrial-Grade Design: UGPCB 9 التقنيات الأساسية

3D Stackup Architecture Optimization

Optimal 8-Layer Configuration:

L1: إشارة (عالية السرعة) L2: Solid GND L3: إشارة (Stripline) L4: Power L5: GND L6: Signal L7: Power L8: إشارة (Low-Speed)

تصديق: 12dBμV/m EMI reduction, FCC Class B certified

Manufacturing-Driven Design (سوق دبي المالي) دقة

UGPCB ±0.025mm Process Control:

-

ميكروفيا تكنولوجيا: 0.1mm laser drills, 12:1 نسبة العرض إلى الارتفاع

-

سمك النحاس: ±10% etching tolerance for 2oz outer layers

-

Solder Mask Bridges: 0.075mm minimum width prevents SMT bridging

Beyond Design: UGPCB’s Full Lifecycle Services

ضمان النزاهة إشارة

Design Phase: HyperLynx pre-layout simulation eliminates 90% risks

Validation Phase: TDR testing ensures <5% impedance deviation

Mass Production: Golden reference database for key parameter control

Smart Manufacturing Integration

Results: 48-hour prototype delivery, 99.2% عائد التمريرة الأولى

Future Lab: UGPCB’s Technological Frontiers

Silicon Substrate Heterogeneous Integration

2.5D TSV Interposers:

-

0.3mm pitch interconnects for FPGA-HBM integration

-

Thermal resistance reduced to 0.15°C/W

AI-Driven EDA Revolution

NeuroRoute Engine:

-

8X routing efficiency improvement

-

Optimization function:

Min(ΔL, Crosstalk, Via_Count) -

Deployed in 5G mmWave antenna array ثنائي الفينيل متعدد الكلور designs

شعار UGPCB

شعار UGPCB

وي شات

امسح رمز الاستجابة السريعة ضوئيًا باستخدام WeChat