Introduzione: La guerra su scala millimetrica in DDR5 PCB Design

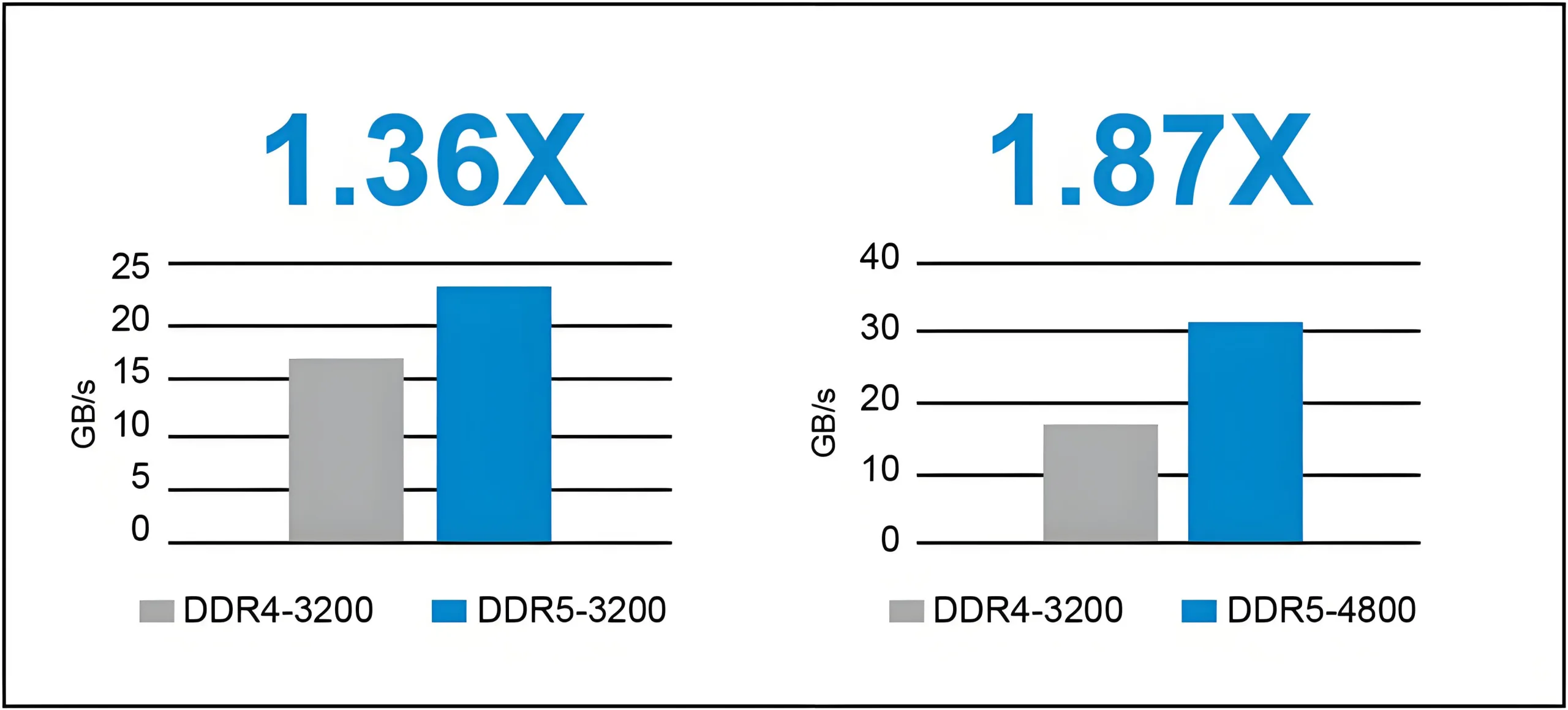

Il salto da DDR4 a DDR5 segna un turno di paradigma: Le velocità del segnale aumentano da 3,200 MT/S a 6,400 MT/S mentre le tensioni operative crollano a 1.1V. Questa doppia sfida si trasforma PCB Routing dall'ingegneria di connettività semplice in guerra di precisione su scala millimetrica. I dati del settore lo rivelano 80% dei fallimenti di progettazione DDR5 provengono da problemi di routing, con 90% Prevedibile attraverso la simulazione pre-layout. Questo articolo analizza cinque insidie di routing DDR5 critiche, supportato da dati empirici e casi studio, Fornire soluzioni fruibili per i professionisti del PCB.

1. Caratteristiche fisiche DDR5: Perché i metodi di progettazione PCB tradizionali falliscono

1.1 Tasso di segnale e rivoluzione della larghezza di banda

Per DDR5-6400, La frequenza di clock efficace raggiunge 3,200 MHz, con tassi di bordo più veloce di 0.5 ps (20-80% Sorgi il tempo). Questo innesca:

-

Effetto della pelle aggravato: Le correnti ad alta frequenza si concentrano sulle superfici dei conduttori, riducendo lo spessore effettivo del rame a 0.66 μm a 10 GHz.

-

Escalation delle perdite dielettriche: Substrati FR4 mostrano una tangente di perdita (Df) Di 0.02 A 10 GHz, causando >3 Attenuazione del segnale dB/pollice.

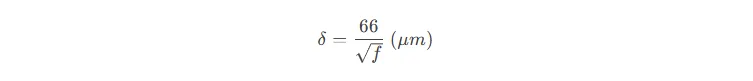

Convalida della formula (Profondità della pelle):

A f=10GHz, δ≈0,66μm,lasciando il tradizionale rame da 1 oncia (35 μm) con <2% utilizzo.

2. Cinque campi minati e contromisure per il percorso DDR5

2.1 Campo minato 1: Errore di temporizzazione: la soglia di sopravvivenza di ±15 ps

Impatto: Una mancata corrispondenza di 5 mil introduce un ritardo di ±12ps, collassando la larghezza dell'occhio orizzontale di 30%.

Caso di studio: Il design di una GPU ha subito un degrado del BER 10−12 A 10−7 a causa di un disallineamento di 8 milioni di DQ/DQS.

Soluzioni:

-

3D Compensazione del percorso: Sostituire i meandri a 90° con serpentine a 45°, riducendo la capacità parassita di 30%.

-

Calibrazione dinamica del tempo: Esegui simulazioni Monte Carlo (Sigrità della cadenza) coprendo variazioni di processo del ±10%..

Formula (Margine temporale):

Tmargine=Tciclo−(Tco+Tvolo+TJitter)

Per DDR5-6400 (Tciclo=0,3125 ), gli avvisi di sistema si attivano quando Tmargine<50 ps.

2.2 Campo minato 2: Discontinuità di impedenza – Lo Tsunami del segnale da 5Ω

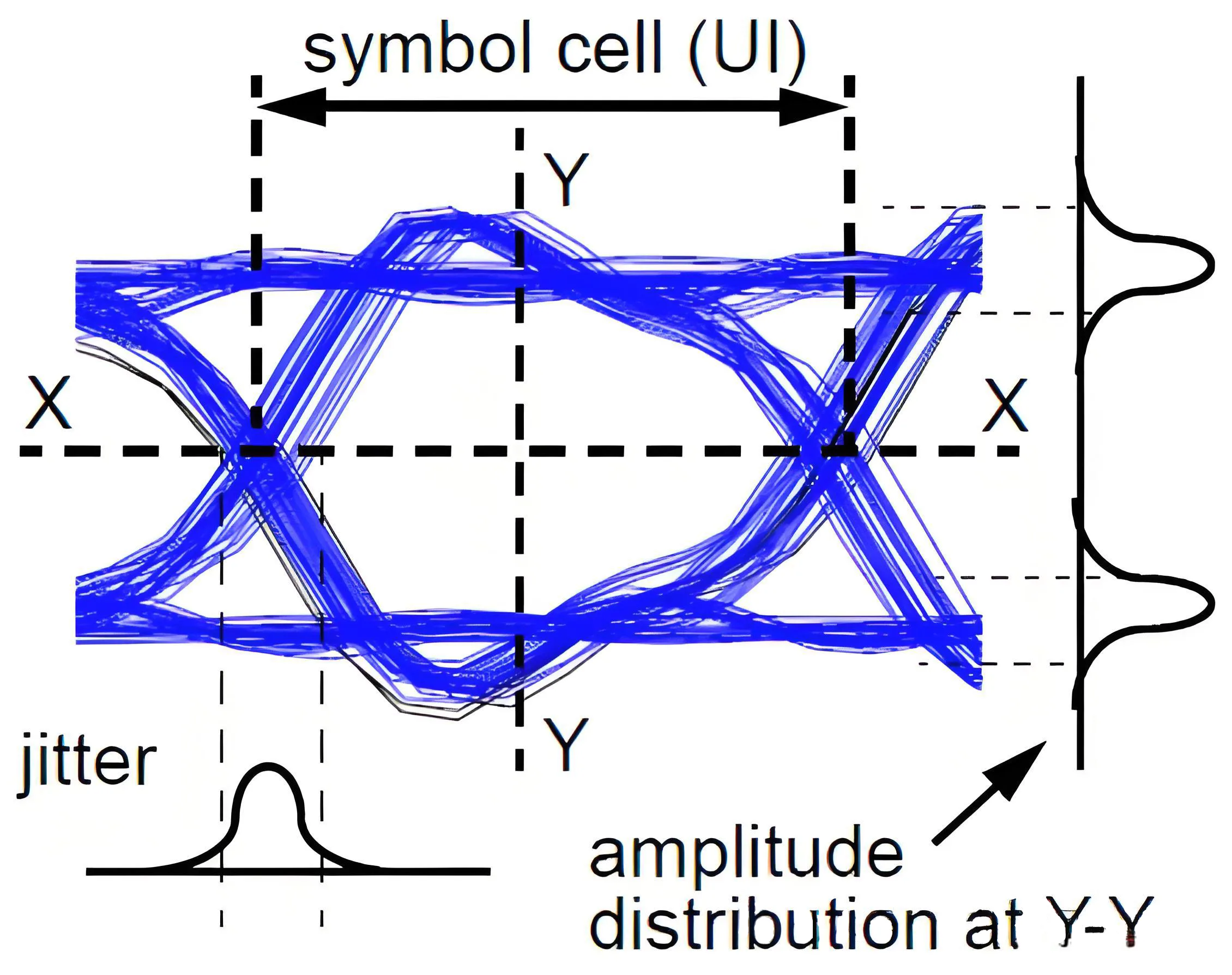

Rischio: Cause di disadattamento di impedenza >15 Perdita di ritorno in dB, collassando l'altezza verticale degli occhi di 40%.

Dati: Ogni non ottimizzato tramite aggiunge 0.2 Perdita di inserzione dB a 5 GHz.

Soluzioni:

-

Attraverso la Rivoluzione: Implementare via ciechi al laser (≤4mil) con compensazione antipad, limitando la variazione di impedenza a ±3Ω.

-

Ottimizzazione del tampone: Utilizzare cuscinetti ellittici (1.5:1 proporzioni) per ridurre gli effetti capacitivi di 20%.

Formula (Tramite modello di impedenza):

Zvia≈87ϵr⋅ln(5.98H/(0.8d1+d2))

Dove : spessore dielettrico, D1: tramite diametro, : diametro del tampone.

2.3 Campo minato 3: Ritardo incrociato: effetto farfalla da 0,1 ps/mm

Effetto tessuto in fibra: Variazione della costante dielettrica (Δϵr = 0,3) dalle cause della periodicità della fibra di vetro 0.6 ps/pollice disallineamento del ritardo.

Soluzioni:

-

Allineamento dell'asse Z: Segnali di gruppo byte di percorso ad angoli di ± 45 ° per annullare l'anisotropia dielettrica.

-

Compensazione del trasversale: Dati DK/DF del substrato di preload negli strumenti EDA per la correzione del ritardo automatico.

2.4 Campo minato 4: Potenza ondula - la reazione a catena nucleare 1MV

Sensibilità: 50MV ondulla a 1,1 V Alimentazione Aumenta il jitter del conducente di 20%.

Simulazione: L'impedenza target PDN deve essere ≤2 MΩ@100 MHz - 5x più rigorosa dei design tradizionali.

Soluzioni:

-

3Matrice di condensatore D.: Distribuire 0,1μf (0402) + 10nf (0201) condensatori vicino a ICS, copertura 10 KHZ - 2 GHz.

-

Pilastri di micro-rastrello: Incorporare pilastri di diametro da 200 μm sotto BGAS, tagliare l'induttanza del ciclo da 30%.

2.5 Campo minato 5: Torna per il percorso di restituzione - La bomba EMI invisibile

Rischio EMI: I piani di riferimento rotti generano rumore in modalità comune, superando i limiti EMI di 10 db.

Soluzioni:

-

Cuciture a terra: Posizionare Vias di terra (≤0.1o) ogni 100 mil tra gli strati di segnale.

-

Ponte a piano diviso: Usa condensatori sepolti (per esempio., AVX 0402B) per accoppiamento da 10nF tra ripartizioni di potenza.

3. Regole d'oro della progettazione DDR5: Formule e catene di strumenti

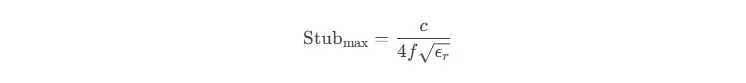

3.1 Tramite limitazione dello stub:Per DDR5-6400 (f=3,2GHz) su FR4: Tronchettomax≤14,7mm.

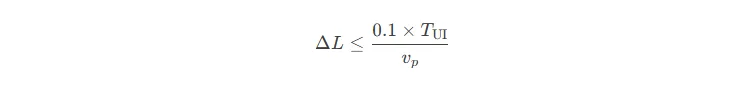

3.2 Tolleranza di coppia differenziale:

Con Tinterfaccia utente=0,3125 ns E vP=6 pollici/: ΔL≤1,9 milioni.

3.3 Obiettivo di impedenza PDN:

Per ondulazione di 50 mV e corrente transitoria di 10 A: Zbersaglio≤5 mΩ.

4. Reingegnerizzazione del processo di progettazione PCB: Da tentativi ed errori a guidati dalla simulazione

4.1 Pianificazione della topologia:

-

Via del modello in HFSS; ottimizzare le dimensioni dell'antipad.

-

Estrai l'impedenza di stackup tramite SIwave; costruire librerie di parametri S.

4.2 Esecuzione del percorso:

-

Abilita i controlli di impedenza in tempo reale in Allegro; violazioni di auto-flag.

-

Implementare la topologia fly-by con disallineamento intragruppo ≤2 mil.

4.3 Validazione:

-

Eseguire i test del diagramma a occhio (Annunci Keysight) con altezza degli occhi ≥70 mV.

-

Misurare le curve TDR; limitare la variazione di impedenza a ±5%.

Conclusione: IL “Tre corpi” Legge della progettazione DDR5

A velocità inferiore a GHz, rumore millivolt, e vincoli di tolleranza ai micron, DDR5 PCB Design entra in un “Meccanica quantistica” era. Victory in Signal Integrity Warfare richiede la convergenza della scienza materiale (Substrati a basso DK), processi avanzati (MSAP), e padronanza della simulazione.

LOGO UGPCB

LOGO UGPCB