PCB レイアウト: 電子システムのパフォーマンスのための重要な戦場

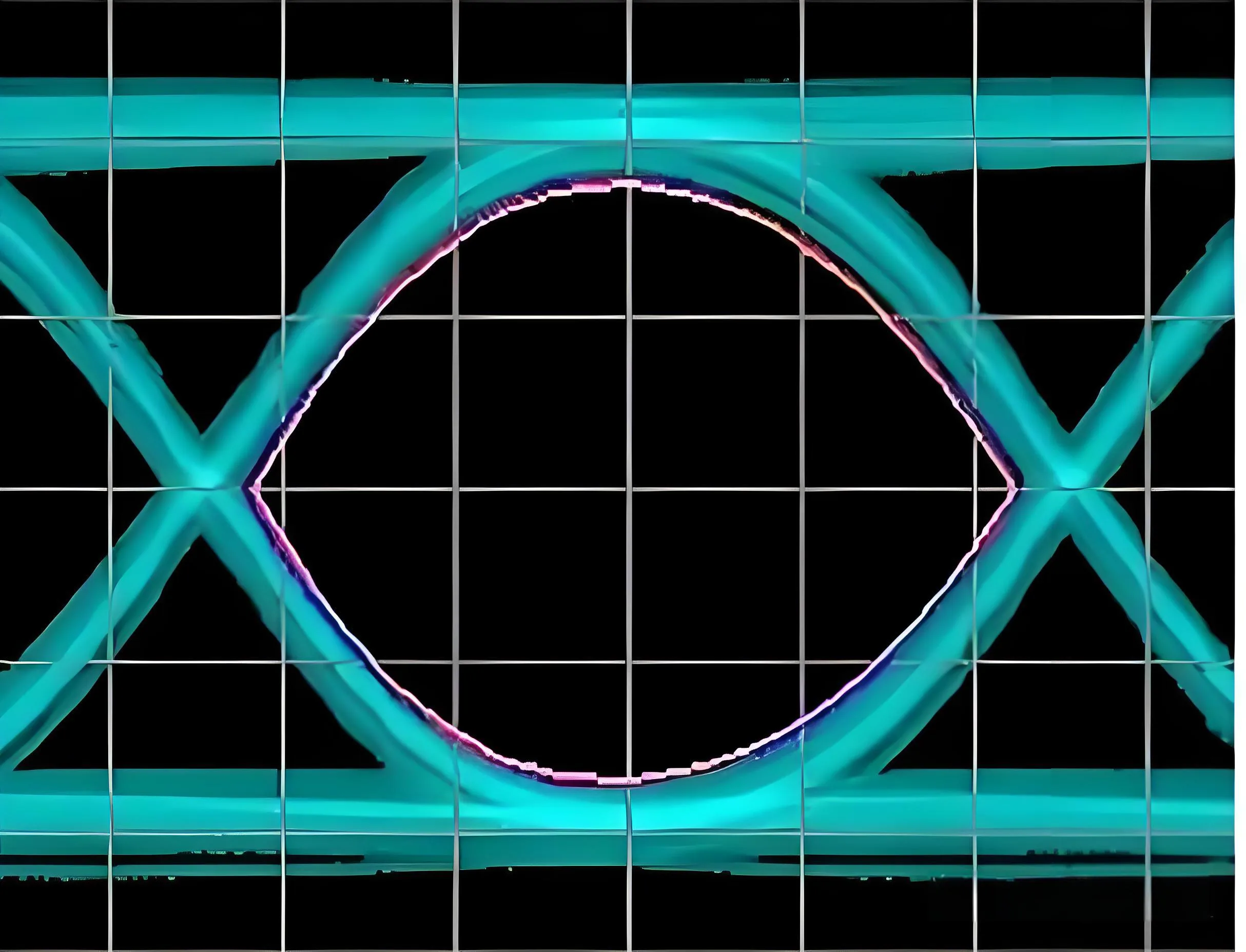

PCBレイアウトは物理回路の接続を超越します, 信号の完全性を基本的に決定します, EMCパフォーマンス, および費用効率. UGPCB データが確認します: 最適化されたレイアウトは、EMI放射を減らします 30% (IEC 61000-4-2 準拠) そして、それによって電力効率を高めます 22%. 5Gbpsを超える信号の場合, インピーダンス耐性は±5%以内に制御する必要があります (式: z₀=√(L/C)), 厳密なPCBスタックアップデザインと材料の選択を要求します.

7 コアテクノロジー: UGPCBのレイアウト方法論

-

高速信号処理 (1.5-28Gbps)

-

微分ペアの長さのマッチング: ±5mil精度

-

損失制御: 落ちた 6 基板 (DK= 3.7, Df= 0.002) 28Gbps信号の場合

-

-

パワーインテグリティイノベーション

3D EMシミュレーションを介した最適化されたPDNインピーダンス:ターゲットインピーダンス式: z_target = (v×ripple%) / (I× 50%)

ケーススタディ: GPUコアパワーソリューションは、120mVから35mVに電圧の変動を減らしました

-

混合シグナル分割戦略

-

デジタル/アナログ間隔: 8×ボードの厚さ以上

-

自動車ソリューション: ISOを使用したAEC-Q100コンポーネント配置 26262 認証

-

業界のペインポイントソリューション

家電におけるHDI設計上の課題

| チャレンジ | UGPCBソリューション | 結果 |

|---|---|---|

| 0.2MM Microvia Fill | レーザー掘削 + パルスメッキ | 99% 降伏率 |

| 5G WiFi干渉 | 3d emシールドデザイン | 40% 下部BER |

サクセスストーリー: 48-レイヤーサーバーマザーボード設計

-

重要な仕様:

-

信号層: 32

-

微分ペア: 287 セット

-

タイミング制御: ±12ps

-

-

実証された結果:

*”PCIE 4.0 信号損失は、-8.2dBから-5.3dBに減少しました, による大量生産の加速 11 週”*

- HPCクライアントの証言

UGPCBのレイアウトサービスを選択する理由?

-

専門家チーム: とのエンジニア 10+ 年’ 平均化を経験します 800+ 高速デザイン

-

エンドツーエンドのサポート:

-

概略設計→SI/PIシミュレーション→レイアウト最適化→DFM検証→PCBA共同設計

-

-

コスト管理: 15% 最適なレイヤー計画による材料の節約

UGPCBのロゴ

UGPCBのロゴ

微信

WeChat で QR コードをスキャンします