導入: The Fallacy of Perfect Length Matching

で プリント基板設計 community, a dangerous myth persists: “Match the trace lengths, and timing issues disappear.” Many engineers routing DDR, PCIE, or other high-speed buses obsess over serpentine aesthetics. They celebrate when physical length errors fall within 5 ミル. But when system clocks enter the GHz range and data rates cross the Gbps threshold, a frustrating phenomenon emerges. The physical lengths are perfectly matched. Yet the signal timing drifts. The eye diagram closes.

This failure is not a lack of effort. It is the work of invisible killers—physical effects hiding inside PCBラミネート, chip packages, and copper surfaces. 今日, we dissect the five most overlooked pitfalls in high-speed length matching.

1. The Inner Corner Effect and Skin Effect: Why Electrons Take the Inside Lane

Consider a classic simulation. Two signal traces measure exactly 100 ミル. One is straight. The other meanders. Which signal arrives first at the receiver? Intuition suggests the straight line wins. Others assume equal length means equal arrival time. Simulation proves otherwise: the serpentine trace wins.

Why does this happen?

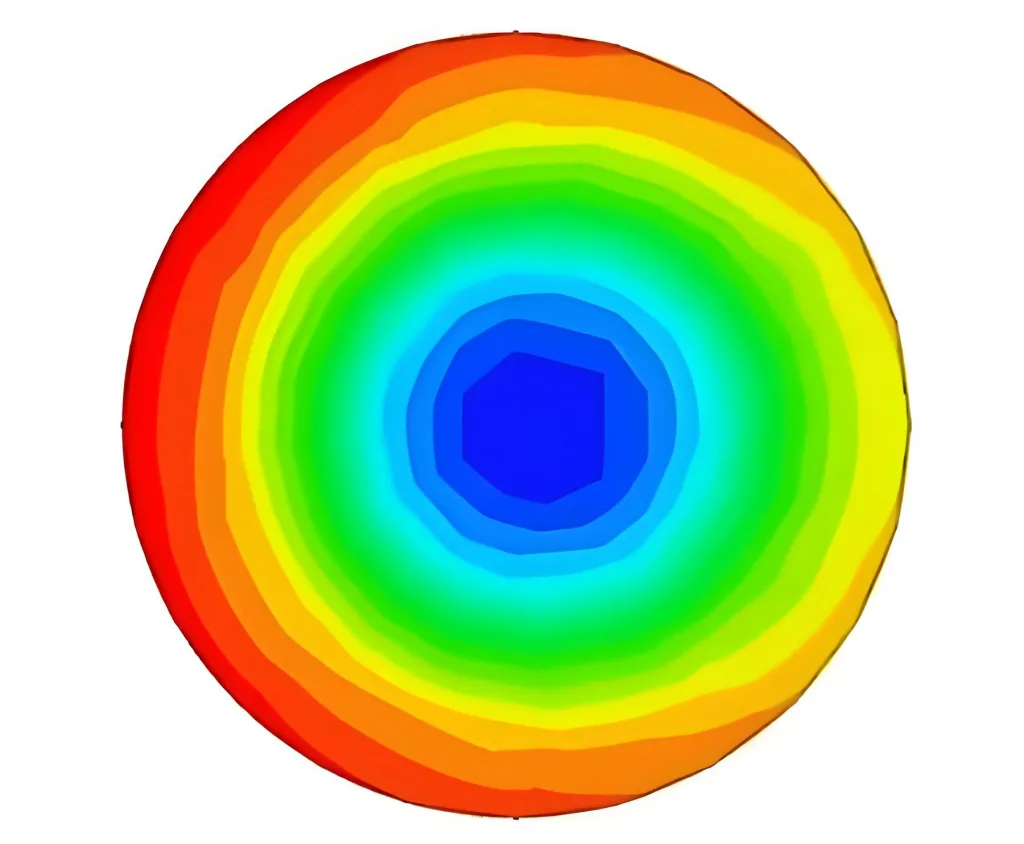

高周波数で, signal transmission is not just electron drift. It is electromagnetic wave propagation. As frequencies rise, electrons behave like skilled race car drivers. They automatically seek the inner lane—the path of lowest impedance. For traces with finite width, electromagnetic fields force current to concentrate along the inside edge of each bend. This “inner corner effect” shortens the actual electrical path compared to the geometric centerline.

This is skin effect in action. According to electromagnetic theory, alternating current concentrates on conductor surfaces as frequency increases. The skin depth (d) determines this penetration.

The formula: δ = √(r / πfμ)

-

At low frequencies, current fills the entire copper cross-section.

-

で 5 GHz, current flows only within a few micrometers of the copper surface.

What does this mean? If you increase copper thickness to 2 oz for lower DC resistance, high-frequency signals ignore your effort. They only use the surface. Wider traces offer shorter “inner lane shortcuts” at bends, creating larger timing errors. In extreme high-speed design, excessively wide traces become a length-matching nightmare.

2. Inside the Chip: The Length Hidden by the Package

We measure every millimeter of プリント基板 trace with calipers or software. But do we account for the distance signals travel before leaving—and after entering—the chip? This is pin delay.

Open a chip package. Inside, the die connects to pins or balls through microscopic bonding wires. In BGA packages, the die sits centrally while balls cover the entire bottom surface. These bond wires vary dramatically in length. One signal may travel from the die edge to Ball A1 through a short wire. Another may originate near the die center and route through complex internal traces to Ball B23.

Chip manufacturers like Intel state clearly in their timing constraint documents: I/O timing calculations (tSU, tH) must include internal delays from core logic to package pins.

The correct length equation is:

L1 (internal delay at Chip A) + L2 (PCB trace) + L3 (internal delay at Chip B) = Constant

If PCB レイアウト engineers match only L2 while ignoring variations in L1 and L3, signals arrive at the die at different times—even with perfectly matched board traces. Professional simulation tools and turn-key designs (like MTK reference layouts) exist precisely to account for these internal differences. Forcing engineers to copy reference positions ensures total delay matching.

3. The Via Effect: Impedance Traps Between Layers

In multilayer designs, vias are unavoidable. But vias represent the most typical impedance discontinuities on transmission lines. Research shows via parasitics severely degrade signal quality.

Key parasitic elements:

-

Parasitic Capacitance: Formed between via pads and antipads.

Approximate formula: c = 1.41 * e * T * D1 / (D2 – D1)

This slows rising edges and increases delay. -

Parasitic Inductance: Inherent to the via structure.

Approximate formula: L = 5.08h * [ln(4h/d) + 1]

This contributes to simultaneous switching noise (SSN) and power rail noise.

The deeper problem: stubs and non-functional pads. When a signal enters on Layer 1 and exits on Layer 3, the unused via portion from Layer 3 to Layer 8 becomes a stub. This stub acts as an antenna at high speeds, generating reflections. Back drilling removes excess stub material. But few engineers consider the extra delay caused by non-functional pads on unused layers.

Best Practice: For high-speed groups like DQS and DQ, enforce identical layer counts and via counts. Never add vias just to match length—the impedance discontinuity kills signal integrity faster than a few mils of length mismatch.

4. Layer-to-Layer Velocity Differences: Is the Surface Really Faster?

Here is a classic misconception: “Surface traces are faster.” The truth lies in dielectric constant.

Signal velocity (V) in PCB is determined by dielectric constant (Er):

V = C / √Er

Where C is the speed of light (~11.8 in/ns or 300,000,000 MS).

-

内層 (ストリップライン): Signal fully embedded in FR4. FR4 Er ranges from 4.2 に 4.5. Velocity is roughly half light speed: 5.5–6 in/ns.

-

Outer Layer (マイクロストリップ): Signal faces FR4 on one side, air (Er=1) on the other. This creates an “effective dielectric constant” (Ereff) lower than FR4’s nominal value. 結果: faster propagation, typically 6.5–7 in/ns.

If a DDR data bus mixes outer and inner layer traces, even perfectly matched physical lengths produce significant timing skew. This velocity difference must be compensated through propagation delay rules, not simple length matching.

5. The Glass-Weave Effect: Invisible Dielectric Potholes

ついに, a microscopic killer even simulations struggle to capture: the glass-weave effect. FR4 is not homogeneous. It is woven glass fiber impregnated with epoxy resin. Glass fiber has a high dielectric constant (~6). Epoxy resin is much lower (~3).

When a high-speed trace routes directly over a glass fiber bundle, the dielectric constant beneath it differs dramatically from a trace sitting in an “epoxy-rich” area. This causes tiny but significant variations in propagation velocity across the same bus. Parallel traces—one over glass, one over epoxy—arrive at different times .

ソリューション:

-

Better Materials: Use spread-glass or flat-glass high-speed laminates for more uniform dielectric distribution.

-

Angle Routing: Route critical buses at angles (10° or 45°) to avoid aligning with the glass weave grid .

結論: From Trace Artist to Timing Doctor

Modern 高速PCB設計 has evolved. “Length matching” is no longer a geometric race. It is a complex optimization involving material science, electromagnetic field theory, and semiconductor packaging. Relying solely on EDA length readouts is like the blind men and the elephant.

True signal integrity requires a “total delay” mindset. Include chip internal delays, via stubs, and layer-to-layer material differences in your calculations. When unexplained timing issues arise, stop drawing. Start investigating these deeper physical effects.

If you need a PCBサプライヤー who masters these complexities—or if your next high-speed project requires a quote for expert manufacturing and design support—contact our engineering team. We don’t just build boards. We solve signal transmission challenges from DC to GHz.