「なぜただ扱っているだけでチップが損傷するのですか?」 回路基板 普通に?多くのエンジニアは、静電気放電による回路損傷に直面して混乱を感じます。 (ESD). 実際には, 人体は、ほとんどの電子部品の許容限界をはるかに超える、数万ボルトもの静電気電圧を発生させる可能性があります。.

たとえ最も正確であっても プリント基板 (プリント基板) ESDに対して脆弱になる可能性がある. 誤って接触すると、数千ドル相当のチップが即座に故障する可能性があります.

昨今の電子機器の高度化を背景に, ESD 保護はもはやオプションの選択肢ではなく、製品の信頼性を確保するために必要な手段です. この記事では、PCB ESD 保護の主要な設計ポイントと製造上の重要事項を詳しく分析します。, 製品がこの「目に見えない稲妻」に耐えられるよう支援します。

1. ESDの脅威: 目に見えない小型稲妻の致命的な影響

ESD は目に見えない小さな稲妻として想像できます. 散歩などの日常生活, セーターを脱ぐ, あるいはプラスチックの箱を持ち上げるだけでも静電気が発生する可能性があります. この静電気の電圧はしばしば数千ボルトに達します, あるいは数万ボルトでも.

実は人体自体が最大の静電気発生源です. 特に乾季には, PCB に手を伸ばした瞬間に ESD が発生する可能性があります. プラスチック製のデスクトップなど、一見重要ではないアイテム, 化学繊維カーペット, 発泡包装箱はすべて静電気の「共犯者」になる可能性があります.

ESD は主に 2 つの形態で PCB に害を与えます。:

- ハードダメージ: これは最も直接的で明らかなダメージです. ESDはチップ内の小さな回路を瞬時に破壊します, チップに永久的な損傷を与える. 結果として, PCB は完全に機能しなくなります, または特定の機能 (シリアルポートやADCなど) 直接失敗するだろう.

- 慢性的な損傷: これはもっと隠されていて厄介です. ESDはチップを完全に破壊しない可能性があります, ただし、内部酸化層やその他の構造に微小な損傷を引き起こす可能性があります。. PCB は今でも正常に動作する可能性があります, ただし不安定になり寿命が短くなります. 数日後または特定の温度下で突然誤動作する場合があります. この断続的な障害は、デバッグ中のトラブルシューティングが最も難しく、多くの時間と労力を費やします。.

2. TVSダイオード: 回路用の高精度雷保護システム

テレビ (過渡電圧サプレッサー) ダイオードは ESD の脅威に対する防御の最前線であり、最も効果的な保護コンポーネントです. これらは「回路信号の警備員」のように機能し、通常の状態ではハイインピーダンス状態を維持します。. ESDパルスが検出されると, 瞬時に低インピーダンス状態に切り替わります。, 高電圧パルスをグランドに迂回し、バックエンドチップを保護します。.

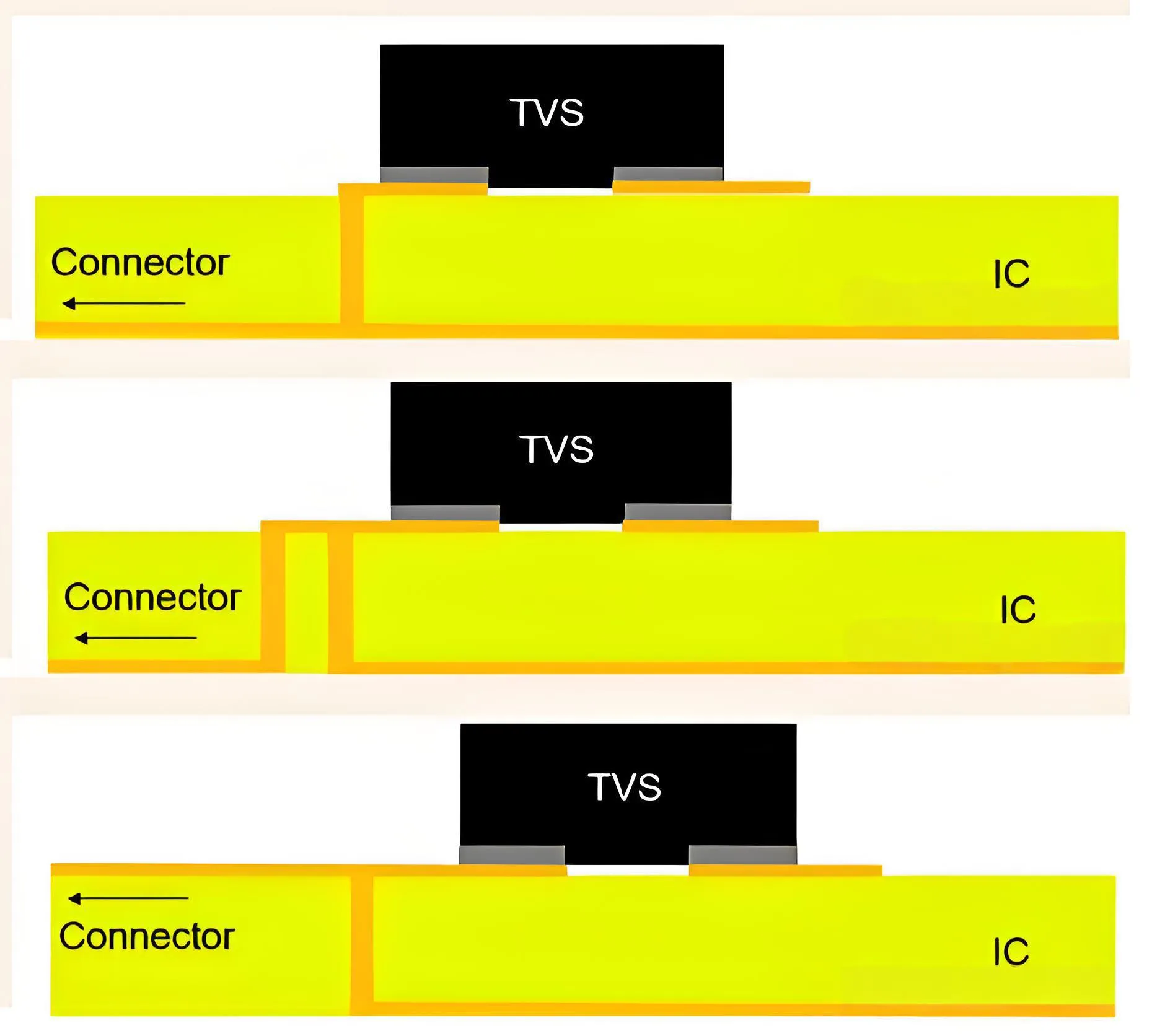

2.1 TVS レイアウトの黄金律

寄生インダクタンスは TVS 性能の最大の敵です. 回路内の寄生インダクタンス(TVS ピン自体の寄生インダクタンスを含む)は、クランプ電圧に影響します。 (Vc) ESDまたはサージが発生した場合のバックエンドICでの.

TVS の保護効果は次の式に従います。: VCL = VBR + RD×IPP. その中で:

- RD は TVS 自体の寄生容量です; RD 値が小さい製品はクランプ電圧が優れており、IC をより効果的に保護できます。.

- IPP は、テストの瞬間に TVS を通過する電流です。.

TVSの保護効果を最大限に発揮するには, アース接続をできるだけ短くし、TVS を ESD 発生源のできるだけ近くに配置する必要があります。. これはEMIを最小限に抑えるだけでなく、 (電磁妨害) PCB 上でのみならず、他のパスとのカップリングも軽減します. 応答時間が 1ns 未満の TVS デバイスを選択すると、PCBA にとって重要な高速インターフェイスに最適な保護が提供されます。 (印刷回路基板アセンブリ) 信頼性.

3. PCB レイアウトと接地: ESD保護の基礎

合理的 PCB レイアウト と接地設計は ESD 保護の基礎です. 追加の保護コンポーネントがなくても, 製品の ESD 耐性を大幅に向上させることができます。.

3.1 PCB レイアウトのポイント

- 高速信号線は基板端から 3mm 以上離してください。, 一方、低周波に敏感な信号は 2mm 以上離れている必要があります.

- クロックラインやリセットラインなどの重要な信号はグランドで囲む必要があります。 (グランドシールド). 両側にグランド線を配置し、50mmごとにグランドビアを追加.

- 露出した金属エンクロージャはすべて、直接接地による低インピーダンス ループの形成を避けるために、1MΩ 抵抗を介して一点接地する必要があります。.

- ユーザーが接触するコンポーネント間では 5mm 以上の沿面距離を維持する必要があります (ボタンやノブなど) そしてメインボード. 等電位接続を実現するには、導電性フォームまたは金属スプリングを使用します。.

- スパークギャップを設定する (0.2mm~0.5mmの間隔で) コネクタの Pin1 の位置と金属筐体の接地点. これらの対策により、ESD 電流を効果的に安全に放電させ、敏感な回路への損傷を回避できます。.

3.2 PCB 接地設計の原則

2層構造や 多層PCB, 完全かつ大面積の接地面を確保するように努めてください。. 完全なグランドプレーンは広大な平野のようなもので、ESD エネルギーをすぐに吸収して分散させることができます。, エネルギーが一点に蓄積するのを防ぐ. 同時に, TVS ダイオードに効率的な放電経路を提供します。.

PCBレイアウト時, 接地ネットワークを銅で満たし、接地銅が基板上の空き領域をできるだけ多く覆うようにします。 (跡形もなく) できるだけ. すべての外部インターフェースの場合 (USB ポートや DC 電源ソケットなど), 金属製の筐体を高電圧コンデンサを介してボードのグランドに接続するか、直接接続します。. こちらです, ESD は回路に入る前にまずエンクロージャを通って迂回され、インターフェイス レベルでの PCB ESD 保護が強化されます。.

4. ラミネート加工: 多層 PCB の内部保護バリア

多層PCBの場合, ラミネートプロセスの品質は、ボードの内部 ESD 保護機能に直接関係します。. 2 つの導体層間の誘電体が薄すぎる場合, 高電圧ESDにより簡単に破壊される可能性があります, 永久的な損傷を引き起こす.

4.1 プリプレグの中心的な役割

プリプレグ (事前含浸複合材料) 多層 PCB の層間絶縁誘電体として機能します。. 精密な製造プロセスで管理された「機能性複合材料」です, 樹脂が「Bステージ半硬化状態」であることが最大の特徴であり、多層基板の積層を実現するための鍵となる特性です。.

プリプレグは物理的な接着だけでなく3つの効果を実現します: 電気断熱 + 構造的サポート. その絶縁性能と誘電特性は、PCB の電気的信頼性を直接決定します。: 硬化後, 体積抵抗率は ≥10¹⁴Ω・cm, 破壊電圧抵抗は≧20kV/mmです, 層間リークをブロックできるため、ESD による層間損傷を防ぐために重要です.

プリプレグのコアパラメータには以下が含まれます。:

- 樹脂含有量 (RC%): 通常50%~70%, 層間の結合強度と誘電体層の厚さを決定します。.

- 流動性: 15~30mm.

- ガラス転移温度 (TG): 通常150~200℃.

- 誘電率 (DK): 4.2通常のFR-4プリプレグの場合±0.2.

4.2 ラミネート工程の品質管理

ラミネート品質を確保するために, 熱膨張係数 (CTE) プリプレグの量は FR-4 コア基板および銅箔の量と一致する必要があります. Z軸CTE偏差が5ppm/℃を超える場合, 温度サイクル中に層間亀裂が発生する可能性が高い.

ラミネート中:

- 中間層温度が80~130℃の場合, キャリアプレートの上層と中間層の温度差は25℃を超えてはなりません, 加熱速度は1.3~5℃/分を超えないようにしてください。.

- 温度が85±5℃に達したとき, 低圧から中圧に切り替える時間を決定する.

- 温度が110±5℃に達すると, 中圧から高圧に切り替える時間を決定する.

現代の PCB 製造では, 真空プレス技術によりラミネート品質が大幅に向上. 真空環境により、気泡や空隙の形成が回避されます。, プリプレグ樹脂の均一な流れと充填を確保し、多層 PCB の ESD 破壊に対する耐性を強化します。.

5. 高度なプロセスと品質検証

電子機器の高周波化、高密度化に伴い, ESD保護は新たな課題に直面しており、より高度なプロセスソリューションが必要です.

5.1 特殊用途向けのプロセス改善

- 高周波通信シナリオ: Low-Dk プリプレグ (Dk=3.48±0.03, Df<0.004) 信頼性の高い絶縁保護を提供しながら、28 GHz/77 GHz の信号伝送要件を満たします。これは、5G または車載レーダー PCB で信号の完全性と ESD 耐性を維持するために重要です。.

- 厚い銅板 (≥3オンス): 「2層低樹脂プリプレグ積層」を採用 (52%レイヤーごとに±1%, 総樹脂含有量 56%) 8MPa高圧ラミネートとの組み合わせ. これにより、誘電体層の耐電圧を 3500V まで高めることができ、電源関連の PCB の ESD 保護を強化できます。.

- HDI (高密度相互接続) ボード: 低流動性プリプレグが必要 (18±2mm) + 0.075mmマイクロビア樹脂のオーバーフロー問題を解決する真空ラミネート. これらの特殊なプロセス処理により、製品の性能が向上するだけでなく、回路基板の内部 ESD 保護機能も強化されます。.

5.2 品質検証および試験基準

閉ループ品質検証システムは、PCB の ESD 保護機能を確保するために不可欠です. それには以下が含まれます:

- 受入検査: 赤外分光計を使用して揮発性物質の含有量をテストし、誘電分光計を使用して Dk/Df の安定性を検証します.

- プロセス監視: ラミネート中に温度と圧力のデータをリアルタイムで収集.

- 完成品の検証: 層間剥離強度試験、絶縁抵抗試験を実施.

最終的な ESD 保護検証は、次の条件を満たす必要があります。 IEC61000-4-2レベル 4 標準, つまり, 最大±8kVの接触放電試験および最大±15kVの空中放電試験. テスト後, 次の基準を満たす必要があります:

- シグナルインテグリティ (アイダイアグラムの開口部 >70%).

- ビットエラー率 (<1×10^-12).

- 動作電流の変動 (<±5%).

- リセット時間 (0 回/テストサイクル).

今日のチップ製造プロセスはますます洗練されています, しかし、これは ESD に対する警戒を緩めることができるという意味ではありません. それどころか, 回路サイズが縮小し、動作電圧が低下するため, コンポーネントが静電気放電に対してより敏感になる.

今日のチップ製造プロセスはますます洗練されています, しかし、これは ESD に対する警戒を緩めることができるという意味ではありません. それどころか, 回路サイズが縮小し、動作電圧が低下するため, コンポーネントが静電気放電に対してより敏感になる.優秀な PCB エンジニアは初期設計段階で ESD 保護を考慮します, 保護対策を製品の「DNA」に組み込む. これは技術的な課題であるだけでなく、責任とプロフェッショナリズムが試されるものでもあります。最善の障害修復は、そもそも障害の発生を防ぐことであるためです。.

UGPCBのロゴ

UGPCBのロゴ