エレクトロニクス製造業界で, PCBAの降伏率 (印刷回路基板アセンブリ) 処理は、生産コストと市場の競争力に直接影響します. に基づいた研究 IPC 国際基準は、それを示しています 80% 生産欠陥のデザイン段階で特定して最適化できます.

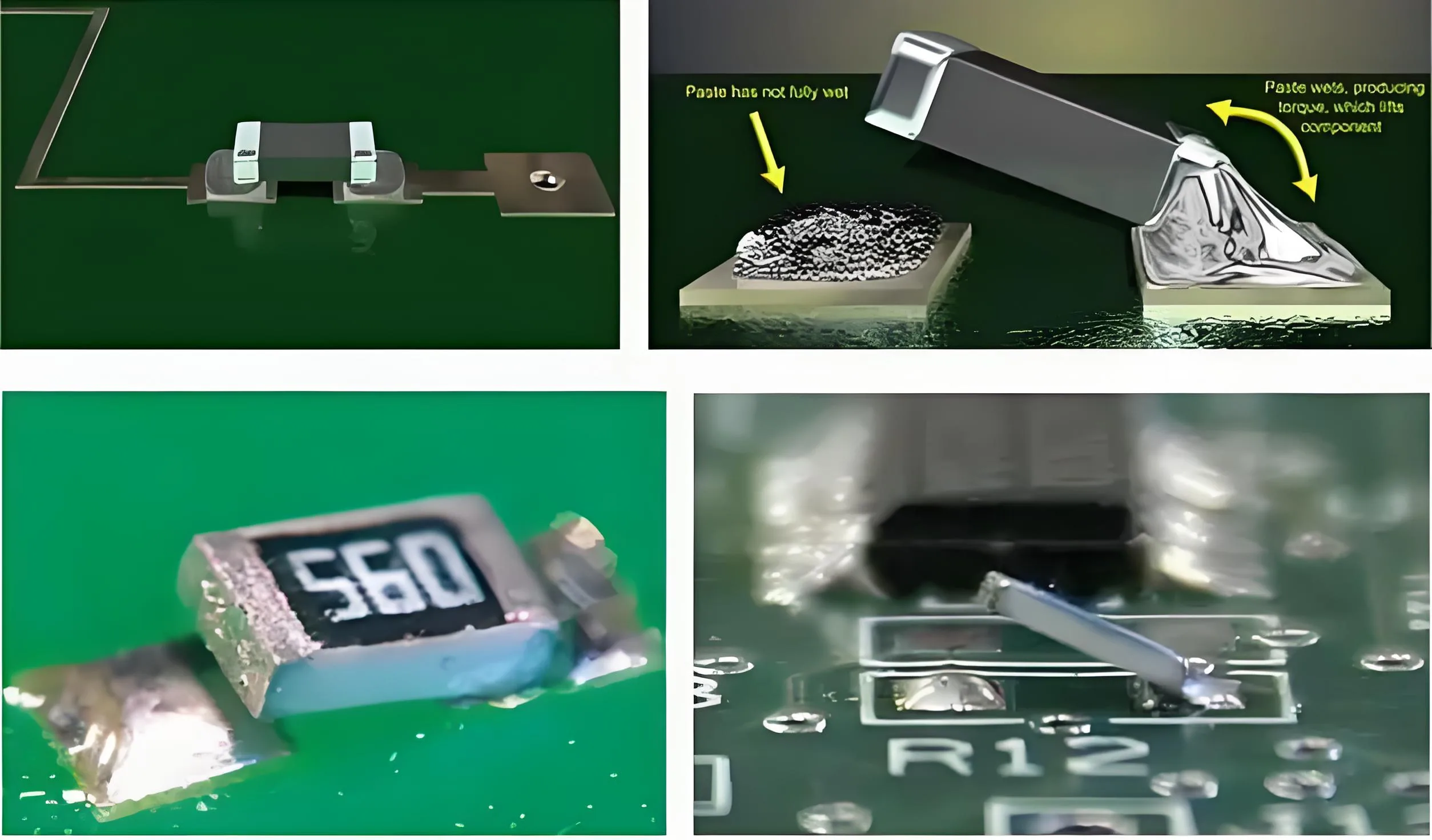

で SMT (表面実装技術) アセンブリプロセス, 墓石の欠陥 - チップコンポーネントの一方の端がパッドから離れる場所 (図に示すように 1) - 最も一般的な問題の1つです. 頻繁に小型のパッシブコンポーネントで発生します, 特に 0402 チップコンデンサと抵抗器. この記事では、詳細な分析を提供します, 実験の設計に基づいています (うーん) 方法論, ステンシルのミスレジュレーションと墓石の欠陥との関係, 実用的で効果的なソリューションを提案します.

-

墓の欠陥のメカニズムと影響

墓石の基本的な原因は、コンポーネントの2つの端子のはんだ張力の不均衡です. はんだ貼り付けが溶けたとき, 表面張力または非同期融解時間の違いにより、はんだ貼り付けが後で溶ける端で成分が上に引っ張られる可能性があります.

1.1 墓爆発の欠陥の形成メカニズム

リフローはんだ中に, チップコンポーネントの上面と下面の両方が加熱されています. 一般的に, 露出した最大の面積があるパッドが最初に熱くなります, はんだペーストの融点の上の温度に達する. 結果として, 後で濡れたコンポーネントの端は、反対側の端にあるすでにモルテンのはんだの表面張力によってしばしば引き上げられます.

はんだ張力バランスフォーミュラ:

f_net = f1 – F2 =γ_LV (cosθ₂ – cosθ₁) ・L

どこ:

f_netは正味の張力です,

γ_LVは液体蒸気表面張力です,

θは接触角です,

Lはパッドの長さです.

1.2 墓の筋肉質の欠陥への寄与要因

フィールドデータ分析に基づいています, 墓の欠陥は、主に次の要因の影響を受けます:

-

プリント基板設計 要因 (30%): 不規則なパッドサイズの設計と最適ではないレイアウト

-

材料 要因 (25%): コンポーネントのはんだが不十分です, 酸化終了

-

プロセス係数 (45%): はんだ貼り付けのミスレジストレーション, プレースメントの精度が不十分です, 不適切なリフローはんだ付け温度プロファイル

-

DOE実験設計と方法論

Dekステンシルプリンターでのミスレジスト化によって引き起こされる墓石の問題に対処する, の技術チーム UGPCB プロセスパラメーターの最適な組み合わせを識別するために厳密なDOEを設計しました.

2.1 実験的な目的と特徴的な値の定義

特性値: はんだ貼り付けのミスレジストレーション (ユニット: mm)

特性タイプ: より小さい

-

測定機器: あおい (自動光学検査)

-

測定方法: 各組み合わせに対して, 測定 10 ボード. 各ボードで, 5つのはんだペーストの誤解を測定します 0402 コンポーネントパッド, そして、その委員会の誤った登録として最大値を取る.

-

計算方法: 全体での平均誤解値の値 10 ボードは、そのパラメーターの組み合わせの誤った登録値と見なされます.

2.2 固定要因と実験的要因の選択

固定係数:

-

ボードタイプ: ロックレイク (インテル)

-

生産ライン: ライン 14

-

ステンシル: 全体に使用されているのと同じステンシル

-

スキージ: 全体で使用されている同じスクイジーセット

-

機械的状態: 機器はメンテナンスを受けています

実験的要因:

-

因子a: 真空保持時間 (保留時間の期間を調整することにより、真空力レベルを制御します)

-

因子b: コンベアレール幅 (幅を調整して保護します プリント基板 動きを防ぎます)

-

因子c: スキージの圧力

-

因子d: 印刷速度

-

因子e: 金型マーク間の距離

-

実験結果と分析

実験は2つの段階で実施されました: 最初の段階では、重要な要因についてスクリーニングされました, また、第2段階では、パラメーターの組み合わせを最適化しました.

3.1 ステージ1の結論

重要な因子効果: あ, 広告 (交流), CD (交流), E

ステージ2で選択された要因: あ, C, D, E

非常に重要な要因: あ, 広告, CD

予期しない発見: 因子b (コンベアレール幅), 当初は非常に影響力があると考えられていました, 有意な効果は示されませんでした. 最も重要な効果は、相互作用効果でした.

3.2 ステージ2の実験とANOVA分析

ANOVAの結果は、因子a, C, そして、Dは第2段階では有意ではありませんでした. これは、観察された主なバリエーションがランダムエラーによるものであることを示唆しています, パラメーターの最適化がほぼ最適レベルに達したことを示しました.

-

最適なプロセスパラメーターと標準化

実験結果に基づいています, 最適な生産プロセスパラメーターが決定されました:

テーブル 1: 改善前後のプロセスパラメーターの比較

| パラメーター | 事前改善 | ポスト改善 | 変化 |

|---|---|---|---|

| スキージの圧力 | 6.0 KG | 5.4 KG | 減少 10% |

| 印刷速度 | 40 mm/sec | 50 mm/sec | 増加 25% |

| 真空保持時間 | 0.4 秒 | 0.4 秒 | 変更はありません |

| 法律上のマーク距離 | 361.9 | 361.9 | 変更はありません |

| コンベアレール幅 | 244.3 | 244.3 | 変更はありません |

選択されたパラメーターの組み合わせの理論的根拠:

-

因子a (真空保持時間): 選択 0.4 プリンター時間の損失を最小限に抑えるために、0.4〜0.8秒の範囲内の秒.

-

因子c (スキージの圧力): より低いレベルを選択しました 5.4 KG, 過度の圧力がステンシルの変形を引き起こし、はんだ貼り付け貼り付けを引き起こす可能性があるため.

-

因子d (印刷速度): 選択 50 mm/sec, 高速でははんだペーストのリリースが不十分になる可能性があるため.

-

利益の評価とコスト分析

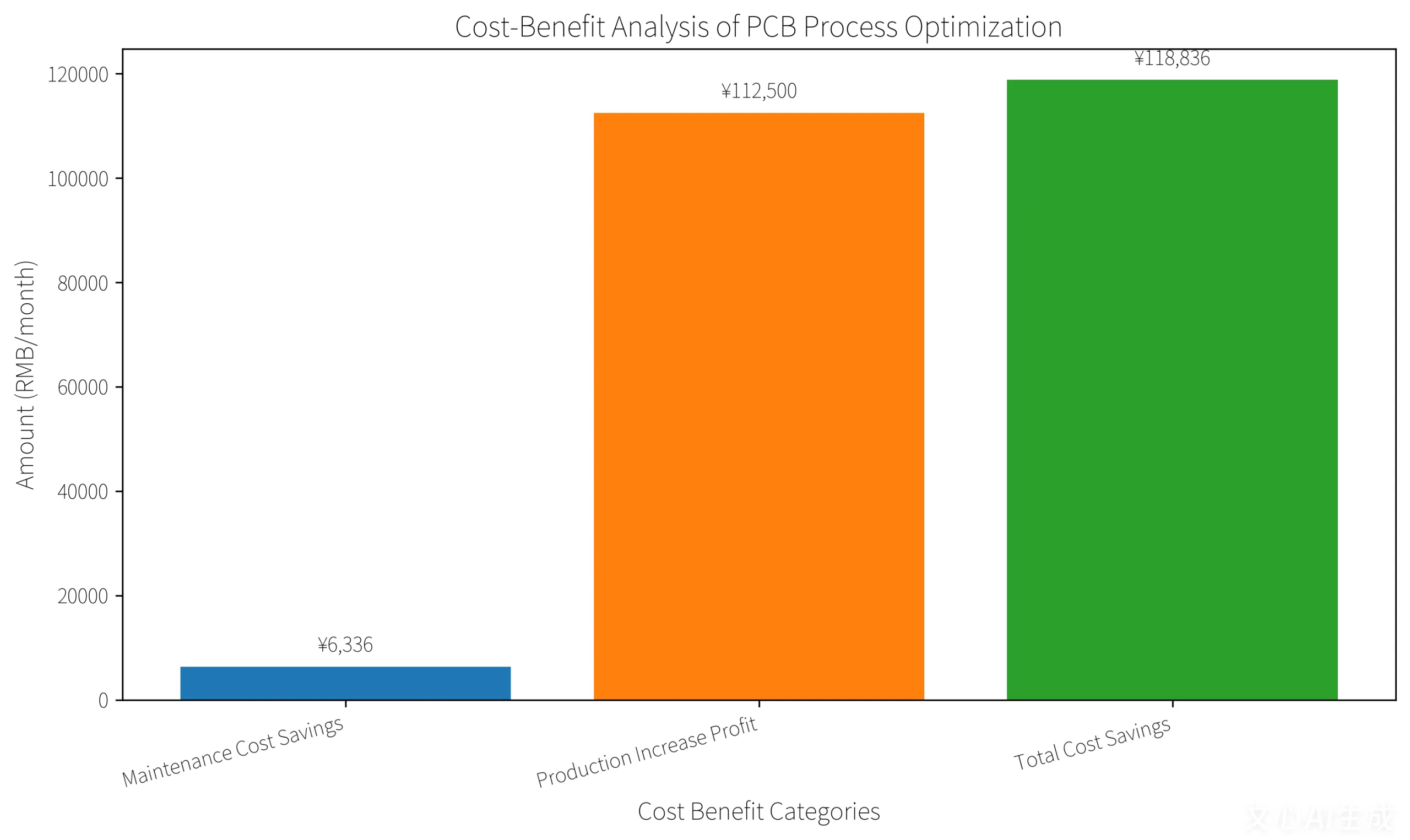

プロセスパラメーターの最適化後, 大きな経済的利益と品質改善が達成されました:

5.1 品質改善の結果

墓の欠陥率は減少しました 29% に 18%, an 11 パーセンテージポイント削減. IPC-7912標準に従って計算されます, プロセス機能インデックスCPから改善されました 0.89 に 1.32, CPKは改善されました 0.72 に 1.08.

5.2 経済的利益計算

-

コストの節約をやり直します: 66 1週間あたりSMTラインあたりの欠陥ボードが少ない. で 2 ボードごとに数分のリワーク:

労働貯蓄= 66 ボード× 2 min/board× 8 線× 4 週= 4224 最小/月

コスト削減= 90 rmb/hour× (4224 / 60) = 6,336 人民元/月 -

出力は利益を増やします: 事前改善, ミスレジストレーションのプリンター調整には約でした. 5 最小ライン/日:

労働貯蓄= 5 最小/日× 30 日× 8 行= 1200 最小/月

出力は利益を増やします= (1200 / 60 / 24) × 1500 ボード/日× 90 rmb/board = 112,500 人民元 -

毎月の総コスト削減 = 6,336 + 112,500 = 118,836 人民元

-

フルプロセス品質制御システムの構築

墓の問題に徹底的に対処する, すべての段階をカバーする包括的な品質保証システムを確立することが不可欠です: 着信材料→処理型生産→最終製品検査→販売後の故障分析.

6.1 着信品質管理 (IQC)

IQCは最初のチェックポイントです. PCB銅箔などの主要な原材料 基質 外観と寸法のサンプリング検査が必要です: 銅箔の表面には酸化がない必要があります, ピンホール, そして傷; 基質の厚さ耐性は、±0.05mm標準を満たす必要があります.

6.2 インプロセスの品質管理 (IPQC)

IPQCは、PCB製造プロセス全体に及びます, と “品質のチェックポイント” 各キー操作の後. 内層イメージングの後, トレースの幅/間隔とエッチングの均一性を点検します; 積層後, X線検査を使用して、層間層のボイドとミスレギスト化を確認する; メッキ後, 銅の厚さテスターを使用して、穴と表面の銅の厚さを測定する.

6.3 最終的な品質管理 (FQC)

FQCは、出荷前の最終テストです, 3つの主要な寸法をカバーします: 外観, 電気性能, と信頼性. 外観のために, 手動検査とAOI検査の組み合わせを使用します; 電気的に, 実行する 100% 開閉やショートパンツを確保するためのフライングプローブまたはベッドオブネイルテスト; 信頼性のため, 顧客の要件に基づいて環境テストを実施します.

-

PCB設計最適化の推奨

プロセスの最適化を超えて, PCBの設計最適化は、墓の筋肉の欠陥を防ぐために重要です.

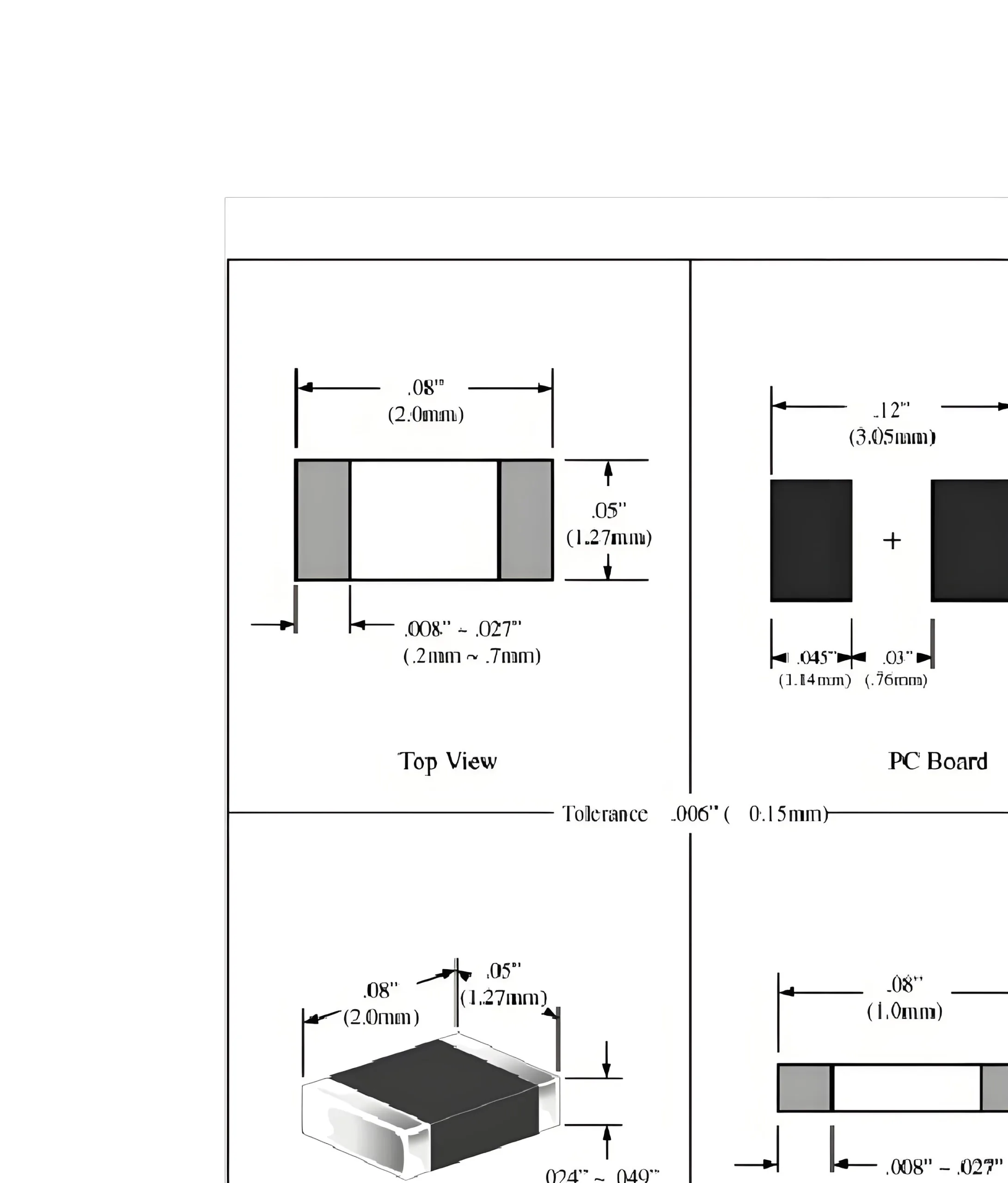

7.1 パッド設計基準

土地パターンの設計を最適化する - 適切なパッド拡張寸法を確保する. パッドの端があるシナリオを避けてください (直線) 45°を超える湿潤角を形成します. IPC-7351標準によると, のために 0402 コンポーネント, パッド間隔は0.35±0.05mm以内に制御する必要があります, パッド幅は0.5±0.05mmでなければなりません.

7.2 レイアウト最適化戦略

コンポーネントのレイアウトが不十分な場合、 コンポーネント PCBで. リフローはんだ中に, これにより、温度差が過剰になります, コンポーネントの両側の不均一な加熱, とトゥームストンリング. 設計中に高出力デバイスの隣に小さなコンポーネントを配置しないようにして、均一な熱分布を確保する.

-

フォローアップアクションと継続的な改善

改善の持続可能性を確保するために、以下の措置が実施されました:

8.1 継続的な監視と統計分析

の墓の収量データを継続的に収集します 30 日, 監視のためにコントロールチャートを利用します, 持続的な改善の有効性を確認します. 10月のデータは、重大な持続的な改善を示しました, 登録に継続的なプラスの効果があります.

8.2 因果分析と制御基準

改善結果に基づいています, 登録と墓石の因果関係を研究します, 制御基準を確立します, それらを毎日の管理に統合します. 実装a “品質トレーサビリティコード” 各PCBに対して, 原材料バッチなどの記録情報, 生産機器, 検査データ, およびオペレーター.

8.3 拡張と技術の転送

このDOEの調査結果を他の生産ラインや製品モデルに拡張します. プロセスパラメーターデータベースを確立します, 実証済みのソリューションのパラメーターを標準化します, 新しいプログラムのデバッグ時間を短縮します 24 営業時間 3 時間.

-

結論と見通し

DOE方法論の使用, はんだ貼り付けのミスレジュレーションに影響を与える主要なプロセスパラメーターを正常に特定し、からの墓の筋肉の欠陥率を減らしました 29% に 18% パラメーター最適化を通じて. これにより、毎月のコスト削減が約118,836円になります, 約1.426百万円の年間貯蓄に翻訳します.

将来を見据えて, プロセス研究をさらに深めます, プロセスパラメーターの最適化におけるAIテクノロジーの適用を探る, インテリジェントプロセス最適化システムを構築します, 製品の品質と生産効率の継続的な改善を達成します.

新製品の紹介ニーズを持つ電子機器メーカー向け, UGPCBのようなワンストップソリューションプロバイダーを選択することをお勧めします, PCB設計を統合します, 製造業, プリント基板, そして PECVD サービス. 設計段階からのPCBおよびPCBAプロセス中の潜在的な問題を検討します, さまざまなシミュレーションテストを実施します, 入ってくる材料からテストとパッケージングまで、フルプロセスの品質管理システムを実装する, 製品の品質の安定性と一貫性を確保します.

UGPCBのロゴ

UGPCBのロゴ