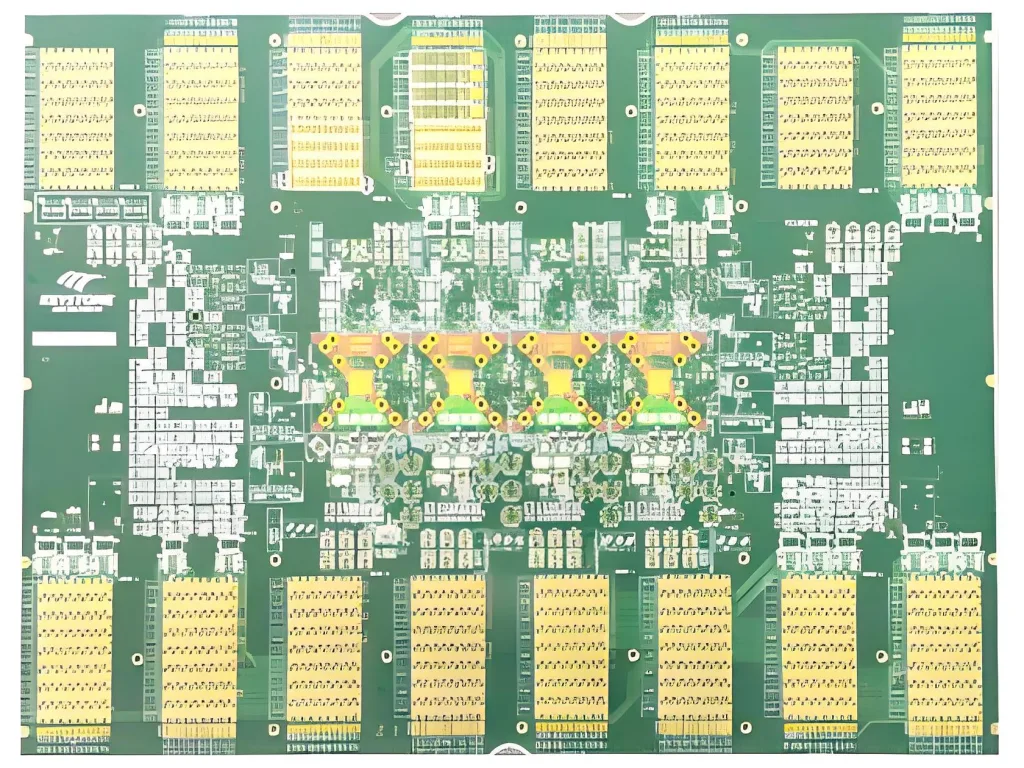

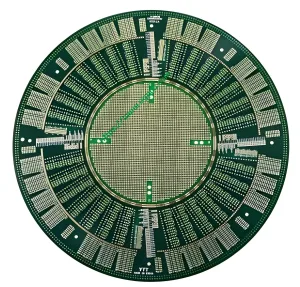

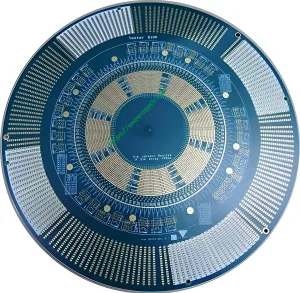

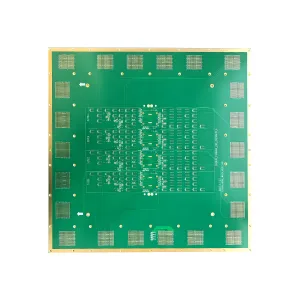

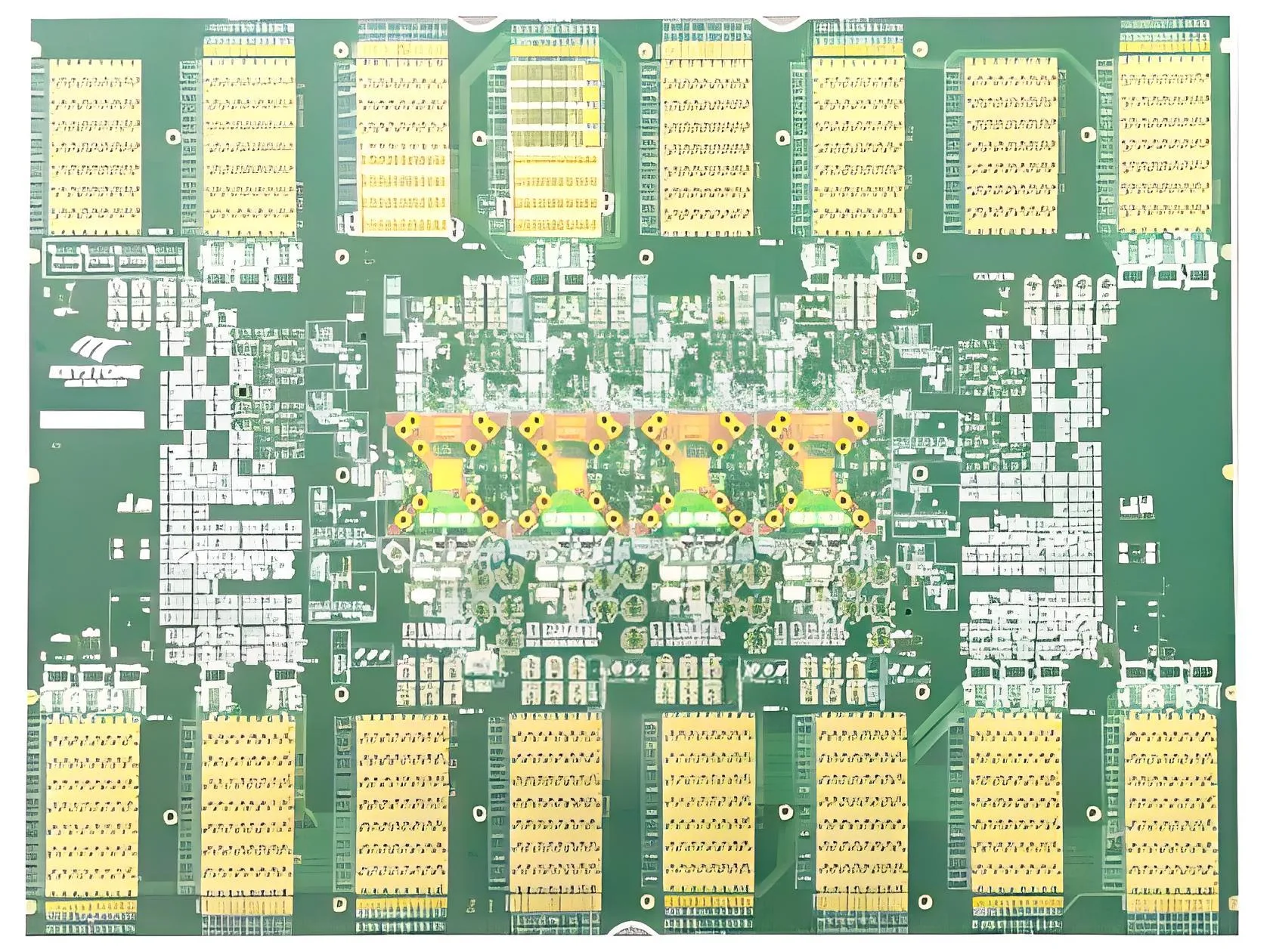

Overview of the 62-Layer ATE Load PCB

The 62-Layer ATE Load PCB is a high-performance, ultra-high-density printed circuit board engineered for Automated Test Equipment (ATE) systems. Designed to handle complex signal routing and high-power loads, it meets rigorous testing requirements in semiconductor manufacturing and advanced electronics validation.

Key Definition

An ATE Load PCB is a specialized circuit board that simulates real-world operating conditions for testing integrated circuits (ICs) and electronic components. The 62-layer configuration supports intricate signal paths, power distribution, and thermal management in compact designs.

Critical Design Parameters

-

Layer Count: 62 layers for multi-domain signal isolation and power plane optimization.

-

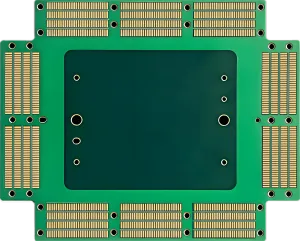

Dimensions: 16.9″ × 22.9″ (large format for multi-device integration).

-

Thickness: 250 mil (balances rigidity and thermal dissipation).

-

Material: FR4 HTg (high-temperature glass epoxy for stability up to 180°C).

-

Minimum Hole Size: 8 mil (supports high-density interconnects).

-

BGA Pitch: 0.65mm (enables fine-pitch component mounting).

-

Aspect Ratio: 32:1 (ensures reliable plating in microvias).

-

Drill-to-Copper: 7 mil (prevents short circuits).

-

POFV & Back-Drilling: Eliminates signal distortion in high-frequency applications.

-

Surface Finish: ENEG (Electroless Nickel Electroless Gold for corrosion resistance).

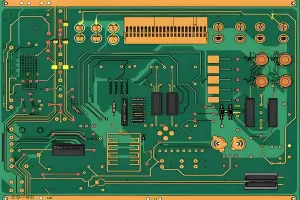

Core Functionality

The PCB routes test signals between ATE systems and devices under test (DUTs), ensuring accurate voltage/current measurements. Back-drilling removes unused via stubs to minimize signal reflections, while POFV (Plated Over Filled Vias) enhances thermal conductivity and structural integrity.

Primary Applications

-

Semiconductor Testing: Validates ICs, CPUs, and memory modules.

-

Aerospace & Defense: Mission-critical avionics and radar systems.

-

Telecom Infrastructure: High-speed data transmission equipment.

-

Medical Devices: Precision diagnostic and imaging tools.

Material Advantages

FR4 HTg provides:

-

Thermal Resilience: Stable performance under cyclic thermal stress.

-

Low Dielectric Loss: Critical for high-frequency signal integrity.

-

Mechanical Strength: Resists warping during multilayer lamination.

Structural Features

-

Hybrid Stackup: Combines high-speed, power, and ground layers.

-

Microvia Technology: Laser-drilled microvias (8 mil) enable dense interlayer connections.

-

Controlled Impedance Traces: Minimizes crosstalk in 0.65mm BGA layouts.

Performance Highlights

-

Signal Integrity: <3% insertion loss at 10 GHz.

-

Power Handling: Supports 20A per power plane.

-

Thermal Management: 1.2 W/mK thermal conductivity via POFV.

Manufacturing Workflow

-

Material Prep: Cut FR4 HTg cores and prepreg sheets.

-

Laser Drilling: Create 8-mil microvias with ±1 mil tolerance.

-

Plating & POFV: Electroplate vias and fill with conductive epoxy.

-

Back-Drilling: Remove excess via stubs using depth-controlled drills.

-

Lamination: Press 62 layers under high temperature/pressure.

-

Surface Finish: Apply ENEG for solderability and oxidation resistance.

-

Testing: Validate impedance, continuity, and thermal cycling.

Ideal Use Cases

-

High-Frequency ATE Systems: Tests 5G RF components and millimeter-wave devices.

-

Multi-Site Testing: Parallel validation of 16+ DUTs on a single board.

-

Harsh Environments: Oil/gas exploration sensors and automotive ECU testing.

UGPCB LOGO

UGPCB LOGO