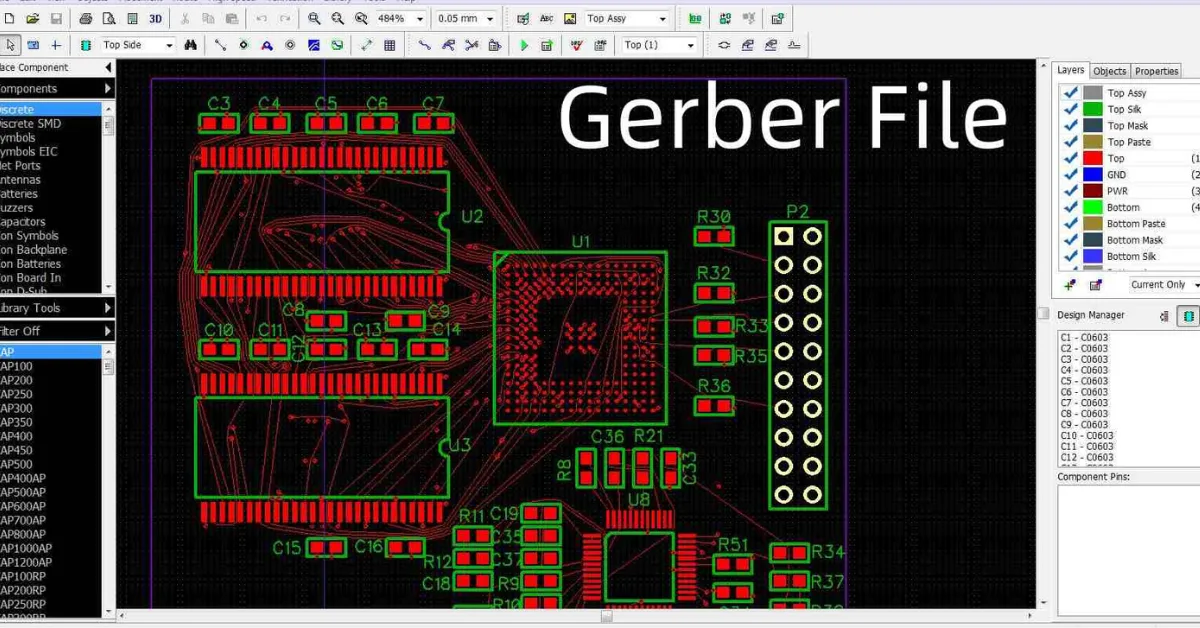

Introducere: Gerber Files – The DNA of PCB Manufacturing

În design PCB de mare viteză, Gerber files encapsulate over 90% of manufacturing data. According to IPC-2581 standards, 85% of global Producătorii de PCB-uri rely on Gerber as primary production documentation. As the “industrial blueprint” of electronics, Gerber files precisely describe a circuit board’s physical structure through layered encoding. This guide decodes each layer’s engineering significance to help you master Fabricarea PCB.

Section 1: Complete Gerber File Export Workflow

1.1 Pre-Export Verification

-

DRC Validation: Ensure spacing compliance with IPC-2221 standards (Min. trace/space = 0.1mm @ 6-layer PCB -uri)

-

Stackup Confirmation: Impedance control must satisfy:

Unde H = dielectric thickness, W = lățimea urmei, T = copper thickness (1 oz = 35µm).

1.2 Export Mode Comparison

| Metodă | Use Case | File Completeness |

|---|---|---|

| One-Click Export | Standard 4-6 layer PCBs | 95% |

| Custom Configuration | PCB-uri HDI / Blind/Buried Vias | 100% |

Section 2: Gerber Layer Structure Deep Dive

2.1 Conductive Layers Explained

Copper Layers:

-

Top/Bottom Layer: Surface routing (Typ. 1 oz copper)

-

Inner Layers: 6-layer PCB stackup: Top-GND-Signal-Power-Signal-Bottom

Drill Layers:

2.2 Process-Supporting Layers

Strat de masca de lipit:

-

Negative image output (Exposes copper openings)

-

Min. clearance: 0.07mm (Prevents solder mask bridging failure)

Paste Mask Layer:

-

Stencil aperture = Pad size × 90%

-

QFN packages require cross-bridge anti-solder bead design

Strat de serigrafie:

-

Text height ≥0.8mm, line width ≥0.15mm

-

Bottom layer silkscreen requires mirroring

Section 3: Gerber Features in Multilayer PCBs

3.1 Layer Count vs. Gerber Files

| Straturi de PCB | Gerber Files | Special Requirements |

|---|---|---|

| 1-2 | 8-10 | Standard through-holes |

| 4-6 | 15-20 | Impedance control + VIPPO |

| 8+ | 25+ | Blind vias + hybrid stacking |

3.2 Advanced Process Implementation

VIPPO (Via-in-Pad):

-

Hole diameter ≤0.15mm, pad size ≥0.3mm

-

Label as “μVia” in drill layers

Stepped Slot Design:

-

MechanicalLayer annotation:

SLOT:3.0x1.2mm @ Layer2-4

Section 4: DFM Rules Driven by Gerber Data

4.1 Manufacturability Checks

4.2 High-Speed Design Markers

-

Differential pairs:

IMPEDANCE:100Ω±10% -

RF traces:

NO_SOLDERMASK(Reduces Dk variation)

Section 5: From Layout Engineer to PCB Architect

True PCBA design experts master:

5.1 Integritatea semnalului (SI)

-

Delay control: ΔL ≤ 0.05√ε_r (ps/inch)

-

Crosstalk prevention: 3W rule (Spacing ≥ 3×trace width)

5.2 Power Integrity (Pi)

-

Target impedanță:

-

Decoupling capacitor layout: Radial placement by capacitance

5.3 Managementul termic

-

Copper current capacity:

I=0.048⋅ΔT0.44⋅A0.725

(ΔT = temperature rise, A = cross-section)

Concluzie: The Engineering Philosophy of Gerber Files

When exporting Gerber data, remember: These “cold” layers represent precision dialogues between electronics and materials science. From 0.05mm laser drills to 10μm solder mask tolerances, each Gerber layer narrates the engineering philosophy of signal isolation and conductive pathways.

Industry data reveals: Using Gerber+ODB++ dual-file delivery increases first-pass yield by 40%. In the 5G/AI era, mastering Gerber semantics means controlling the core of intelligent hardware manufacturing.