Р’РІРөРҙРөРҪРёРө: Р’РҫР№РҪР° РІ миллимРөСӮСҖРҫРІРҫРј РјР°СҒСҲСӮР°РұРө РІ РҙизайРҪРө РҝРөСҮР°СӮРҪСӢС… РҝлаСӮ DDR5

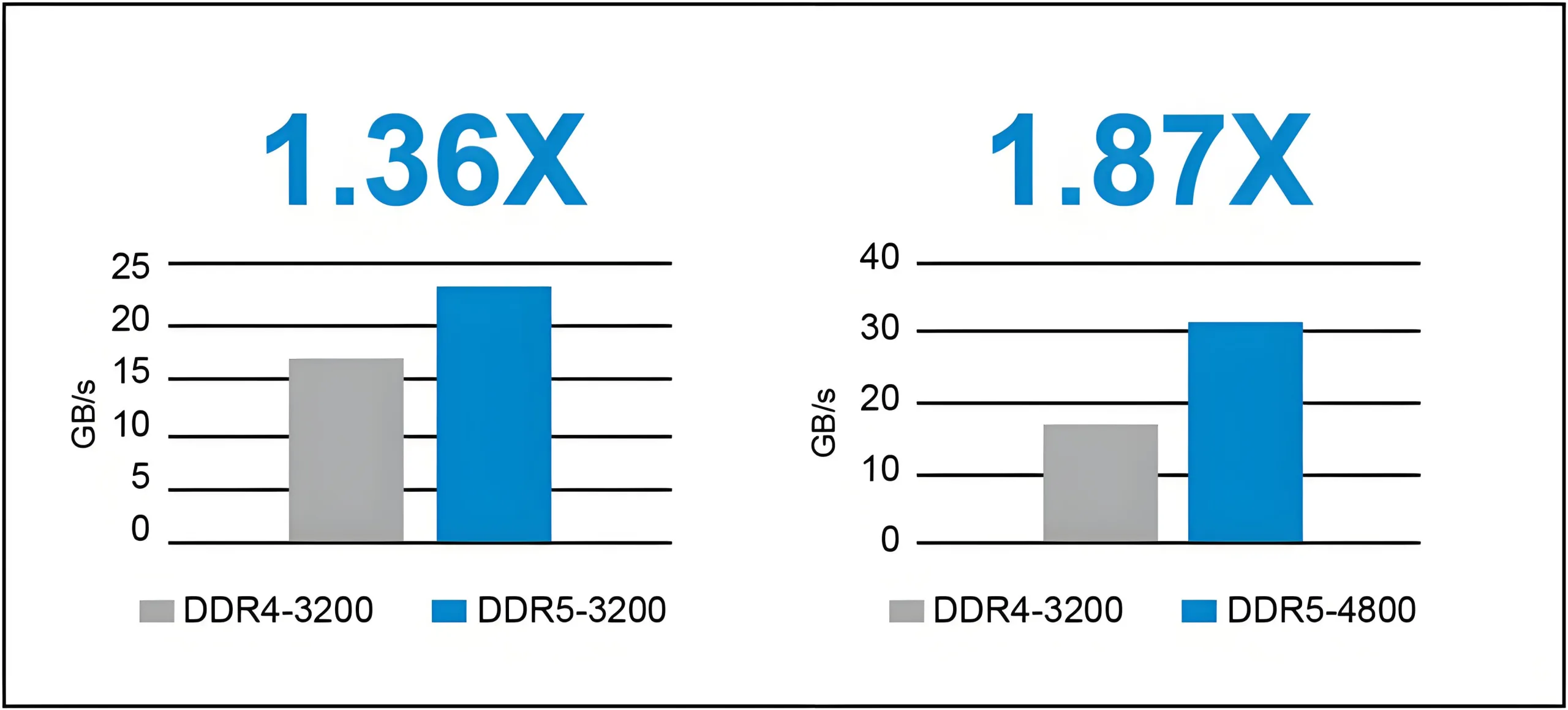

РҹСҖСӢР¶РҫРә РҫСӮ DDR4 РҪР° DDR5 РҫСӮРјРөСҮР°РөСӮ СҒРјРөРҪСғ РҝР°СҖР°РҙРёРіРјСӢ: РЎРәРҫСҖРҫСҒСӮСҢ СҒРёРіРҪала РІСҒРҝР»СӢла РҫСӮ 3,200 РңРў/СҒ 6,400 MT/S РҝСҖРё СҖР°РұРҫСҮРёС… РҪР°РҝСҖСҸР¶РөРҪРёСҸС… РҝР°РҙР°РөСӮ РҙРҫ 1,1 Р’. РӯСӮР° РҙРІРҫР№РҪР°СҸ Р·Р°РҙР°СҮР° СӮСҖР°РҪСҒС„РҫСҖРјРёСҖСғРөСӮСҒСҸ РҝРөСҮР°СӮРҪР°СҸ РҝлаСӮР° РңР°СҖСҲСҖСғСӮРёР·Р°СҶРёСҸ РҫСӮ РҝСҖРҫСҒСӮРҫР№ РёРҪР¶РөРҪРөСҖРёРё РҝРҫРҙРәР»СҺСҮРөРҪРёСҸ РІ СӮРҫСҮРҪСғСҺ РІРҫР№РҪСғ РІ миллимРөСӮСҖРҫРІРҫРј РјР°СҒСҲСӮР°РұРө. РһСӮСҖР°СҒР»РөРІСӢРө РҙР°РҪРҪСӢРө РҝРҫРәазСӢРІР°СҺСӮ, СҮСӮРҫ 80% СҒРұРҫРөРІ РҙизайРҪР° DDR5 РІРҫР·РҪРёРәР°РөСӮ РёР· -Р·Р° РҝСҖРҫРұР»РөРј РјР°СҖСҲСҖСғСӮРёР·Р°СҶРёРё, СҒ 90% РҹСҖРөРҙРҫСӮРІСҖР°СүРөРҪРҫ СҒ РҝРҫРјРҫСүСҢСҺ РјРҫРҙРөлиСҖРҫРІР°РҪРёСҸ РҝРөСҖРөРҙ лайРөР№СӮРҫРј. РӯСӮР° СҒСӮР°СӮСҢСҸ Р°РҪализиСҖСғРөСӮ РҝСҸСӮСҢ РәСҖРёСӮРёСҮРөСҒРәРёС… РҫСҲРёРұРҫРә РјР°СҖСҲСҖСғСӮРёР·Р°СҶРёРё DDR5, РҝРҫРҙРҙРөСҖживаРөСӮСҒСҸ СҚРјРҝРёСҖРёСҮРөСҒРәРёРјРё РҙР°РҪРҪСӢРјРё Рё СӮРөРјР°СӮРёСҮРөСҒРәРёРјРё РёСҒСҒР»РөРҙРҫРІР°РҪРёСҸРјРё, РҹСҖРөРҙРҫСҒСӮавлРөРҪРёРө РҙРөР№СҒСӮРІРөРҪРҪСӢС… СҖРөСҲРөРҪРёР№ РҙР»СҸ РҝСҖРҫС„РөСҒСҒРёРҫРҪалРҫРІ РҝРөСҮР°СӮРҪРҫР№ РҝлаСӮСӢ.

1. DDR5 РӨРёР·РёСҮРөСҒРәРёРө С…Р°СҖР°РәСӮРөСҖРёСҒСӮРёРәРё: РҹРҫСҮРөРјСғ СӮСҖР°РҙРёСҶРёРҫРҪРҪСӢРө РјРөСӮРҫРҙСӢ РҝСҖРҫРөРәСӮРёСҖРҫРІР°РҪРёСҸ РҝРөСҮР°СӮРҪСӢС… РҝлаСӮ СӮРөСҖРҝРёСӮ РҪРөСғРҙР°СҮСғ

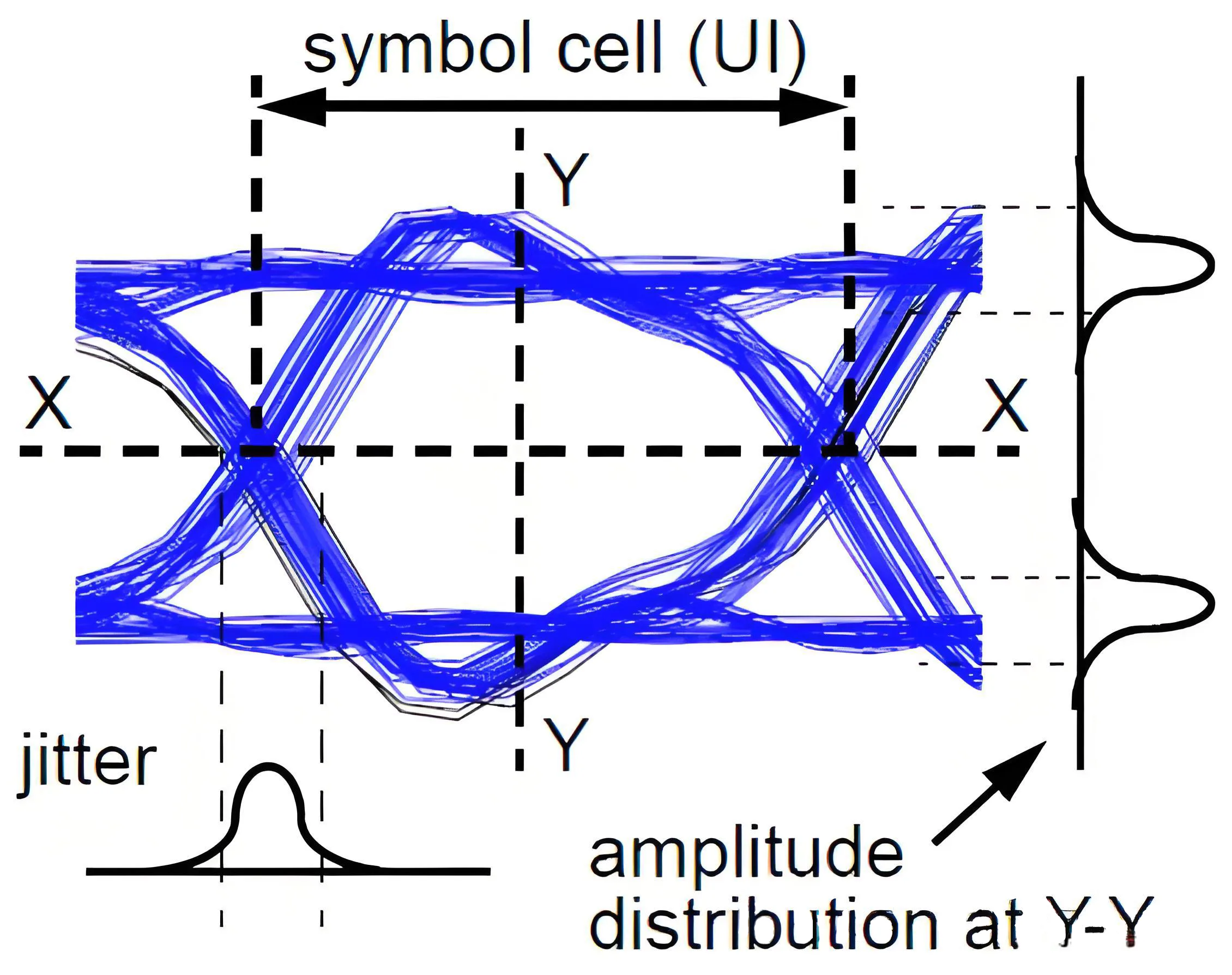

1.1 РЎРәРҫСҖРҫСҒСӮСҢ СҒРёРіРҪала Рё СҖРөРІРҫР»СҺСҶРёСҸ РҝРҫР»РҫСҒСӢ РҝСҖРҫРҝСғСҒРәР°РҪРёСҸ

ДлСҸ DDR5-6400, РӯффРөРәСӮРёРІРҪР°СҸ СӮР°РәСӮРҫРІР°СҸ СҮР°СҒСӮРҫСӮР° РҙРҫСҒСӮРёРіР°РөСӮ 3,200 РңР“СҶ, СҒ СӮР°РәРёРјРё Р¶Рө РҝРҫРәазаСӮРөР»СҸРјРё СӮР°Рә Р¶Рө РұСӢСҒСӮСҖРҫ, РәР°Рә 0.5 РҝСҒР° (20-80% РІСҖРөРјСҸ РҝРҫРҙСҠРөРјР°). РӯСӮРҫ СӮСҖРёРіРіРөСҖСӢ:

-

РӯффРөРәСӮ РҫСӮСҸРіСҮР°РҪРёСҸ РәРҫжи: Р’СӢСҒРҫРәРҫСҮР°СҒСӮРҫСӮРҪСӢРө СӮРҫРәРё РәРҫРҪСҶРөРҪСӮСҖРёСҖСғСҺСӮСҒСҸ РҪР° РҝРҫРІРөСҖС…РҪРҫСҒСӮСҸС… РҝСҖРҫРІРҫРҙРҪРёРәР°, СғРјРөРҪСҢСҲРөРҪРёРө СҚффРөРәСӮРёРІРҪРҫР№ СӮРҫР»СүРёРҪСӢ РјРөРҙРё РҙРҫ 0.66 РјРәРј РІ 10 ГГСҶ.

-

ДиСҚР»РөРәСӮСҖРёСҮРөСҒРәР°СҸ РҝРҫСӮРөСҖРё СҚСҒРәалаСҶРёСҸ: FR4 СҒСғРұСҒСӮСҖР°СӮР° РҝСҖРҫСҸРІРёСӮСҢ РҝРҫСӮРөСҖСҺ РәР°СҒР°СӮРөР»СҢРҪРҫР№ (Дф) РёР· 0.02 РІ 10 ГГСҶ, РІСӢР·СӢРІР°СҺСүРёР№ >3 ДБ/РҙСҺР№РјРҫРІРҫРө РҫСҒлаРұР»РөРҪРёРө СҒРёРіРҪала.

РҹСҖРҫРІРөСҖРәР° С„РҫСҖРјСғР»СӢ (ГлСғРұРёРҪР° РәРҫжи):

Р’ F = 10 ГГСҶ, О”вүҲ0,66 РјРәРј,РҫСҒСӮавлСҸСҸ СӮСҖР°РҙРёСҶРёРҫРҪРҪСғСҺ РјРөРҙРҪСғСҺ РјРөРҙСҢ (35 РјРәРј) СҒ <2% РҳСҒРҝРҫР»СҢР·РҫРІР°РҪРёРө.

2. РҹСҸСӮСҢ РјР°СҖСҲСҖСғСӮРёР·Р°СҶРёРё DDR5 Minefields and Countermeres

2.1 РңРёРҪРҪРҫРө РҝРҫР»Рө 1: РһСҲРёРұРәР° РІСҖРөРјРөРҪРё - РҝРҫСҖРҫРі РІСӢживаРҪРёСҸ Вұ 15 Р».СҒ.

ВлиСҸРҪРёРө: РқРөСҒРҫРҫСӮРІРөСӮСҒСӮРІРёРө РҙлиРҪСӢ 5 РјРёР»СҢ РІРІРҫРҙРёСӮ Р·Р°РҙРөСҖР¶РәСғ Вұ 12 Р».СҒ., РҫРұСҖСғСҲРёРІР°СҸ РіРҫСҖРёР·РҫРҪСӮалСҢРҪСғСҺ СҲРёСҖРёРҪСғ глаз РҝРҫ 30%.

РўРөРјР°СӮРёСҮРөСҒРәРҫРө РёСҒСҒР»РөРҙРҫРІР°РҪРёРө: ДизайРҪ РіСҖафиСҮРөСҒРәРҫРіРҫ РҝСҖРҫСҶРөСҒСҒРҫСҖР° РҝРҫСҒСӮСҖР°Рҙал РҫСӮ РҙРөРіСҖР°РҙР°СҶРёРё BER РҫСӮ 10вҲ’12 Рә 10вҲ’7 РҳР·-Р·Р° 8 РјРёР»СҢ DQ/DQS РҝРөСҖРөРәРҫСҒРё.

Р РөСҲРөРҪРёСҸ:

-

3D РңР°СҖСҲСҖСғСӮРёР·Р°СҶРёСҸ РәРҫРјРҝРөРҪСҒР°СҶРёРё: ЗамРөРҪРёСӮСҢ 90 В° извилиСҒСӮСӢС… СҒСҖРөРҙСҒСӮРІ РҪР° 45 В° СҒРөСҖРҝРөРҪСӮРёРҪР°, СҒРҪРёР¶РөРҪРёРө РҝР°СҖазиСӮРёСҮРөСҒРәРҫР№ РөРјРәРҫСҒСӮРё 30%.

-

ДиРҪамиСҮРөСҒРәР°СҸ РәалиРұСҖРҫРІРәР° РІСҖРөРјРөРҪРё: Р’СӢРҝРҫР»РҪРёСӮСҢ РјРҫРҙРөлиСҖРҫРІР°РҪРёРө РңРҫРҪСӮРө -РҡР°СҖР»Рҫ (РҡР°РҙРөРҪСҒ РЎРёРіСҖафиСҸ) РҝРҫРәСҖСӢСӮРёРө Вұ 10% РІР°СҖРёР°СҶРёР№ РҝСҖРҫСҶРөСҒСҒР°.

РӨРҫСҖРјСғла (Р’СҖРөРјСҸ РјР°СҖжа):

РўРҙРҫРҝСғСҒРә= РўСҶРёРәР»-(РўСҒРҫРҝСғСӮСҒСӮРІСғСҺСүРёР№+РўРҝРҫР»РөСӮ+ТДжаРҪРёСӮРөСҖ)

ДлСҸ DDR5-6400 (РўСҶРёРәР»= 0,3125 ), РЎРёСҒСӮРөРјРҪСӢРө РҫРҝРҫРІРөСүРөРҪРёСҸ СӮСҖРёРіРіРөСҖ, РәРҫРіРҙР° РўРҙРҫРҝСғСҒРә<50 РҝСҒР°.

2.2 РңРёРҪРҪРҫРө РҝРҫР»Рө 2: Р Р°СҒРҝСӢР»РөРҪРёРө РёРјРҝРөРҙР°РҪСҒР° - СҶСғРҪами СҒРёРіРҪала 5 РһРј

Р РёСҒРә: Р§РөСҖРөР· РҪРөСҒРҫРҫСӮРІРөСӮСҒСӮРІРёРө РёРјРҝРөРҙР°РҪСҒР° РҝСҖРёСҮРёРҪ >15 РҹРҫСӮРөСҖСҸ Рҫ РІРҫР·РІСҖР°СӮРө БД, СҖазСҖСғСҲР°СҸ РІРөСҖСӮРёРәалСҢРҪСғСҺ РІСӢСҒРҫСӮСғ глаз 40%.

ДаРҪРҪСӢРө: РҡажРҙСӢР№ РҪРөРҝСӮРёРјРёР·РёСҖРҫРІР°РҪ СҮРөСҖРөР· РҙРҫРұавлРөРҪРёРө 0.2 РҹРҫСӮРөСҖСҸ РІСҒСӮавРәРё DB РҝСҖРё 5 ГГСҶ.

Р РөСҲРөРҪРёСҸ:

-

Р§РөСҖРөР· СҖРөРІРҫР»СҺСҶРёСҺ: Р РөализРҫРІР°СӮСҢ лазРөСҖРҪСӢРө СҒР»РөРҝРҫР№ вайи (вүӨ4mil) СҒ РәРҫРјРҝРөРҪСҒР°СҶРёРөР№ Р°РҪСӮРёРҝР°РҙСӢ, РһРіСҖР°РҪРёСҮРёРІР°СҺСүРөРө РёР·РјРөРҪРөРҪРёРө РёРјРҝРөРҙР°РҪСҒР° РҙРҫ Вұ 3 РһРј.

-

РһРҝСӮРёРјРёР·Р°СҶРёСҸ РҪР°РәлаРҙРәРё: РҳСҒРҝРҫР»СҢР·СғР№СӮРө СҚллиРҝСӮРёСҮРөСҒРәРёРө РҝСҖРҫРәлаРҙРәРё (1.5:1 РЎРҫРҫСӮРҪРҫСҲРөРҪРёРө СҒСӮРҫСҖРҫРҪ) Р§СӮРҫРұСӢ СғРјРөРҪСҢСҲРёСӮСҢ РөРјРәРҫСҒСӮРҪСӢРө СҚффРөРәСӮСӢ 20%.

РӨРҫСҖРјСғла (Р§РөСҖРөР· РјРҫРҙРөР»СҢ РёРјРҝРөРҙР°РҪСҒР°):

ZviaвүҲ87ПөrttrnвҒЎ(5.98СҮР°СҒ/(0.8D1+D2))

Р“РҙРө : ДиСҚР»РөРәСӮСҖРёСҮРөСҒРәР°СҸ СӮРҫР»СүРёРҪР°, D1: СҮРөСҖРөР· РҙиамРөСӮСҖ, : ДиамРөСӮСҖ РҝСҖРҫРәлаРҙРәРё.

2.3 РңРёРҪРҪРҫРө РҝРҫР»Рө 3: Р—Р°РҙРөСҖР¶РәР° РјРөР¶СҒР»РҫР№РҪРҫРіРҫ-СҚффРөРәСӮ РұР°РұРҫСҮРәРё 0,1 Р».СҒ./РјРј

РӯффРөРәСӮ РҝР»РөСӮРөРҪРёСҸ РІРҫР»РҫРәРҪР°: ДиСҚР»РөРәСӮСҖРёСҮРөСҒРәРҫРө РҝРҫСҒСӮРҫСҸРҪРҪРҫРө РёР·РјРөРҪРөРҪРёРө (О”ПөR = 0,3) РҳР· РҝРөСҖРёРҫРҙРёСҮРҪРҫСҒСӮРё СҒСӮРөРәР»СҸРҪРҪРҫРіРҫ РІРҫР»РҫРәРҪР° РІСӢР·СӢРІР°РөСӮ 0.6 РҹСҒ/РҙСҺР№Рј Р·Р°РҙРөСҖР¶РәР° РҝРөСҖРөРәРҫСҒР°.

Р РөСҲРөРҪРёСҸ:

-

Р’СӢСҖавРҪРёРІР°РҪРёРө РҫСҒРё Z.: РЎРёРіРҪалСӢ РұайСӮРҫРІСӢС… РіСҖСғРҝРҝ РјР°СҖСҲСҖСғСӮР° РҝРҫРҙ СғРіР»РҫРј Вұ 45 В° РҙР»СҸ РҫСӮРјРөРҪСӢ РҙРёСҚР»РөРәСӮСҖРёСҮРөСҒРәРҫР№ Р°РҪРёР·РҫСӮСҖРҫРҝРёРё.

-

РңРөР¶СҒР»РҫР№РҪР°СҸ РәРҫРјРҝРөРҪСҒР°СҶРёСҸ: РҹСҖРөРҙРІР°СҖРёСӮРөР»СҢРҪР°СҸ загСҖСғР·РәР° DAC/DF DATA РІ РёРҪСҒСӮСҖСғРјРөРҪСӮСӢ EDA РҙР»СҸ авСӮРҫРјР°СӮРёСҮРөСҒРәРҫР№ РәРҫСҖСҖРөРәСҶРёРё Р·Р°РҙРөСҖР¶РәРё.

2.4 РңРёРҪРҪРҫРө РҝРҫР»Рө 4: РЎРёР»РҫРІР°СҸ РҝСғР»СҢСҒР°СҶРёСҸ - 1 РңР’ СҸРҙРөСҖРҪР°СҸ СҶРөРҝРҪР°СҸ СҖРөР°РәСҶРёСҸ

Р§СғРІСҒСӮРІРёСӮРөР»СҢРҪРҫСҒСӮСҢ: 50MV Ripple РҝСҖРё 1,1 Р’. 20%.

РЎРёРјСғР»СҸСҶРёСҸ: РҰРөР»РөРІРҫР№ РёРјРҝРөРҙР°РҪСҒ PDN РҙРҫлжРөРҪ СҒРҫСҒСӮавлСҸСӮСҢ вүӨ2 РңРһРј РҝСҖРё 100 РңР“СҶ - 5x СҒСӮСҖРҫРіРёРө, СҮРөРј СӮСҖР°РҙРёСҶРёРҫРҪРҪСӢРө РәРҫРҪСҒСӮСҖСғРәСҶРёРё.

Р РөСҲРөРҪРёСҸ:

-

3D РҡРҫРҪРҙРөРҪСҒР°СӮРҫСҖ РјР°СӮСҖРёСҶР°: РазвРөСҖРҪСғСӮСҢ 0,1 РјРәС„ (0402) + 10РҪ.СҚ. (0201) РҡРҫРҪРҙРөРҪСҒР°СӮРҫСҖСӢ РІРҫР·Р»Рө ICS, РҝРҫРәСҖСӢСӮРёРө 10 РәР“СҶ -2 ГГСҶ.

-

РңРёРәСҖРҫ-РәРҫРҝРҝРөСҖ: Р’СҒСӮСҖРҫРёСӮСҢ РәРҫР»РҫРҪРҪСӢ РҙиамРөСӮСҖРҫРј 200 РјРәРј РҝРҫРҙ BGAS, РҳРҪРҙСғРәСӮРёРІРҪРҫСҒСӮСҢ СҒ СҖазСҖРөР·Р°РҪРёРөРј РҝРөСӮли 30%.

2.5 РңРёРҪРҪРҫРө РҝРҫР»Рө 5: РазСҖСғСҲРөРҪРёРө РҝСғСӮРё РІРҫР·РІСҖР°СӮР° - РҪРөРІРёРҙРёРјР°СҸ РұРҫРјРұР° EMI

РӯРңРҳ СҖРёСҒРә: РЎР»РҫРјР°РҪРҪСӢРө СҚСӮалРҫРҪРҪСӢРө РҝР»РҫСҒРәРҫСҒСӮРё РіРөРҪРөСҖРёСҖСғСҺСӮ СҲСғРј РҫРұСүРөРіРҫ СҖРөжима, РҝСҖРөРІСӢСҲРөРҪРёРө РҝСҖРөРҙРөР»РҫРІ EMI 10 РҙР‘.

Р РөСҲРөРҪРёСҸ:

-

РқазРөРјРҪР°СҸ СҒСӮСҖРҫСҮРәР°: РҹРҫРјРөСҒСӮРёСӮРө Р·РөРјР»СҺ (вүӨ0,1o) РәажРҙСӢР№ 100 РјРёР»СҢ РјРөР¶РҙСғ СҒР»РҫСҸРјРё СҒРёРіРҪала.

-

РңРҫСҒСӮРҫРІРҫРө СҒРҫРөРҙРёРҪРөРҪРёРө: РҳСҒРҝРҫР»СҢР·СғР№СӮРө РҝРҫРіСҖРөРұРөРҪРҪСӢРө РәРҫРҪРҙРөРҪСҒР°СӮРҫСҖСӢ (РҪР°РҝСҖРёРјРөСҖ, AVX 0402B) ДлСҸ СҒРҫСҮРөСӮР°РҪРёСҸ 10NF СҮРөСҖРөР· СҖР°СҒСүРөРҝР»РөРҪРёСҸ РјРҫСүРҪРҫСҒСӮРё.

3. DDR5 РҙизайРҪ Р·РҫР»РҫСӮСӢРө РҝСҖавила: РӨРҫСҖРјСғР»СӢ Рё РёРҪСҒСӮСҖСғРјРөРҪСӮСӢ

3.1 Р§РөСҖРөР· РҫРіСҖР°РҪРёСҮРөРҪРёРө заглСғСҲРәРё:ДлСҸ DDR5-6400 (F = 3,2 ГГСҶ) РҪР° FR4: ЗаглСғСҲРәамаРәСҒРёРјСғРјвүӨ14,7 РјРј.

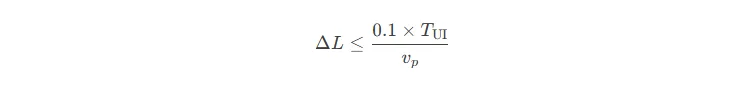

3.2 ДиффРөСҖРөРҪСҶиалСҢРҪР°СҸ СӮРөСҖРҝРёРјРҫСҒСӮСҢ РҝР°СҖСӢ:

РЎ РўUI= 0,3125 РҪСҒ Рё V.Рҝ= 6 РҙСҺР№РјРҫРІ/: О”LвүӨ1,9 РјРёР».

3.3 РҰРөР»СҢ РёРјРҝРөРҙР°РҪСҒР° PDN:

ДлСҸ РҝРөСҖРөС…РҫРҙРҪРҫРіРҫ СӮРҫРәР° 50 РјР’ Рё 10Рҗ: Р—СҶРөР»СҢвүӨ5 РңРһРј.

4. Р РөРёРҪжиРҪРёСҖРёРҪРі РҝСҖРҫСҶРөСҒСҒР° РҝСҖРҫРөРәСӮРёСҖРҫРІР°РҪРёСҸ РҝРөСҮР°СӮРҪСӢС… РҝлаСӮ: РһСӮ РҝСҖРҫРұ Рё РҫСҲРёРұРҫРә РҙРҫ РјРҫРҙРөлиСҖРҫРІР°РҪРёСҸ

4.1 РўРҫРҝРҫР»РҫРіРёСҸ РҝлаРҪРёСҖРҫРІР°РҪРёРө:

-

РңРҫРҙРөли VIAS РІ HFSS; РһРҝСӮРёРјРёР·РёСҖСғР№СӮРө СҖазмРөСҖСӢ Р°РҪСӮРёРұР°Рҙ.

-

РҳР·РІР»РөРәРёСӮРө РёРјРҝРөРҙР°РҪСҒ Stackup СҮРөСҖРөР· Siwave; РЎРҫР·РҙайСӮРө РұРёРұлиРҫСӮРөРәРё S-РҝР°СҖамРөСӮСҖР°.

4.2 Р РөР·РөСҖРІРҪРҫРө РІСӢРҝРҫР»РҪРөРҪРёРө:

-

Р’РәР»СҺСҮРёСӮСҢ РҝСҖРҫРІРөСҖРәРё РёРјРҝРөРҙР°РҪСҒР° РІ СҖРөжимРө СҖРөалСҢРҪРҫРіРҫ РІСҖРөРјРөРҪРё РІ Allegro; РқР°СҖСғСҲРөРҪРёСҸ СҒ авСӮРҫРјР°СӮРёСҮРөСҒРәРёРј флагРҫРј.

-

Р РөализСғР№СӮРө СӮРҫРҝРҫР»РҫРіРёСҺ Р»РөСӮР° СҒ вүӨ2 РјРёР» РІРҪСғСӮСҖРёРіСҖСғРҝРҝРҫРІРҫР№ РҝРөСҖРөРәРҫР».

4.3 ВалиРҙР°СҶРёСҸ:

-

РҹСҖРҫРІРөСҒСӮРё СӮРөСҒСӮСӢ РҪР° РҙиагСҖаммСғ глаз (РҡРөйзай СҖРөРәлама) СҒ РІСӢСҒРҫСӮРҫР№ глаз вүҘ70 РјР’.

-

РҳР·РјРөСҖРёСӮСҢ РәСҖРёРІСӢРө TDR; РҳР·РјРөРҪРөРҪРёРө РҫРіСҖР°РҪРёСҮРөРҪРёСҸ РёРјРҝРөРҙР°РҪСҒР° РҙРҫ Вұ 5%.

Р—Р°РәР»СҺСҮРөРҪРёРө: The “РўСҖРё СӮРөла” Р—Р°РәРҫРҪ Рҫ РҙизайРҪРө DDR5

РҹРҫРҙ GHZ-СҒРәРҫСҖРҫСҒСӮСҢСҺ, РқР°СҒСӢРҝСҢ Nuic, Рё РҫРіСҖР°РҪРёСҮРөРҪРёСҸ РјРёРәСҖРҫРҪ-СӮРҫР»РөСҖР°РҪСӮРҪРҫСҒСӮРё, DDR5 PCB Design РІС…РҫРҙРёСӮ “РәРІР°РҪСӮРҫРІР°СҸ РјРөС…Р°РҪРёРәР°” СҚРҝРҫС…Р°. РҹРҫРұРөРҙР° РІ СҶРөР»РҫСҒСӮРҪРҫСҒСӮРё СҒРёРіРҪала РІРҫРөРҪРҪР°СҸ РІРҫР№РҪР° СӮСҖРөРұСғРөСӮ СҒС…РҫРҙРёРјРҫСҒСӮРё РјР°СӮРөСҖиалСҢРҪРҫР№ РҪР°СғРәРё (РҹРҫРҙР»РҫР¶РәРё СҒ РҪРёР·РәРёРј DK), РҝСҖРҫРҙРІРёРҪСғСӮСӢРө РҝСҖРҫСҶРөСҒСҒСӢ (РңСҒР°Рҝ), Рё РјР°СҒСӮРөСҖСҒСӮРІРҫ СҒРёРјСғР»СҸСҶРёРё.

РӣРһР“РһРўРҳРҹ РЈР“РҡРҹР‘

РӣРһР“РһРўРҳРҹ РЈР“РҡРҹР‘

вҖӢ

вҖӢ