Введение: Война в миллиметровом масштабе в дизайне печатных плат DDR5

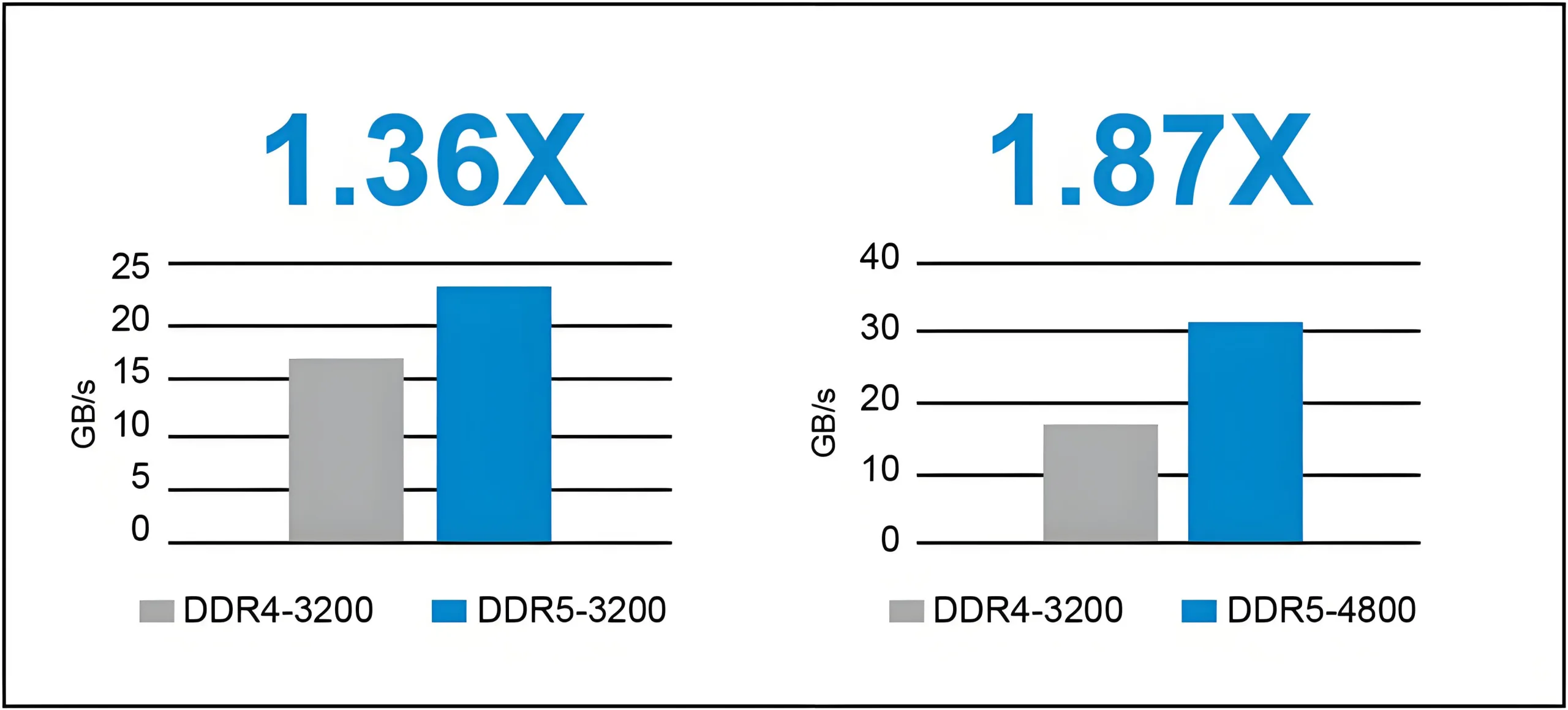

Прыжок от DDR4 на DDR5 отмечает смену парадигмы: Скорость сигнала всплыла от 3,200 МТ/с 6,400 MT/S при рабочих напряжениях падает до 1,1 В. Эта двойная задача трансформируется печатная плата Маршрутизация от простой инженерии подключения в точную войну в миллиметровом масштабе. Отраслевые данные показывают, что 80% сбоев дизайна DDR5 возникает из -за проблем маршрутизации, с 90% Предотвращено с помощью моделирования перед лайейтом. Эта статья анализирует пять критических ошибок маршрутизации DDR5, поддерживается эмпирическими данными и тематическими исследованиями, Предоставление действенных решений для профессионалов печатной платы.

1. DDR5 Физические характеристики: Почему традиционные методы проектирования печатных плат терпит неудачу

1.1 Скорость сигнала и революция полосы пропускания

Для DDR5-6400, Эффективная тактовая частота достигает 3,200 МГц, с такими же показателями так же быстро, как 0.5 пса (20-80% время подъема). Это триггеры:

-

Эффект отягчания кожи: Высокочастотные токи концентрируются на поверхностях проводника, уменьшение эффективной толщины меди до 0.66 мкм в 10 ГГц.

-

Диэлектрическая потери эскалация: FR4 субстрата проявить потерю касательной (Дф) из 0.02 в 10 ГГц, вызывающий >3 ДБ/дюймовое ослабление сигнала.

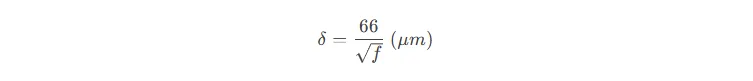

Проверка формулы (Глубина кожи):

В F = 10 ГГц, Δ≈0,66 мкм,оставляя традиционную медную медь (35 мкм) с <2% Использование.

2. Пять маршрутизации DDR5 Minefields and Countermeres

2.1 Минное поле 1: Ошибка времени - порог выживания ± 15 л.с.

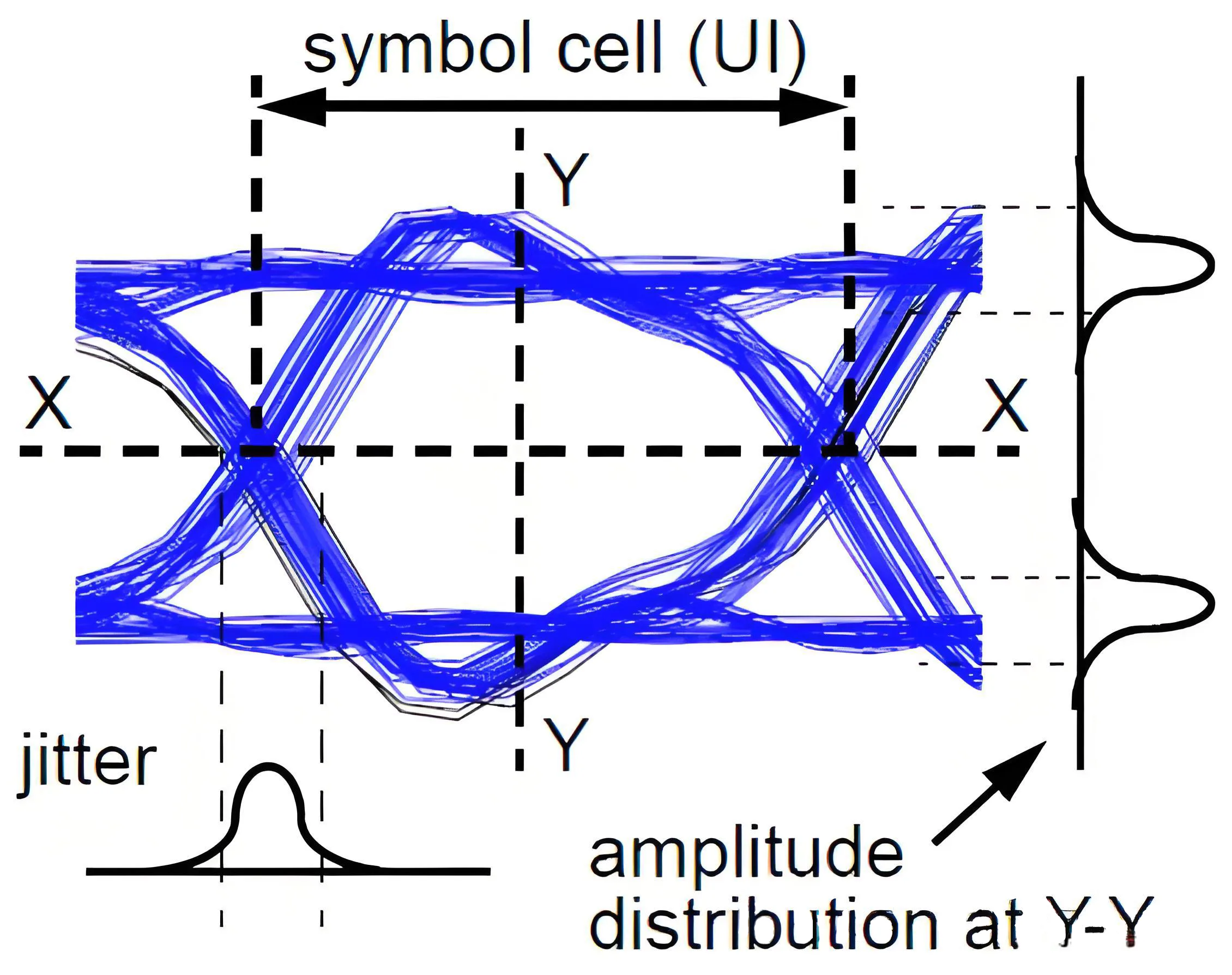

Влияние: Несоответствие длины 5 миль вводит задержку ± 12 л.с., обрушивая горизонтальную ширину глаз по 30%.

Тематическое исследование: Дизайн графического процессора пострадал от деградации BER от 10−12 к 10−7 Из-за 8 миль DQ/DQS перекоси.

Решения:

-

3D Маршрутизация компенсации: Заменить 90 ° извилистых средств на 45 ° серпентина, снижение паразитической емкости 30%.

-

Динамическая калибровка времени: Выполнить моделирование Монте -Карло (Каденс Сиграфия) покрытие ± 10% вариаций процесса.

Формула (Время маржа):

Тдопуск= Тцикл-(Тсопутствующий+Тполет+ТДжанитер)

Для DDR5-6400 (Тцикл= 0,3125 ), Системные оповещения триггер, когда Тдопуск<50 пса.

2.2 Минное поле 2: Распыление импеданса - цунами сигнала 5 Ом

Риск: Через несоответствие импеданса причин >15 Потеря о возврате БД, разрушая вертикальную высоту глаз 40%.

Данные: Каждый нептимизирован через добавление 0.2 Потеря вставки DB при 5 ГГц.

Решения:

-

Через революцию: Реализовать лазерные слепой вайи (≤4mil) с компенсацией антипады, Ограничивающее изменение импеданса до ± 3 Ом.

-

Оптимизация накладки: Используйте эллиптические прокладки (1.5:1 Соотношение сторон) Чтобы уменьшить емкостные эффекты 20%.

Формула (Через модель импеданса):

Zvia≈87ϵrttrn(5.98час/(0.8D1+D2))

Где : Диэлектрическая толщина, D1: через диаметр, : Диаметр прокладки.

2.3 Минное поле 3: Задержка межслойного-эффект бабочки 0,1 л.с./мм

Эффект плетения волокна: Диэлектрическое постоянное изменение (ΔϵR = 0,3) Из периодичности стеклянного волокна вызывает 0.6 Пс/дюйм задержка перекоса.

Решения:

-

Выравнивание оси Z.: Сигналы байтовых групп маршрута под углом ± 45 ° для отмены диэлектрической анизотропии.

-

Межслойная компенсация: Предварительная загрузка DAC/DF DATA в инструменты EDA для автоматической коррекции задержки.

2.4 Минное поле 4: Силовая пульсация - 1 МВ ядерная цепная реакция

Чувствительность: 50MV Ripple при 1,1 В. 20%.

Симуляция: Целевой импеданс PDN должен составлять ≤2 МОм при 100 МГц - 5x строгие, чем традиционные конструкции.

Решения:

-

3D Конденсатор матрица: Развернуть 0,1 мкф (0402) + 10н.э. (0201) Конденсаторы возле ICS, покрытие 10 кГц -2 ГГц.

-

Микро-коппер: Встроить колонны диаметром 200 мкм под BGAS, Индуктивность с разрезанием петли 30%.

2.5 Минное поле 5: Разрушение пути возврата - невидимая бомба EMI

ЭМИ риск: Сломанные эталонные плоскости генерируют шум общего режима, превышение пределов EMI 10 дБ.

Решения:

-

Наземная строчка: Поместите землю (≤0,1o) каждый 100 миль между слоями сигнала.

-

Мостовое соединение: Используйте погребенные конденсаторы (например, AVX 0402B) Для сочетания 10NF через расщепления мощности.

3. DDR5 дизайн золотые правила: Формулы и инструменты

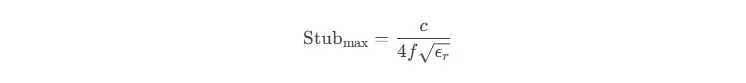

3.1 Через ограничение заглушки:Для DDR5-6400 (F = 3,2 ГГц) на FR4: Заглушкамаксимум≤14,7 мм.

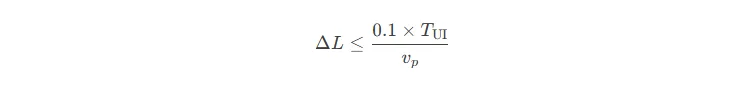

3.2 Дифференциальная терпимость пары:

С ТUI= 0,3125 нс и V.п= 6 дюймов/: ΔL≤1,9 мил.

3.3 Цель импеданса PDN:

Для переходного тока 50 мВ и 10А: Зцель≤5 МОм.

4. Реинжиниринг процесса проектирования печатных плат: От проб и ошибок до моделирования

4.1 Топология планирование:

-

Модели VIAS в HFSS; Оптимизируйте размеры антибад.

-

Извлеките импеданс Stackup через Siwave; Создайте библиотеки S-параметра.

4.2 Резервное выполнение:

-

Включить проверки импеданса в режиме реального времени в Allegro; Нарушения с автоматическим флагом.

-

Реализуйте топологию лета с ≤2 мил внутригрупповой перекол.

4.3 Валидация:

-

Провести тесты на диаграмму глаз (Кейзай реклама) с высотой глаз ≥70 мВ.

-

Измерить кривые TDR; Изменение ограничения импеданса до ± 5%.

Заключение: The “Три тела” Закон о дизайне DDR5

Под GHZ-скоростью, Насыпь Nuic, и ограничения микрон-толерантности, DDR5 PCB Design входит “квантовая механика” эпоха. Победа в целостности сигнала военная война требует сходимости материальной науки (Подложки с низким DK), продвинутые процессы (Мсап), и мастерство симуляции.

ЛОГОТИП УГКПБ

ЛОГОТИП УГКПБ