I chip a semiconduttore servono come “cervelli” dell'era digitale, Mentre l'imballaggio chip funge da protezione “armatura” E “rete neurale.” Oltre alla schermatura muore di silicio fragile, consente una gestione termica critica, connettività elettrica, e trasmissione del segnale. Dai pacchetti voluminosi a foro attraverso soluzioni a livello di wafer ultra-sottili, L'evoluzione del packaging ha guidato la miniaturizzazione dell'elettronica e il miglioramento delle prestazioni - una saga tecnologica monumentale.

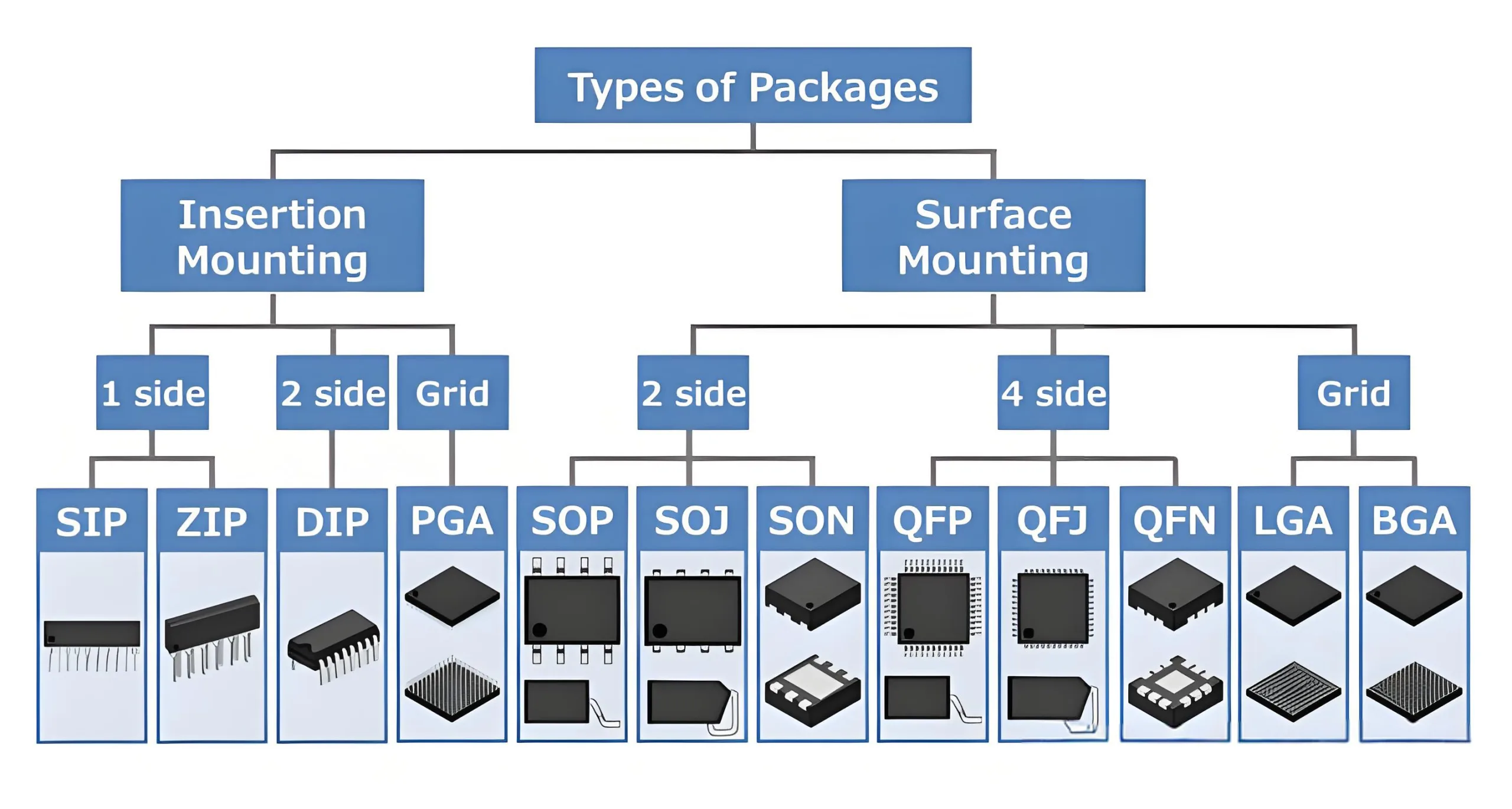

Classificare le tecnologie di imballaggio

Con metodo di montaggio

-

Imballaggio a foro (Tht):

Pin inseriti in PCB Placted Through Holes per la saldatura. Rappresenta la tecnologia di generazione della prima generazione. -

Tecnologia a montaggio di superficie (SMT):

Componenti saldati direttamente su cuscinetti PCB. Abilita una densità maggiore e un gruppo automatizzato.

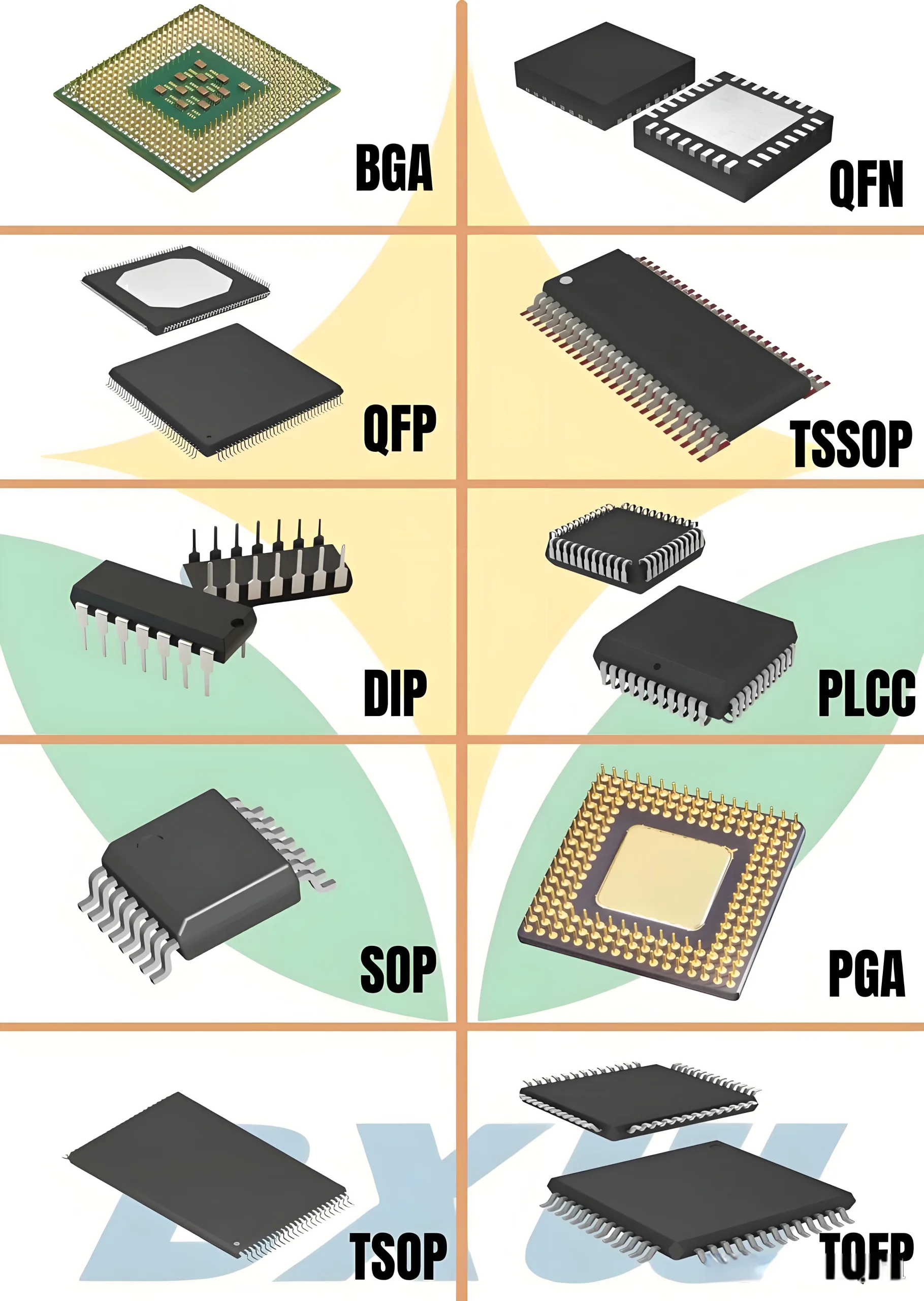

Per configurazione del pin (Progressione della densità)

Singola fila → doppia fila → quad-lati-area-ary

L'era del buco attraverso

Fare/a: Fondazioni di componenti discreti

-

Diodo DO-41: Ø2,7 mm × 5,2 mm

-

Transistor To-220: Geste ≤50w dissipazione di potenza

-

Resistenza termica: R<sub>E</sub> = (T<sub>J</sub> – T<sub>UN</sub>)/P

Dove R<sub>E</sub> = resistenza termica da giunzione a ambiente

SIP/ZIP: Innovazioni mono in linea

-

SORSO: 3-16 perni, conveniente per resistori/diodi a bassa potenza

-

Zip: 40% densità del pin più elevata rispetto al SIP tramite disposizione del perno a zigzag

-

Applicazioni: Moduli di memoria precoce, regolatori di tensione

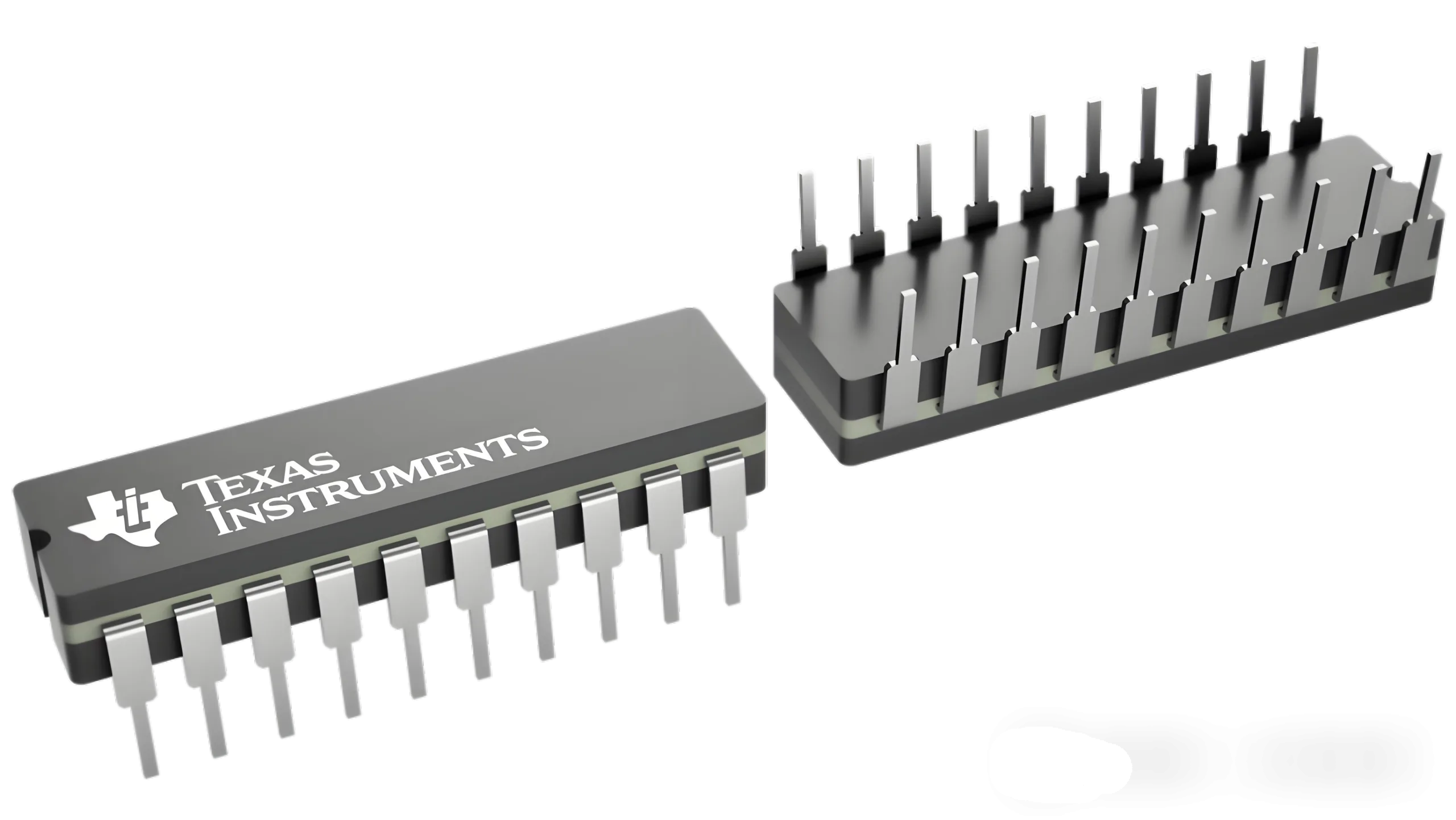

IMMERSIONE: La rivoluzione IC

-

PIT PIN: 2.54mm (0.1″) standard

-

1980quota di mercato: >70% di imballaggio IC

-

Prestazioni termiche:

Dip ceramica: 20-30 Conducibilità W/M · K.

Dip di plastica: 0.2-0.3 W/m · k

PGA: Pioneer di calcolo ad alte prestazioni

-

Densità del perno: 3× superiore a DIP

-

Applicazioni: Intel 80386/80486 CPU

-

Forza di inserzione: 30-100 Newton

La rivoluzione SMT

SOD/SOT: Miniaturizzazione componente discreta

-

SOD-323: 1.7mm × 1,25 mm

-

Resistenza termica SOT-23: ~ 250 ° C/W.

-

Profilo di riflusso: Picco Temp 235-245 ° C.

Cavi di gabbiano: Famiglia SOP

-

Evoluzione del pitch pin:

1.27mm (SOP) → 0,8 mm (Ssop) → 0,65 mm (Tssop) -

Pacchetti derivati:

SOP → SSOP → TSOP → TSSOP → VSSOP -

Miglioramento termico: HSSOP riduce la resistenza termica di 40%

Configurazione J-Lead: Osservazione

-

Resistenza meccanica: 30% maggiore resistenza allo stress

-

Limitazione elettrica: 0.8-1.2NH induttanza parassita

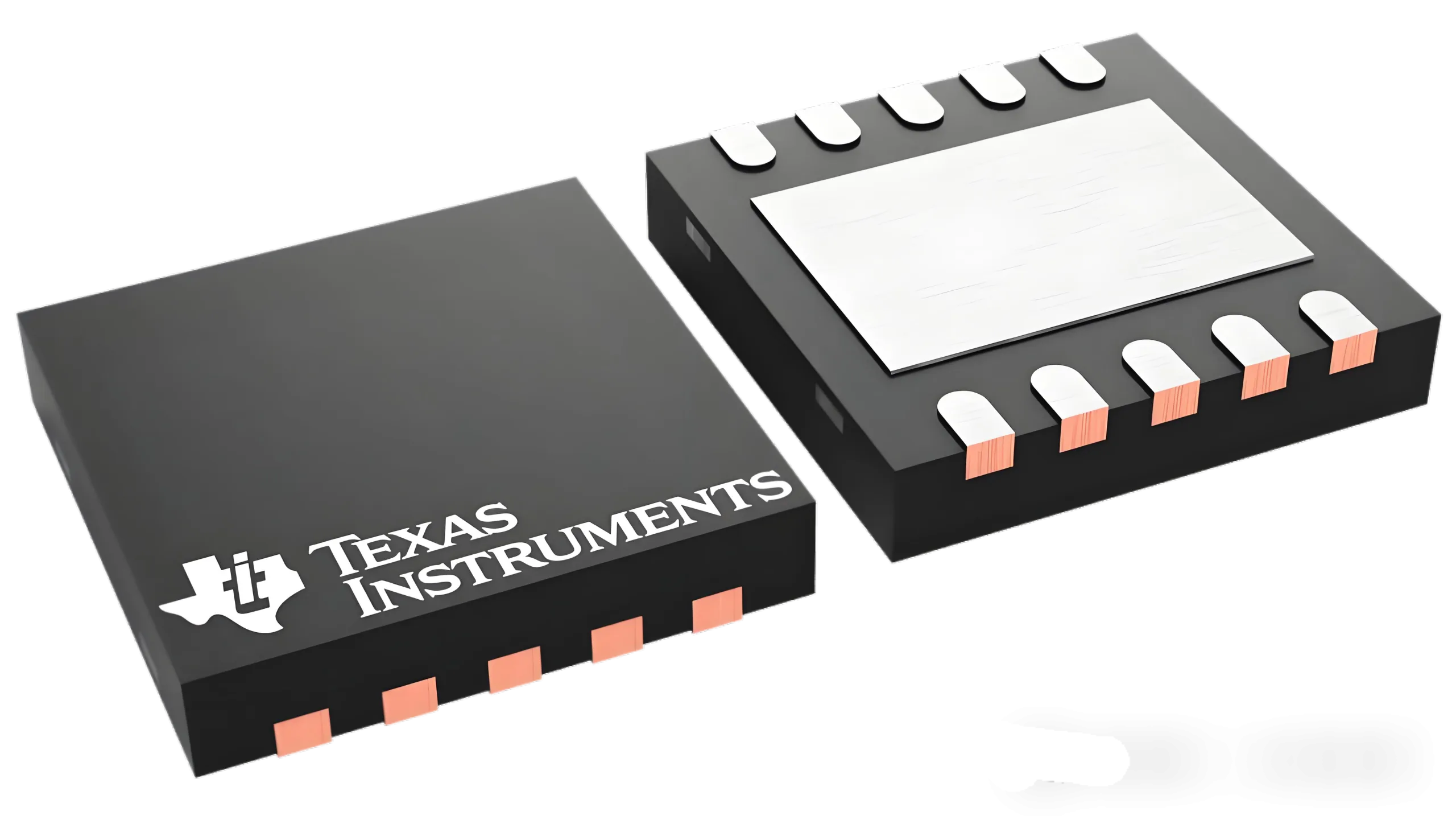

BUSHTHTROUGH NESSUNA: Figlio/dfn

-

Efficienza dello spazio: >50% Miglioramento rispetto a SOP

-

Prestazioni termiche: 15° C/W con cuscinetti termici

-

Limite di miniaturizzazione:

X2son: 0.6mm × 0,6 mm × 0,32 mm

Fisica dietro la miniaturizzazione

Tre sfide fondamentali regolano il ridimensionamento dei pacchetti:

-

Gestione termica:

Q = haΔt

Dimensioni ridotte (↓ a) richiede un coefficiente di convezione più elevato (↑ h) -

Controllo dello stress termico:

S = Eptt

Dove cte (UN) La mancata corrispondenza induce stress -

Integrità del segnale:

Induttanza del piombo *l ≈ 2L(ln(2L/d)-1) NH*

La miniaturizzazione riduce l'induttanza di 30%

Prossima frontiera: Imballaggio avanzato

Mentre X2SON colpisce scale da 0,6 mm, L'innovazione si sposta a:

-

3Packaging d: Integrazione verticale abilitata per TSV

-

Integrazione eterogenea: Assemblaggio di dapi multi-nodi

-

Fotonica: Co-progettazione della fotonica del silicio

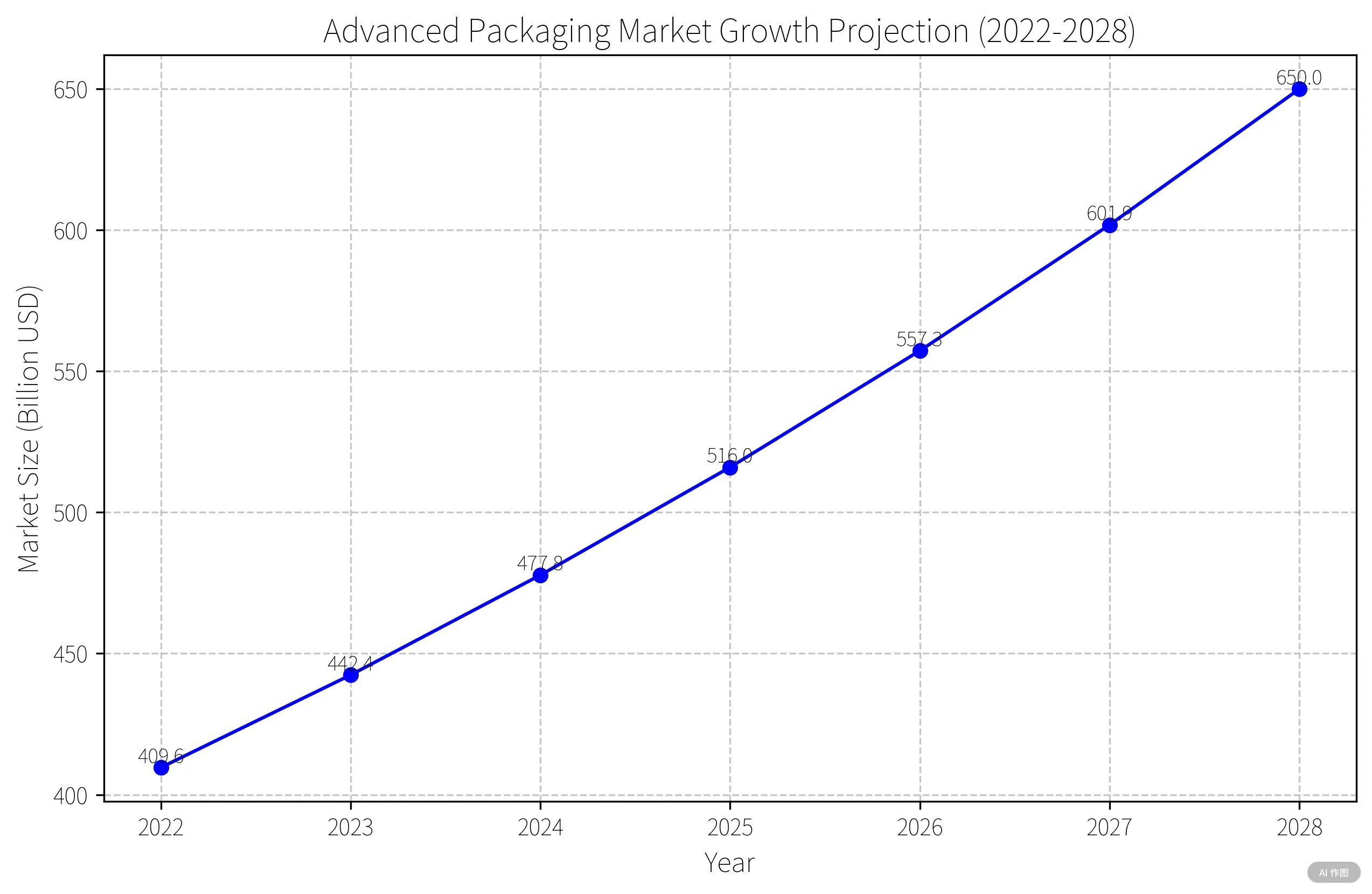

Previsioni di mercato (Développement yole):

8% CAGR attraverso 2028 → Mercato di $ 65 miliardi

L'imballaggio ora definisce criticamente le prestazioni del sistema - ben oltre la semplice protezione.

Conclusione

Dall'impronta da 0,6 mm di 2,54 mm di Dep all'impronta di 0,6 mm di X2SON, I progressi del packaging ridefiniscono continuamente l'elettronica. Ogni smartphone slim e dispositivo 5G si affidano a queste innovazioni invisibili. Con emergere con AI e calcolo quantistico, L'imballaggio chip continuerà a spingere i confini di nanosci.

*Next in Series:

Tecnologie BGA/CSP/WLCSP

3Packaging d & TSV Interconnects

Scienza dei materiali di imballaggio avanzato

Rimani sintonizzato!*

LOGO UGPCB

LOGO UGPCB