Ogni progresso microscopico nella tecnologia del packaging rimodella i confini fisici dell’elettronica.

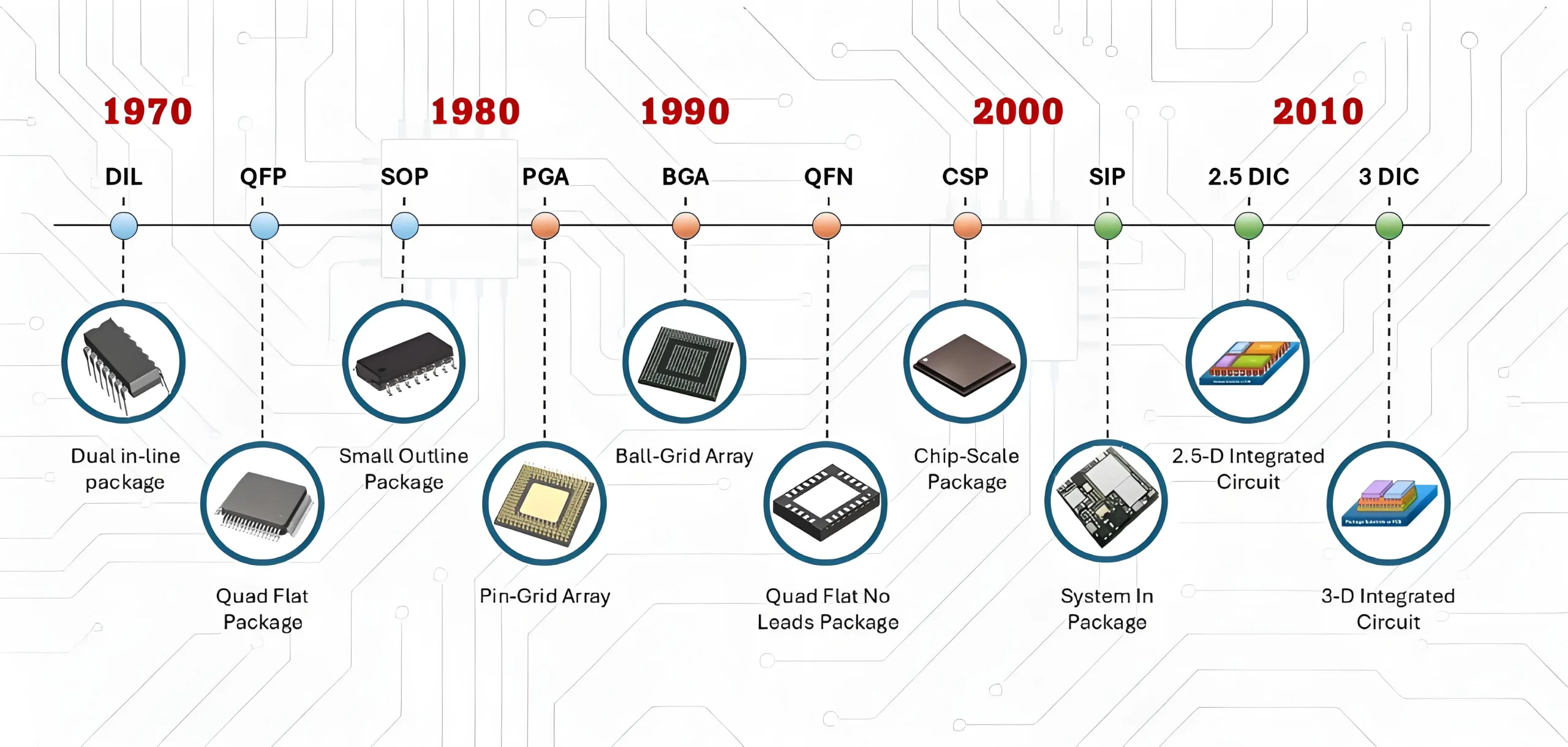

Nella scorsa settimana Evoluzione del confezionamento dei chip: Dal DIP a X2SON: come la miniaturizzazione ha rimodellato l'elettronica, abbiamo esplorato l'era del confezionamento a foro passante (IMMERSIONE) e come i dispositivi a montaggio superficiale (SOP, Osservazione, FIGLIO) ha avviato la miniaturizzazione del dispositivo. Mentre queste tecnologie hanno gettato le basi del packaging moderno, IL rivoluzione della miniaturizzazione continua. Oggi, esaminiamo i pacchetti a densità più elevata, dal CSP quad-flat al livello wafer, e il loro impatto su Progettazione di circuiti stampati limiti.

Pacchetti quad-flat: L'equilibrio spazio-densità

Pacchetti quad-flat (QFP, PLCC/QFJ, QFN) rappresentano un'evoluzione critica verso una maggiore densità di I/O utilizzando tutti e quattro i bordi del package.

QFP: Il pioniere della densità ad ala di gabbiano

QFP (Pacchetto appartamento quadruplo) caratteristiche iconiche “ad ala di gabbiano” (A forma di L) conduttori che si estendono da tutti i lati. Suo passo del perno (0.4mm/0,5 mm/0,65 mm) detta Instradamento del PCB densità e precisione di saldatura.

Varianti QFP:

-

Dimensioni/spessore: LQFP (Basso profilo), TQFP (Magro), VQFP (Molto magro)

-

Materiale: PQFP (Plastica), MQFP (Metallo)

-

Termico migliorato: HQFP, HLQFP, HTQFP, HVQFP

-

Protezione: BQFP (Imbottiture angolari con paraurti per evitare che i cavi si pieghino)

La gestione termica è fondamentale. La formula della resistenza termica giunzione-ambiente θja = (Tj-Ta)/P (Dove Tj=temp.giunzione, Di fronte=temperatura ambiente, P=potenza) governa la progettazione della dissipazione del calore.

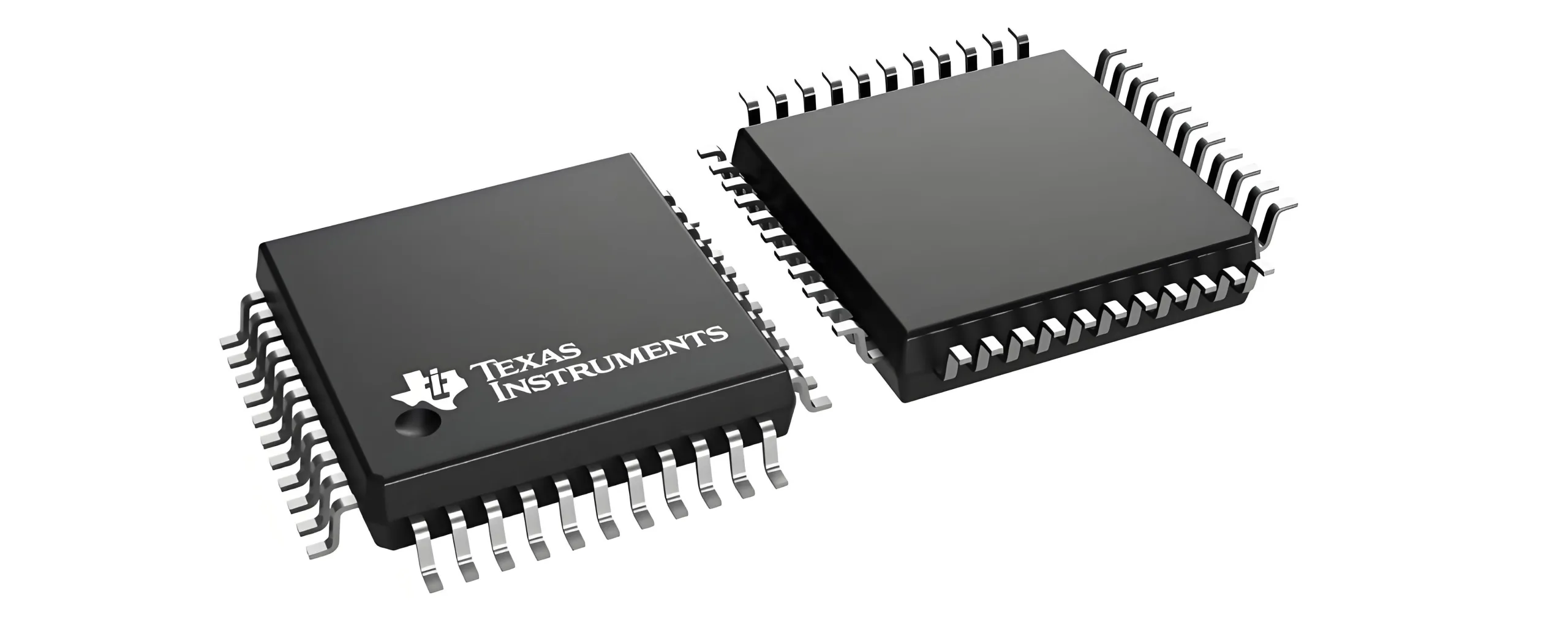

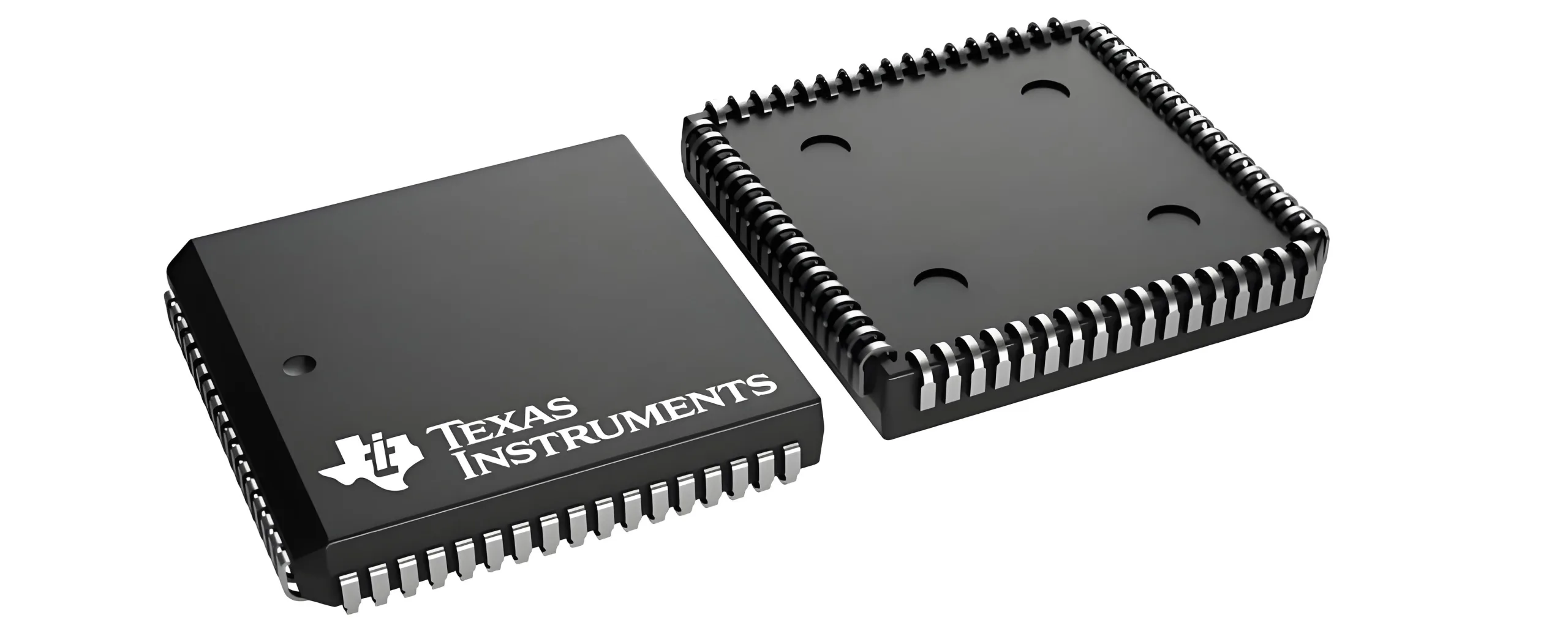

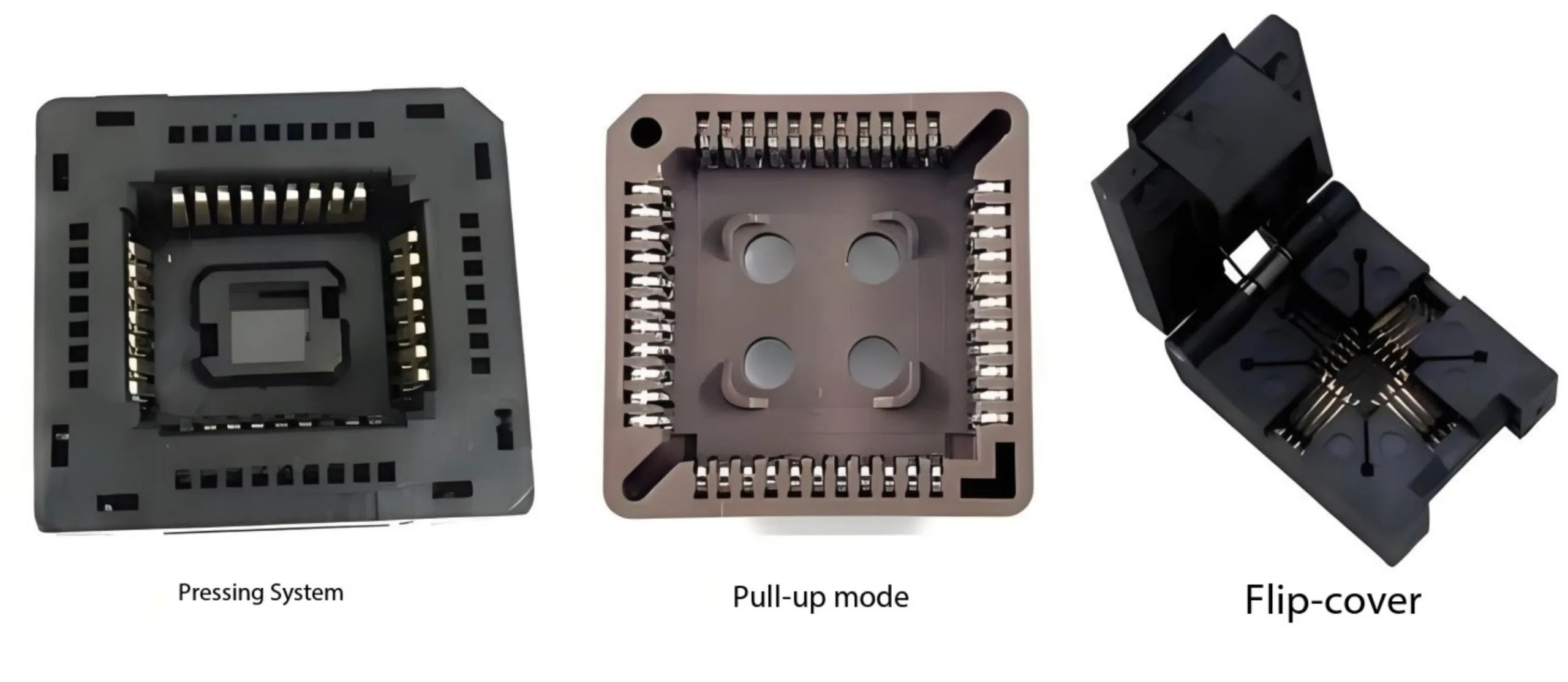

PLCC/QFJ: Stabilità grazie ai cavi J

PLCC (Portatrucioli con piombo in plastica) o QFJ (Quad Flat J-conduttore) utilizza conduttori a forma di J piegati verso il basso per la stabilità meccanica contro vibrazioni/stress termico.

Vantaggio della standardizzazione: L'elevata compatibilità di PLCC/QFJ con le prese di prova universali semplifica i test di produzione. Sebbene QFJ sia tecnicamente preciso, “PLCC” rimane preferito dal settore.

QFN: La svolta nella miniaturizzazione senza piombo

QFN (Quad Flat senza piombo) elimina i cavi esterni, collegamento tramite:

-

Tampone esposto (EP): Percorso termale diretto a PCB rame

-

Fianchi bagnabili: Tamponi saldabili sulle pareti laterali

Vantaggi principali:

-

Ultracompatto: 40% più piccolo del QFP

-

Superiorità elettrica: Percorsi più brevi riducono l'induttanza parassita (L ≈ μ·l/w)

-

Efficienza termica: θja inferiore vs. QFP della stessa dimensione

Evoluzione dello spessore: LQFN → UQFN → VQFN → WQFN → X1QFN → X2QFN. LCC (LPCC/LCCC) è la variante in ceramica/plastica senza piombo.

Pacchetti di matrici: Rivoluzionare i limiti di densità

Quando il quad-flat raggiunge i limiti di I/O, pacchetti di array (LGA, BGA) abilitare la densità di interconnessione 2D.

LGA: Connessione elastica di precisione

LGA (Matrice della griglia terrestre) utilizza contatti metallici allineati con precisione (per esempio., LGA775: 775 contatti) accoppiamento con i pin della presa.

Valore principale:

-

Possibilità di presa: Aggiornamenti/manutenzione della CPU

-

Bassa induttanza: Percorsi brevi del segnale

-

Alta affidabilità: Ideale per CPU (Intel/AMD)

Limitazione: L'elevato costo/dimensione del socket favorisce il BGA nei dispositivi compatti. Nota: Gli LGA possono essere saldati direttamente tramite SMT.

BGA: La dominanza della sfera saldante

BGA (Array a sfera) si collega tramite una matrice di sfere di saldatura. Passo della palla (0.3–1,0 mm; <0.2mm per FBGA) è fondamentale.

Vantaggi trasformativi:

-

Alta densità: >1,000 Io/noi (vs. QFP ~ 300)

-

Risparmio di spazio: 30%+ riduzione dell’area rispetto. QFP

-

Elettrico/Termico: Basso ritardo del segnale; le palline conducono il calore

-

Autoallineamento: Assemblaggio di aiuti per la tensione superficiale

Famiglia BGA:

-

Materiale: PBGA (Plastica), CBGA/CABGA (Ceramica)

-

Dimensioni/Passo: nFBGA/FBGA (Passo fine), PiccoloBGA, DSBGA/WCSP (Dimensioni dello stampo), LFBGA/VFBGA (Magro)

-

Integrazione:

-

Fcbga (Flip-Chip): Connessione diretta tra stampo e substrato tramite microbump

-

Pop (Pacchetto nel pacchetto): Impilamento verticale (per esempio., logica + memoria)

-

PG-WF2BGA: Confezione fan-out a livello di wafer

-

Sfide: Ispezione a raggi X (Assi), rielaborazione complessa, Corrispondenza CTE Materiali PCB.

Confronto dei pacchetti di array

| Caratteristica | PGA (Matrice della griglia dei perni) | LGA (Matrice della griglia terrestre) | BGA (Array a sfera) |

|---|---|---|---|

| Connessione | Perni rigidi | Contatti planari | Sfere di saldatura |

| Punto di forza chiave | Affidabilità della presa | Densità + inseribile | Densità massima/dimensione minima |

| Ritardo del segnale | Più alto | Medio | Il più basso |

| Applicazioni | CPU legacy/industriali | CPU desktop/server | Dispositivi mobili/GPU/SoC |

| Spazio PCB | Grande | Medio | Compatto |

Chip-scala & Pacchetti a livello di wafer: Avvicinamento ai limiti fisici

CSP: Ridefinire i confini delle dimensioni

CSP (Pacchetto scala chip) metrica chiave: Dimensioni confezione ≤ 1,2× dimensioni della matrice (vs. 2–5× per tradizionale). BGA essenzialmente miniaturizzato (FBGA/VFBGA) con passo più fine (0.2–0,5 mm).

Valore: Miniaturizzazione definitiva per dispositivi indossabili/sensori.

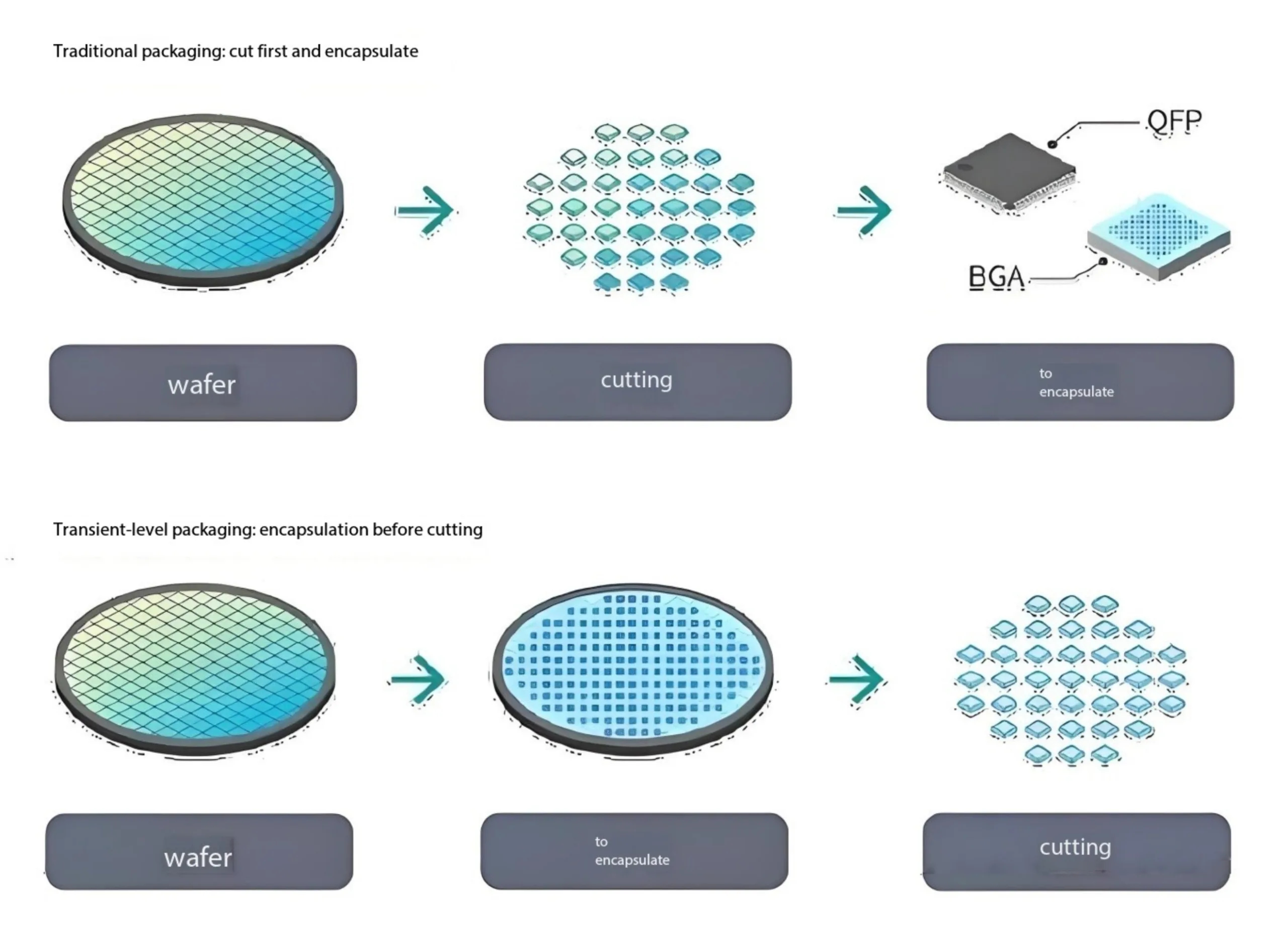

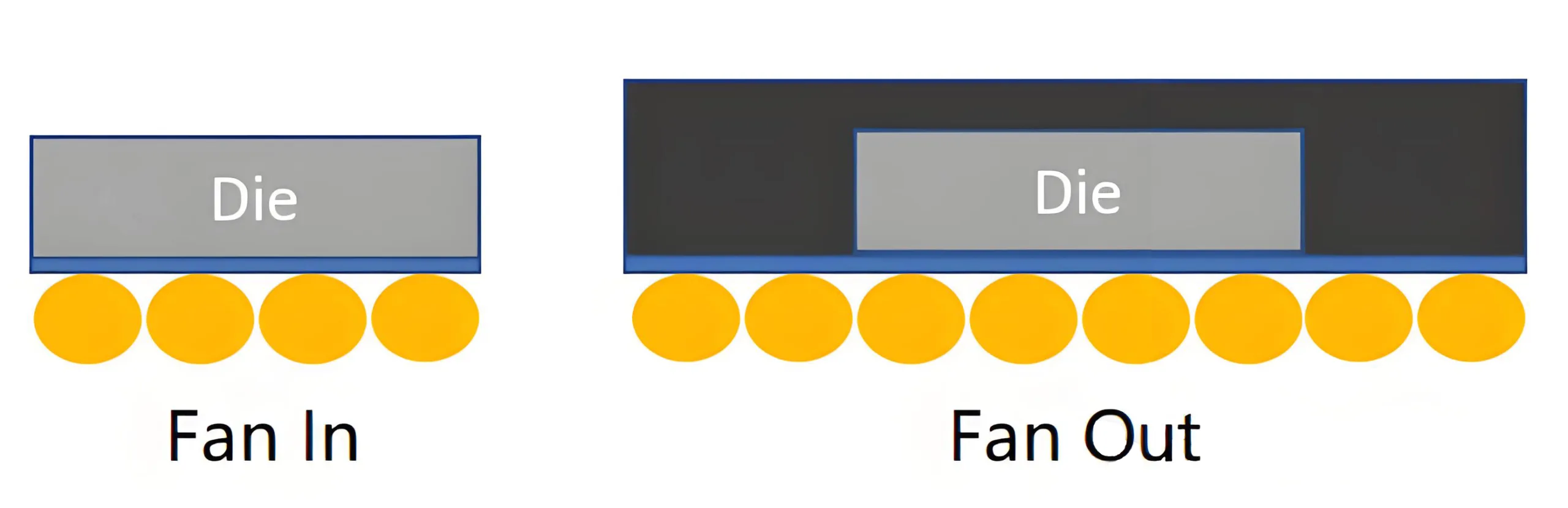

WLCSP: La rivoluzione a livello di wafer

L'imballaggio a livello di wafer/WLCSP completa tutti i passaggi (RDL, ballare) sulla cialda prima di tagliarla a cubetti.

Vantaggi dirompenti:

-

Dimensioni minime: ≈ Dimensioni della matrice

-

Riduzione dei costi: 30-50% più economico (nessun substrato/stampaggio)

-

Massime prestazioni: Interconnessioni più brevi, parassiti più bassi

Tipi WLCSP:

-

WLCSP con ingresso ventola:

-

Palline all'interno dell'area della fustella

-

Dimensione della confezione = dimensione dello stampo

-

Basso costo per sensori/PMIC

-

-

Distribuzione WLCSP (per esempio., Informazioni su TSMC, Samsung FO-PLP):

-

Le palline si estendono oltre il dado

-

Dimensioni del pacchetto > dimensione dello stampo

-

Maggiore densità di I/O, integrazione multi-chip

-

Per SoC/moduli RF premium

-

ID visivo: Silicone non incapsulato (vs. DFN stampato in resina).

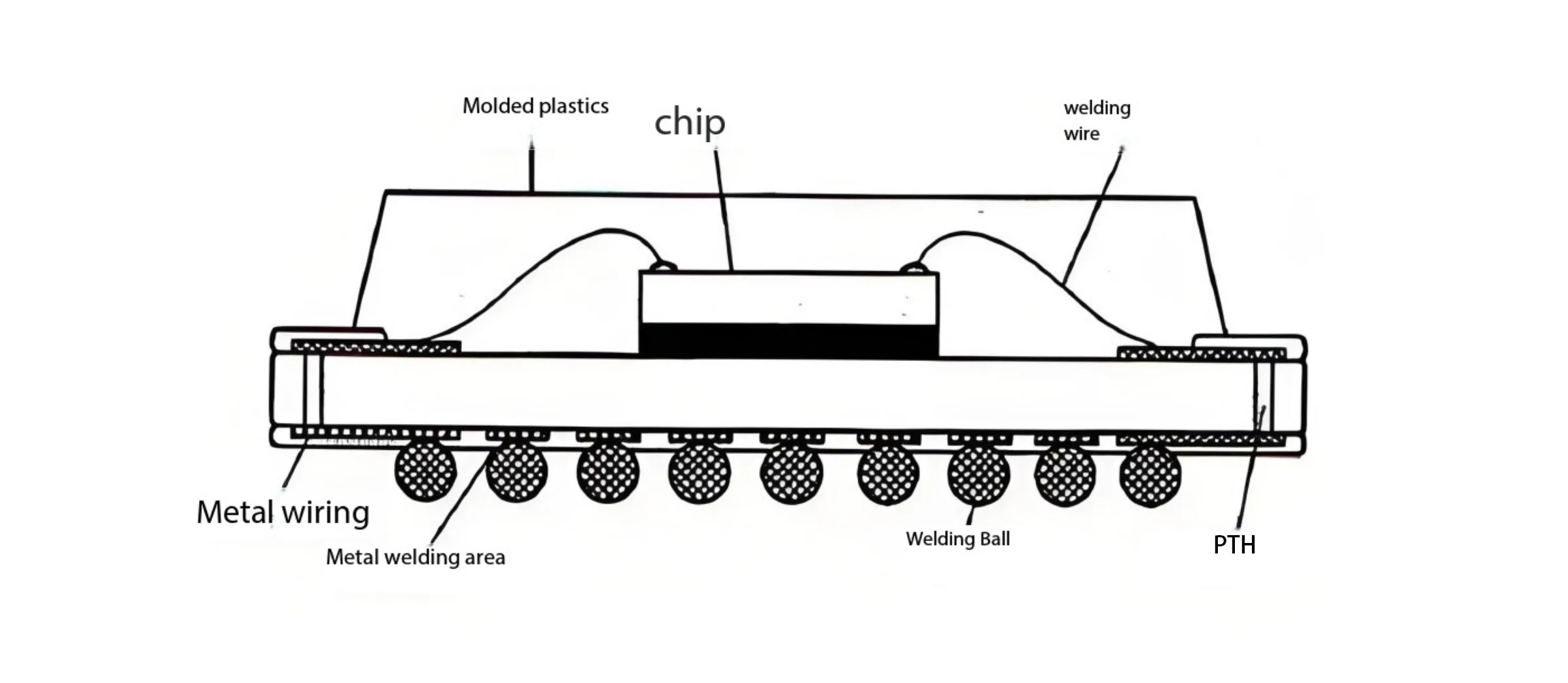

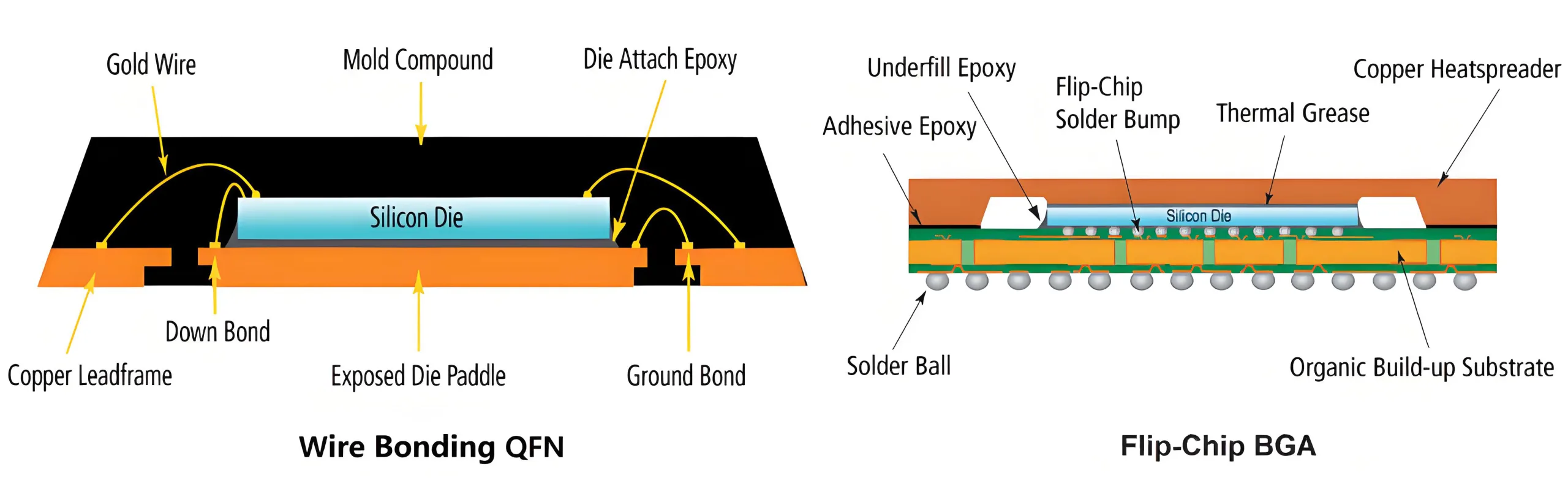

Morfologia dell'imballaggio & Tecniche di incollaggio

Modulo del pacchetto esterno (QFP/BGA/WLCSP) e il legame interno sono intrinsecamente collegati:

-

Legame filo:

-

Maturo, basso costo

-

Domina QFP/QFN/BGA di fascia media

-

Avere/Con fili; I/O moderato

-

-

Flip-Chip:

-

Le matrici si attaccano a faccia in giù tramite microbump

-

Interconnessioni più brevi, induttanza più bassa

-

Essenziale per FCBGA/WLCSP/CSP ad alte prestazioni

-

Conclusione & Future Frontiers

Da QFP a LGA/BGA e infine CSP/WLCSP, l'evoluzione del packaging dei chip è a cronaca della compressione dello spazio, miglioramenti delle prestazioni, e ottimizzazione dei costi. Ogni salto di miniaturizzazione rimodella il design del PCB, generando tracce più fini, multistrato ISU, e materiali avanzati.

Prossima frontiera: Tecnologie come TSV (Attraverso il silicio Via), Sorso (Sistema nel pacchetto), e l'IC 2.5D/3D ora consentono l'integrazione eterogenea 3D, spingendo la progettazione PCB verso nuove dimensioni, che verranno esplorate nel nostro prossimo articolo.

Quando un miliardo di transistor entrano in un contenitore grande quanto un granello di sabbia, battaglie di ingegneria elettronica su scala molecolare.

LOGO UGPCB

LOGO UGPCB

Grazie per aver condiviso le informazioni con noi.

whoah questo blog è magnifico, mi piace davvero leggere i tuoi articoli. Continuate così con i buoni dipinti! Lo riconosci, molte persone stanno cercando queste informazioni, puoi aiutarli molto.