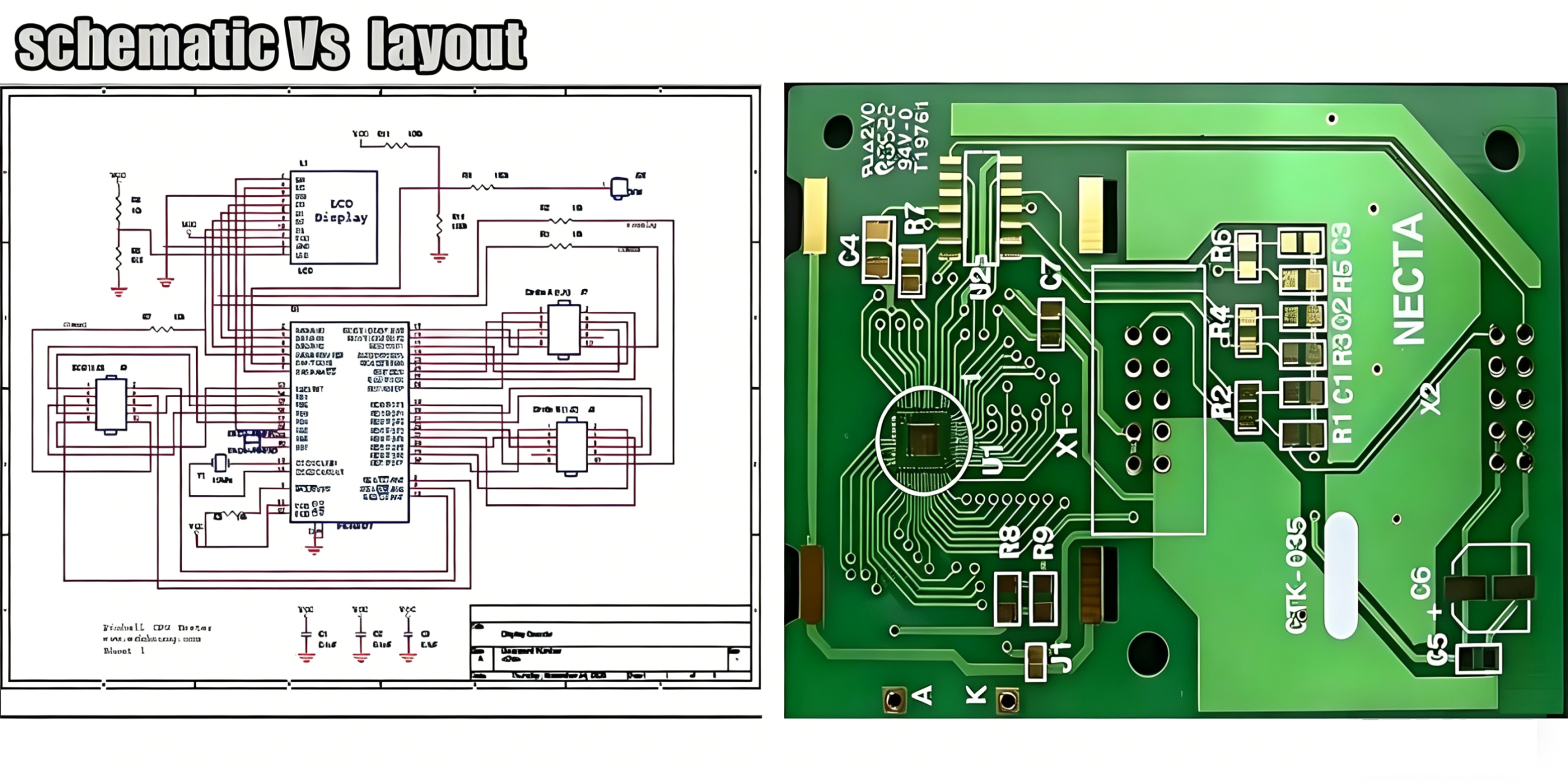

In the world of プリント基板設計 そして PCBA製造, three terms often cause confusion: レイアウト (physical framework design), 配置 (component positioning), そして ルーティング (trace routing). Many engineers with years of experience still struggle to explain how these three elements work together. This article gives you a clear framework based on IPC and UL standards.

1. Core Definitions of the Three Elements

PCB レイアウト is the top-level design concept. It defines the entire board’s physical structure – board dimensions, レイヤー数, connector locations, high-speed signal paths, and power/ground plane assignments. A good Layout sets the maximum manufacturability limit for the whole プリント基板.

PCB Placement is the first execution step of Layout. It places every resistor, コンデンサ, IC, and connector onto the board according to the schematic and functional zones.

PCB Routing is the second execution step. It uses copper traces to connect all components based on the netlist.

A house-building analogy works best: Layout is the architectural blueprint; Placement is furniture arrangement; Routing is the water and electrical wiring. If the blueprint fails proper planning, even the best furniture placement will cause traffic chaos. Poor furniture arrangement forces wiring to take detours, increasing both cost and failure risks.

2. 配置: The First Critical Node for PCB Performance

A messy PCB with low space utilization often traces its root cause back to the Placement phase. A golden rule in high-performance プリント基板 デザイン: good placement is the foundation of mature routing. Once components reflow onto the board during first assembly, their positions become fixed. Later Routing can only dance in shackles.

によるとIPC-2221C generic design requirements, engineers must consider functional partitioning during Placement: separate digital from analog circuits; place high-frequency devices (like CPU and DDR memory) close together to shorten critical traces; keep power module loops (input cap – power IC – inductor – output cap) コンパクト; and place high-frequency decoupling capacitors immediately next to IC power pins. These steps ensure power integrity and minimize switching noise.

Mechanical constraints also affect Placement. Fixed features like USB ports, Ethernet RJ45, ボタン, LED, and mounting holes must first align with the DXF mechanical drawing. High-heat components such as power MOSFETs, LDOs, or main ICs should go near vents or heat-dissipation edges. This prevents localized temperature rise on the PCBA, aligning withIPC-2152 thermal design principles.

3. ルーティング: From Netlist to Physical Copper Traces

Routing transforms the schematic’s logical connections into actual copper traces on the board – the most time-consuming and resource-intensive phase in EDA software.

For multilayer boards, Routing affects not only continuity but also signal integrity (そして) and power integrity (PI). In high-speed PCB Layout, signal lines like DDR data, PCIe differential pairs, and USB must reference a continuous ground plane. They must never cross split reference planes; さもないと, the return path breaks, causing severe EMI and potential radiation test failures.

Routing quality directly ties to IPC acceptance standards.IPC-A-600M defines target and acceptable conditions for internal and external observable features on a PCB, with quantitative criteria for trace width precision and layer-to-layer registration.

4. The 3W and 20H Rules: Classic Design Principles from IPC Standards

To increase your PCB design professionalism, you must master these IPC-derived engineering rules.

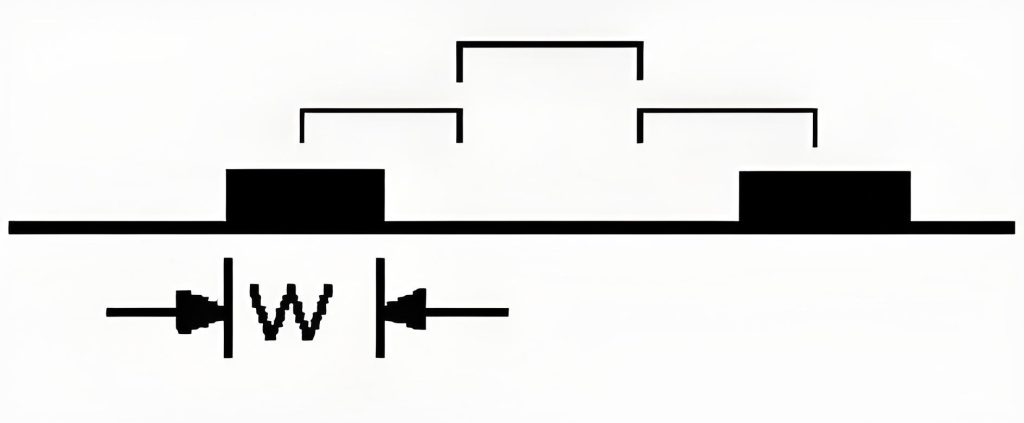

The 3W Rule addresses crosstalk reduction. When multiple high-speed signal traces run parallel over long distances, keep their center-to-center spacing at leastthree times the trace width. Engineering handbooks from IPC sources show that 3W spacing blocks about 70% of electric field coupling. Extending to 10W spacing blocks nearly 98% of crosstalk.

The 20H Rule suppresses electromagnetic edge radiation between power and ground planes. On multilayer PCB Layouts, shrink the power plane’s physical edge inward from the ground plane edge by20 times the dielectric thickness (H) between the two planes. A 20H shrink confines about 70% of electric fields within the ground plane, greatly improving EMC performance. This rule becomes critical for clock frequencies above5 MHz or pulse rise times under5 ns. It requires at least 8 total layers for full effectiveness.

5. Data from IPC Standards: クリアランス, Temperature Rise, and Current Calculation

To strengthen your article’s authority and depth, always cite supporting data from IPC standards.

IPC-2221 specifies a minimum electrical clearance of0.1 mm (について 4 ミル) between any two conductors on a general-use PCB. For power conversion equipment, recalculate clearance using the voltage creepage tables in the standard to guarantee dielectric withstand safety. For spacing between two adjacent drilled holes (drill-to-drill), IPC-2221 recommends a minimum margin of0.5 mm (20 ミル).

For thermal design and current-carrying capacity, the industry now follows IPC-2152 (Standard for Determining Current Carrying Capacity in プリント基板設計). This standard replaces the outdated IPC-2221 thermal data from 50 数年前. IPC-2152 considers board material thermal conductivity, layer position (outer or inner), and adjacent copper planes. A classic conservative estimation formula uses the form:Where *k*, *b*, *c* are non-physical constants. For outer layer traces (better cooling), *k* ≈ 0.048. For inner layer traces (poorer cooling), *k* ≈ 0.024. A typical temperature rise TRISE ranges from 10°C to 30°C. (Sources: IPC-2152 framework and major EDA tool technical manuals.)

6. From Layout to High-Yield PCBA Mass Production: Synergy of Three Essentials

A high-yield PCBA manufacturing project always relies on the synergy of Layout, 配置, とルーティング. If a designer fails to consider stack-up and signal flow during the circuit board’s layout, even precise Placement will lead to many vias, serpentine detours, and broken connections during Routing. If Placement ignores high-current path length and decoupling capacitor distance from IC pins, Routing will never fix poor power integrity.

According to technical white papers from Cypress Semiconductor and Sierra Circuits, excellent PCB Layout reduces20–35% of PCBA rework and scrap rates. It also significantly shortens the tuning cycle from prototype to mass production. So whether you are selecting a vendor during validation or evaluating a reliable PCBA production partner, choose a manufacturer with full-process PCB design and process control capabilities.

If you plan to find a reliable PCBサプライヤー for your new project or need a PCBA quote, please contact us for one-stop PCB manufacturing and PCBA assembly services – from Layout DFM review to component sourcing and final testing. Our senior engineering team will help you control every technical detail.

結論

PCB Layout creates the blueprint. Placement positions every component precisely. Routing builds the electrical connections. These three essentials work as an inseparable trio for any successful PCBA project. This article has systematically explained their differences and connections based on IPC-2221C, IPC-2152, and the classic 3W/20H rules. We hope this helps hardware engineers improve their PCB design professionalism.

For any technical consultation on high-multilayer PCBs, HDIブラインド/埋葬バイアス, or controlled impedance PCBA mass production, feel free to follow our official technical blog for the latest DFM checklists and PCB design guides.

UGPCBのロゴ

UGPCBのロゴ