Nel campo dell'ingegneria elettronica, il conteggio degli strati di a Circuito stampato (PCB) è spesso un indicatore diretto della complessità e della sofisticazione tecnologica di un prodotto. Mentre la maggior parte degli ingegneri lavora abitualmente con 2, 4, o schede a 6 strati, con l'elettronica di consumo che impiega anche soluzioni ottimizzate in termini di costi come “pseudo-8 strati” assi (6 strati elettrici funzionali plus 2 strati isolanti per spessore)—il panorama cambia radicalmente nei server di fascia alta, schede madri per computer ad alte prestazioni, e apparecchiature di comunicazione all'avanguardia. Qui, PCB con 16, 32, o anche 64 gli strati sono comuni. Ciò solleva una questione critica: quali sono i principi di progettazione e le tecnologie di produzione che li rendono possibili PCB ad alto numero di strati? In questo articolo vengono approfonditi gli aspetti tecnici, sfide fondamentali, e soluzioni di produzione avanzate per PCB ad alto numero di strati.

Perché i PCB ad alto numero di strati? Molto più di un semplice gioco di routing

Aumentare il numero di strati di PCB non significa perseguire numeri impressionanti. Il motore fondamentale è la crescita esponenziale delle esigenze prestazionali dei moderni dispositivi elettronici. Quando la densità dei pin del chip continua ad aumentare (per esempio., Pacchetti BGA con over 2500 sfere di saldatura), le velocità del segnale entrano nel regime dei GHz (per esempio., PCIe 5.0 A 32 GT/s), e i sistemi devono gestire simultaneamente il digitale ad alta velocità, Analogico RF, e segnali ad alta potenza, tradizionale 4 oppure i pannelli a 6 strati diventano inadeguati.

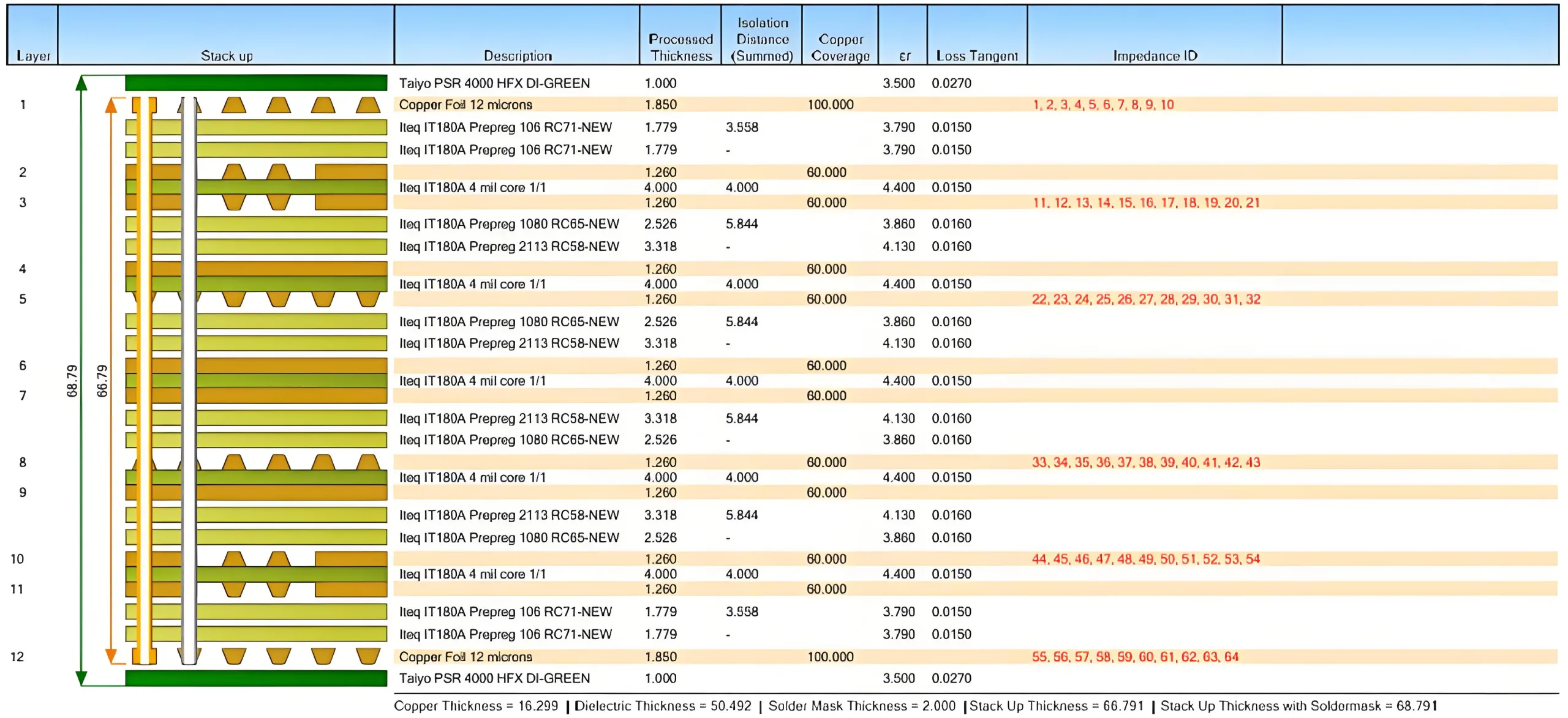

Il valore fondamentale dei PCB ad alto numero di strati risiede nel fornire ampie risorse di instradamento e piani di riferimento completi. Potrebbe essere un tipico impilamento di schede a 12 strati: Segnale 1 / Terra / Segnale 2 / Energia 1 / Segnale 3 / Terra / Segnale 4 / Energia 2 / Segnale 5 / Terra / Segnale 6. Questo simmetrico “terra-segnale-potenza-segnale-terra” impilare (seguendo le linee guida come IPC-2141A) controlla efficacemente l'impedenza e fornisce un percorso di ritorno a basso rumore per segnali ad alta velocità. Le statistiche mostrano che in apparecchiature come gli switch dei data center, progetti utilizzando PCB con 20+ i livelli possono ridurre di oltre la diafonia nei segnali di rete critici 60% (dati a cui si fa riferimento dal rapporto IPC TR-579).

Sfide di progettazione per PCB con numero elevato di strati: Al di là “Tracce di disegno”

Integrità del segnale e controllo dell'impedenza

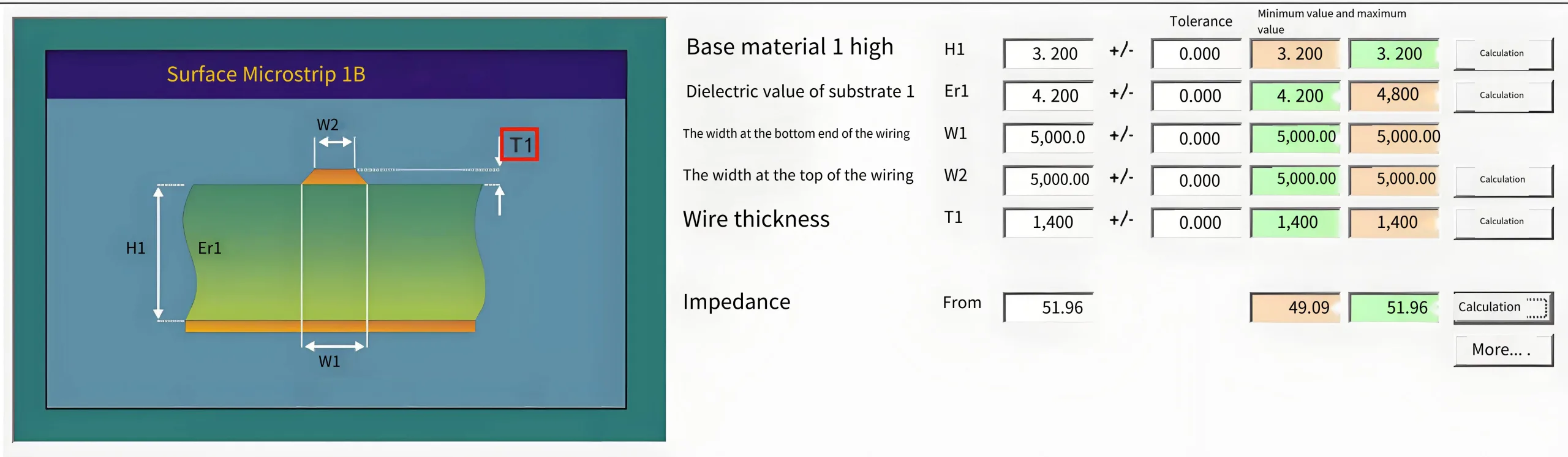

Nel design ad alta velocità, Le tracce PCB non sono più semplici collegamenti elettrici ma devono essere linee di trasmissione controllate con precisione. Deviazioni nell'impedenza caratteristica (per esempio., 50Ω single-ended, 90Differenziale Ω/100Ω) causare direttamente la riflessione del segnale, superare, e chiusura del diagramma a occhio dei dati. L'impedenza dipende principalmente dalla larghezza della traccia (W), spessore dielettrico (H), costante dielettrica (εr), e spessore del rame. Strumenti standard del settore come Polar Si9000 modellano questo utilizzando formule semplificate (per linee a microstriscia):

Z0 ≈ (87 / √(εr + 1.41)) * ln(5.98 * H / (0.8 * W + T))

dove T è lo spessore della traccia. Per il comune materiale FR-4 (εr ≈ 4.2 @1GHz), per ottenere un'impedenza di 50Ω con uno spessore dielettrico H=5 mil, la larghezza della traccia W deve essere controllata a circa 8.5 mil. Tuttavia, disuniformità nella struttura laminata dei pannelli ad alto numero di strati, l'effetto trama del vetro, e tolleranze di incisione della produzione (tipicamente ±10%) tutti introducono variazioni di impedenza. Lo standard IPC-6012D consente una deviazione del ±10% del valore misurato dall'impedenza nominale per schede ad impedenza controllata, ma le applicazioni di fascia alta ora richiedono tolleranze fino a ±7%.

Integrità dell'alimentazione e gestione termica del PCB

Man mano che il numero degli strati aumenta, la complessità della rete di distribuzione elettrica (PDN) il design cresce in modo esponenziale. Le tensioni del nucleo possono arrivare fino a 0,8 V con correnti transitorie che raggiungono centinaia di ampere. In questo scenario, l'impedenza target degli aerei di potenza deve essere estremamente bassa (per esempio., <1 Mω) per sopprimere l'ondulazione di tensione. Ciò richiede un'attenta pianificazione del posizionamento dei condensatori di disaccoppiamento, ottimizzazione della capacità interpiano tra i piani di potenza e di terra (calcolato da C = ε0 * εr * A / d, dove A è l'area di sovrapposizione e d è lo spessore dielettrico), e potrebbero richiedere livelli di potenza dedicati. Inoltre, maggiore densità di potenza grazie al routing ad alta densità (eccedente 100 W/cm² in alcune aree ASIC) richiede un raffreddamento potenziato tramite array termici, monete di rame incastonate, o substrati metallici, aggiungendo ulteriore complessità alla progettazione e all'elaborazione dello stack-up.

L'alchimia della produzione di PCB: La catena di processo di precisione per pannelli con numero elevato di strati

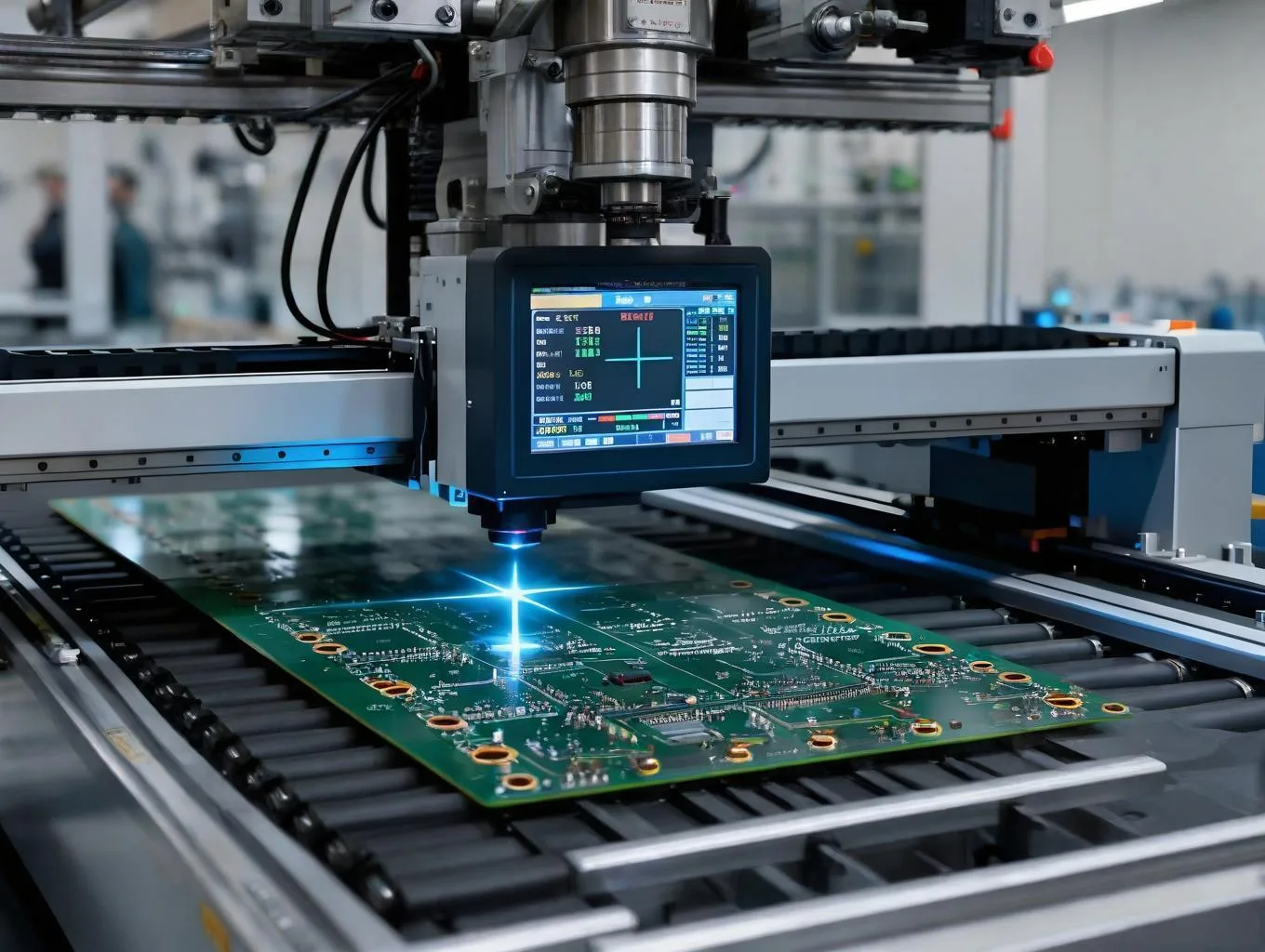

Trasformare la progettazione in realtà fisica rappresenta un'altra sfida significativa per i PCB ad alto numero di strati. Il processo principale può essere riassunto come un ciclo preciso di “laminazione – allineamento – foratura – placcatura.”

Allineamento da livello a livello: L'arte della registrazione a livello di micron

Tutti gli strati di un pannello multistrato (nuclei dello strato interno e prepreg) deve essere laminato in una singola unità ad alta temperatura e pressione. La registrazione errata dello strato può causare l'eliminazione delle tracce da parte delle frese, creare cortometraggi, o causare discontinuità di impedenza. Per una tavola a 16 strati, se l'errore medio di allineamento per strato è 25 μm (la tolleranza di registrazione grafica consentita dalla classe IPC-A-600G 3), l'errore cumulativo nel caso peggiore potrebbe superare 100 μm: sufficiente a compromettere a 0.2 Tampone BGA da mm.

Produttori leader come UGPCB affrontano questa sfida utilizzando Imaging diretto laser (LDI) E sistemi di allineamento ottico ad alta precisione. Perni di allineamento E scale fiduciarie globali inciso su ogni strato centrale, combinato con l'acquisizione della visione CCD e la regolazione del servo, può controllare la registrazione da livello a livello all'interno 15 μm (dati basati sui white paper sui processi dei principali fornitori del settore). Inoltre, analisi reologica dei materiali prevedere il flusso della resina e l'orientamento della fibra di vetro del preimpregnato durante la laminazione consente la precompensazione della deformazione dimensionale, garantire uno spessore dielettrico uniforme dopo la pressatura.

Tramite interconnessione: Dai fori passanti all'HDI a qualsiasi livello

I tradizionali fori passanti penetrano nell'intero spessore del pannello, occupando uno spazio di instradamento significativo nei PCB con un numero elevato di strati e causando lunghi problemi sul percorso di ritorno del segnale. Perciò, Interconnessione ad alta densità (ISU) tecnologia consente transizioni di livello più flessibili utilizzando vie cieche (dalla superficie allo strato interno), vie sepolte (strato interno a strato interno), E microvie (diametro ≤ 0.15 mm).

Per esempio, UN “1+N+1” Struttura dell'ISU (dove gli strati superficiali utilizzano microvia e il centro è un nucleo tradizionale a N strati) può aumentare la densità di routing di oltre 40% senza aumentare il numero totale di strati (facendo riferimento allo standard di progettazione HDI IPC-2226). Tuttavia, questo introduce complessità di processo come foratura sequenziale della laminazione, tramite riempimento e placcatura, E cicli multipli di laminazione. I produttori devono attrezzarsi macchine foratrici laser (per microvia), tappatrici verticali sottovuoto (per garantire un riempimento senza vuoti), E apparecchiature per la pulizia al plasma (per rimuovere lo striscio di trapano), ed eseguire rigorosi test delle sonde volanti E test Kelvin a quattro fili verificare l’affidabilità di ogni punto di interconnessione.

Tendenze future: Innovazione dei materiali e integrazione tra progettazione e produzione basata sulla simulazione

L'evoluzione dei PCB ad alto numero di strati continua. Man mano che le velocità del segnale avanzano verso 56 Gbps e oltre utilizzando la modulazione PAM4, materiali a bassa perdita (come Panasonic MEGTRON 6, Serie Rogers RO4000) con εr basso come 3.2 e fattori di dissipazione (Df) sotto 0.002 vengono adottati. Contemporaneamente, componenti incorporati (come resistori e condensatori sepolti) E integrazione di pacchetti di semiconduttori (per esempio., EMIB di Intel, SoIC di TSMC) stanno confondendo i confini tra PCB e circuiti integrati.

Per progettisti e specialisti degli acquisti, selezionando un qualificato conteggio di strati elevati Fornitore di PCB è fondamentale. Oltre a concentrarsi sul loro capacità massima del livello (per esempio., produzione di massa stabile di 32 strati), Controllo dell'impedenza capacità (se forniscono rapporti sui test di impedenza), E Livello del processo HDI (dimensione minima del foro/larghezza della traccia), è fondamentale valutarli servizi di supporto alla progettazione (come la simulazione SI/PI e la consulenza sull'ottimizzazione dello stack-up) E sistema di controllo qualità (adesione alla Classe IPC 3 standard e disponibilità di attrezzature di ispezione complete come AOI, AVI, 3D-ray).

Cerco un'alta affidabilità, ad alte prestazioni PCB multistrato soluzione? Contattare un fornitore professionale con capacità sull'intera catena, dalla simulazione della progettazione alla produzione di precisione, per ottenere un proposta di design impilabile personalizzato E preventivo istantaneo per il tuo progetto è il primo passo fondamentale verso il successo. Nell’era dell’Internet of Everything e dell’esplosione computazionale, I PCB ad alto numero di strati non sono più solo portatori; costituiscono il cardine fondamentale che definisce i limiti prestazionali dei sistemi elettronici.

LOGO UGPCB

LOGO UGPCB

Non sono sicuro di dove hai preso le tue informazioni, ma ottimo argomento. Ho bisogno di dedicare un po' di tempo a imparare di più o a capire di più. Grazie per le meravigliose informazioni, stavo cercando queste informazioni per la mia missione.