Dominar o controle de impedância de PCB: Estratégias avançadas para design de circuito de alta velocidade

Figura 1: Rastreios controlados por impedância crítica em design de PCB multicamadas

O papel crítico do controle de impedância na eletrônica moderna

Por que a impedância corresponde a questões em designs de alta frequência

Em sistemas digitais de alta velocidade operando acima 1 GHz, PCB traços se transformam de condutores simples para linhas de transmissão complexas onde impedância característica (Z₀) torna -se fundamental. Quando as incompatibilidades Z ocorrem entre componentes, Reflexões de sinal podem alcançar 35% de poder incidente, causando erros de distorção e tempo da forma de onda que prejudicam o desempenho do sistema.

Principais conseqüências do controle de impedância fraca:

- Degradação da integridade do sinal: Degradação do tempo de subida até 40% nas interfaces DDR4

- Picos de radiação EMI: Linhas incompatíveis podem aumentar as emissões irradiadas em 15-20dB

- Questões de integridade de energia: As descontinuidades do caminho de retorno criam salto no solo

Conceitos de impedância fundamental

Fórmula de impedância característica para microfita:

Z₀ = frac{87}{\sqrt{e_r + 1.41}} \Ln esquerda(\Frac{5.98H}{0.8C + T}\certo)

Onde:

- ε_r = constante dielétrica (FR4: 4.2-4.7, Rogers 4350b: 3.48)

- H = espessura dielétrica (milímetros)

- W = largura do rastreamento (milímetros)

- T = espessura de cobre (onças)

Cálculo de pares diferenciais:

Z_{Dif} = 2z₀ esquerda(1 - 0.48e^{-0.96S/h}\certo)

S = espaçamento de pares, H = altura dielétrica

Cinco pilares de engenharia de impedância de PCB

1. Matriz de seleção de material

| Tipo de material | ε_r @10GHz | Perda tangente | ÍNDICE DE CUSTO |

|---|---|---|---|

| FR-4 | 4.5 | 0.02 | $ |

| Rogers 4350b | 3.48 | 0.0037 | $$$ |

| I -RA ILHA | 3.45 | 0.0031 | $$$$ |

| PTFE composto | 2.2-3.0 | 0.0009 | $$$$$ |

Mesa 1: Comparação laminada de alta frequência

2. Princípios de arquitetura de empilhamento

Inclinação HDI ideal de 12 camadas para sinais de 25 Gbps:

- L1: Sinal (0.5onças)

- L2: Chão

- L3: Sinal (3.5MIL DIELECTRIC)

- L4: Poder

- L5: Sinal (De alta velocidade)

- L6: Chão

… Estrutura simétrica espelhada

Parâmetros críticos:

- Tolerância à espessura dielétrica: ± 10% máximo

- Rugosidade de cobre: <2μm rms for >10GHz

- Laminação seqüencial para continuidade da impedância

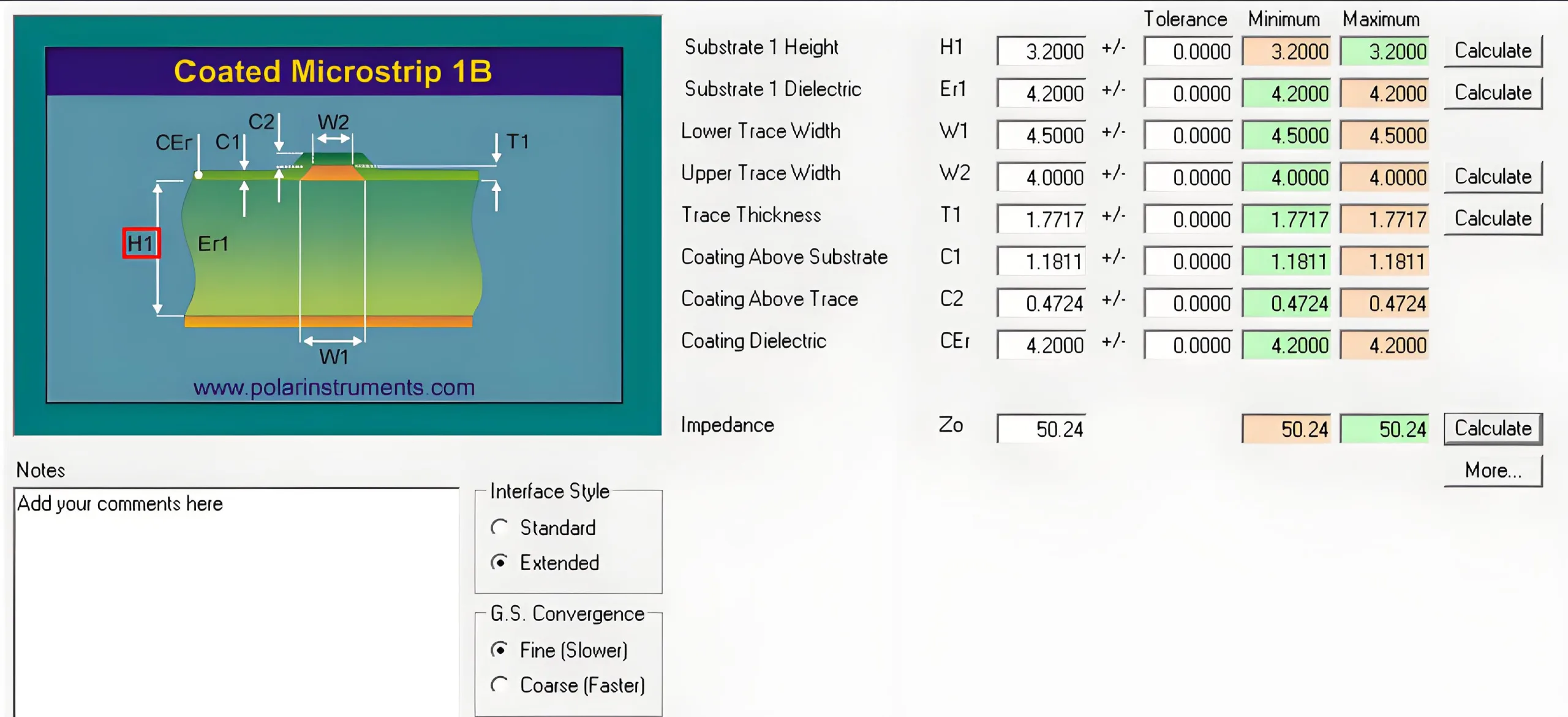

3. Metodologias de cálculo avançado

Processo de validação de impedância de três etapas:

- Estimativa inicial:

Use fórmula empírica:W pid frac{100H}{\sqrt{e_r}} \Quad (\texto{50Ω microStrip}) - Simulação de precisão:

- Polar Si9000 para estruturas de várias camadas

- Rogers MWI-2017 para linhas de RF/microondas

- Verificação pós-produção:

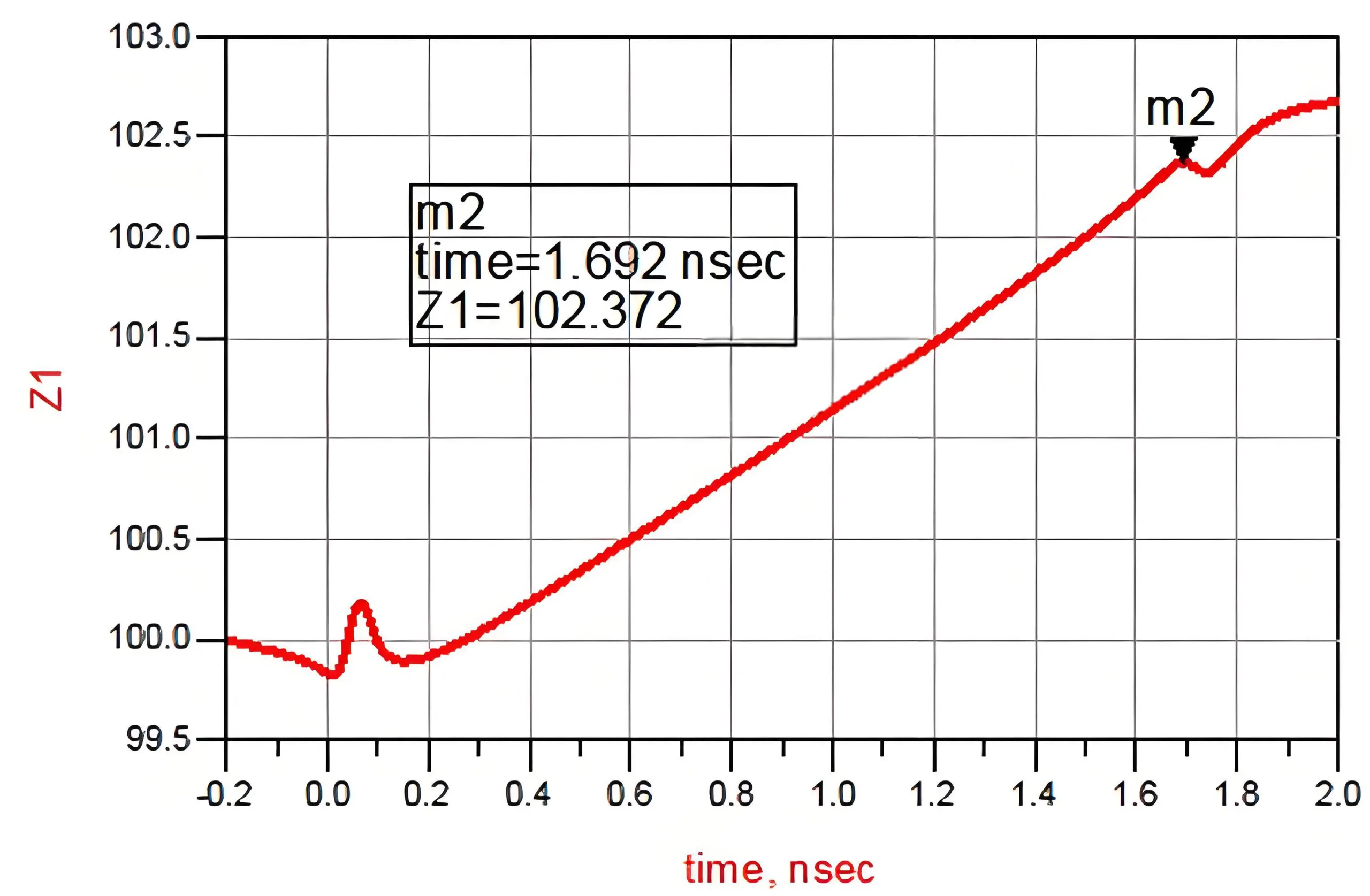

Medições de TDR com <5% tolerância

Figura 2: Fluxo de trabalho de engenharia de impedância de PCB

Figura 2: Fluxo de trabalho de engenharia de impedância de PCB

4. Controles de processo de fabricação

Fatores críticos de tolerância:

| Parâmetro | Tolerância típica | Impacto em z₀ |

|---|---|---|

| Largura de gravação | ± 0,5mil | ± 3Ω |

| Espessura dielétrica | ± 10% | ± 8Ω |

| Peso de cobre | 0,2oz | ± 2Ω |

| SolderMask | 0.3-0.5mil | ± 1,5O |

Dados dos padrões IPC-2141A

Estratégias de mitigação:

- Use obras de arte compensadas (0.75× fator de gravação)

- Implementar inspeção óptica automatizada (AOI)

- Especificar cupons de teste de impedância controlada

5. Ecossistema de ferramentas de ponta

Soluções de software líder do setor:

- Instrumentos polares SI9000E

- 2D Solver de campo com 47 Modelos de linha de transmissão

- Processamento em lote para designs complexos

- Rogers MWI-2017

- Especializado para designs de microondas até 110 GHz

- Banco de dados de material integrado com 50+ substratos

- Cadence Sigrity Aurora

- 3Dem simulação com <2% margem de erro

- DDR5/PCIE6.0 Verificação de conformidade

- Profiler de impedância de altium

- Visualização de impedância em tempo real

- Validação automatizada de empilhamento

Diretrizes de design prático para engenheiros

Regras de ouro para designs iniciantes à direita

- 3W regra para o controle de diafonia:

S ≥ 3 × W Quad (\texto{Onde s = espaçamento de rastreamento}) - Prioridades de correspondência de comprimento:

- Pares diferenciais: <5Mil Intra-Par-Par Incompation

- Sinais de ônibus: <100PS Atraso Skew

- Via técnicas de otimização:

- Use 8-12mil diâmetro para sinais de 10 Gbps

- Pano de fundo para o comprimento do stub <15% de tempo de aumento

- Estratégias de rescisão:

Tipo Aplicativo Custo de energia Série 22Ω Fonte-End Baixo Paralelo 50Ω Ponto final Alto Capacitivo CA. Interfaces de memória DDR Médio

Tendências futuras no gerenciamento de impedância

Tecnologias emergentes Impacto

- 5G MMWAVE Desafios:

- 28/39As bandas GHz requerem tolerância a ± 1Ω

- Ablação a laser para controle de largura de linha 2μM

- Integração avançada de embalagens:

- 3D ic com correspondência de impedância TSV

- Substrato híbrido Designs PCB-Flex

- Otimização de impedância acionada por IA:

- Redes neurais prevendo variações de fabricação

- Design generativo para soluções de múltiplas restrições

Tomar medidas para obter uma cotação

UGPCB mantém uma posição de liderança em ambos os PCB (Placa de circuito impresso) e PCBA (Conjunto da placa de circuito impresso) setores, tornando -o um líder do setor. O UGPCB possui uma equipe de design de PCB altamente experiente que se destaca no controle de impedância de PCB, classificação na vanguarda da indústria. Se você tiver alguma dúvida ou requisitos de design relacionados à impedância de PCB, Entre em contato com nossa equipe técnica profissional para obter suporte técnico ou agir e solicite uma cotação competitiva hoje.

LOGOTIPO UGPCB

LOGOTIPO UGPCB