"لماذا تتلف الرقائق عندما أتعامل مع لوحة الدائرة عادة?يشعر العديد من المهندسين بالارتباك عند مواجهة تلف الدائرة الناتج عن التفريغ الكهروستاتيكي (البيئة والتنمية المستدامة). في الحقيقة, يمكن لجسم الإنسان أن يولد جهدًا كهروستاتيكيًا يصل إلى عشرات الآلاف من الفولتات، وهو ما يتجاوز بكثير حد التسامح لمعظم المكونات الإلكترونية.

حتى الأكثر دقة مركبات ثنائي الفينيل متعدد الكلور (لوحات الدوائر المطبوعة) يمكن أن تكون عرضة لESD. قد تتسبب اللمسة غير المقصودة في فشل رقائق بقيمة آلاف الدولارات على الفور.

على خلفية الأجهزة الإلكترونية المتطورة بشكل متزايد اليوم, لم تعد الحماية من التفريغ الكهروستاتيكي (ESD) خيارًا اختياريًا ولكنها إجراء ضروري لضمان موثوقية المنتج. ستحلل هذه المقالة بعمق نقاط التصميم الرئيسية وعوامل التصنيع الحرجة لحماية PCB ESD, مساعدة منتجاتك على مقاومة هذا "البرق غير المرئي".

1. تهديدات البيئة والتنمية المستدامة: التأثير المميت للبرق المصغر غير المرئي

يمكن تصور ESD على أنه برق مصغر غير مرئي. ممارسة الأنشطة اليومية مثل المشي, خلع السترات, أو حتى التقاط صندوق بلاستيكي يمكن أن يولد كهرباء ساكنة. غالبًا ما يصل جهد هذه الكهرباء الساكنة إلى عدة آلاف من الفولتات, أو حتى عشرات الآلاف من الفولتات.

جسم الإنسان نفسه هو في الواقع أكبر مولد للكهرباء الساكنة. خاصة في مواسم الجفاف, قد يحدث ESD في اللحظة التي تصل فيها إلى PCB. عناصر تبدو غير مهمة مثل أجهزة الكمبيوتر المكتبية البلاستيكية, سجاد من الألياف الكيماوية, وصناديق التغليف الرغوية يمكن أن تصبح جميعها "متواطئة" مع الكهرباء الساكنة.

تضر البيئة المستدامة بمركبات ثنائي الفينيل متعدد الكلور في شكلين رئيسيين:

- الضرر الصعب: وهذا هو الضرر الأكثر مباشرة ووضوحا. سوف يقوم ESD بتفكيك الدوائر الصغيرة داخل الشريحة على الفور, مما يسبب ضررا دائما للرقاقة. نتيجة ل, سيتوقف ثنائي الفينيل متعدد الكلور عن العمل تمامًا, أو وظائف محددة (مثل المنافذ التسلسلية أو ADC) سوف تفشل مباشرة.

- الضرر المزمن: وهذا أكثر خفية وإزعاجا. قد لا يؤدي ESD إلى تدمير الشريحة بالكامل, ولكنها يمكن أن تسبب أضرارًا جزئية لطبقات الأكسيد الداخلية والهياكل الأخرى. ربما لا يزال PCB يعمل بشكل طبيعي الآن, ولكنها سوف تصبح غير مستقرة ولها عمر خدمة أقصر. قد يتعطل فجأة بعد بضعة أيام أو تحت درجات حرارة معينة. يعد هذا الفشل المتقطع هو الأصعب في استكشاف الأخطاء وإصلاحها أثناء تصحيح الأخطاء ويستهلك الكثير من الوقت والجهد.

2. الثنائيات TVS: نظام الحماية من الصواعق الدقيق للدوائر

TVS (مثبط الجهد العابر) الثنائيات هي خط الدفاع الأول ضد تهديدات ESD ومكونات الحماية الأكثر فعالية. إنهم يتصرفون مثل "حراس أمن إشارات الدائرة" - حيث يحافظون على حالة المعاوقة العالية في الظروف العادية. بمجرد اكتشاف نبض ESD, يتحولون على الفور إلى حالة مقاومة منخفضة, تحويل نبض الجهد العالي إلى الأرض وحماية الرقائق الخلفية.

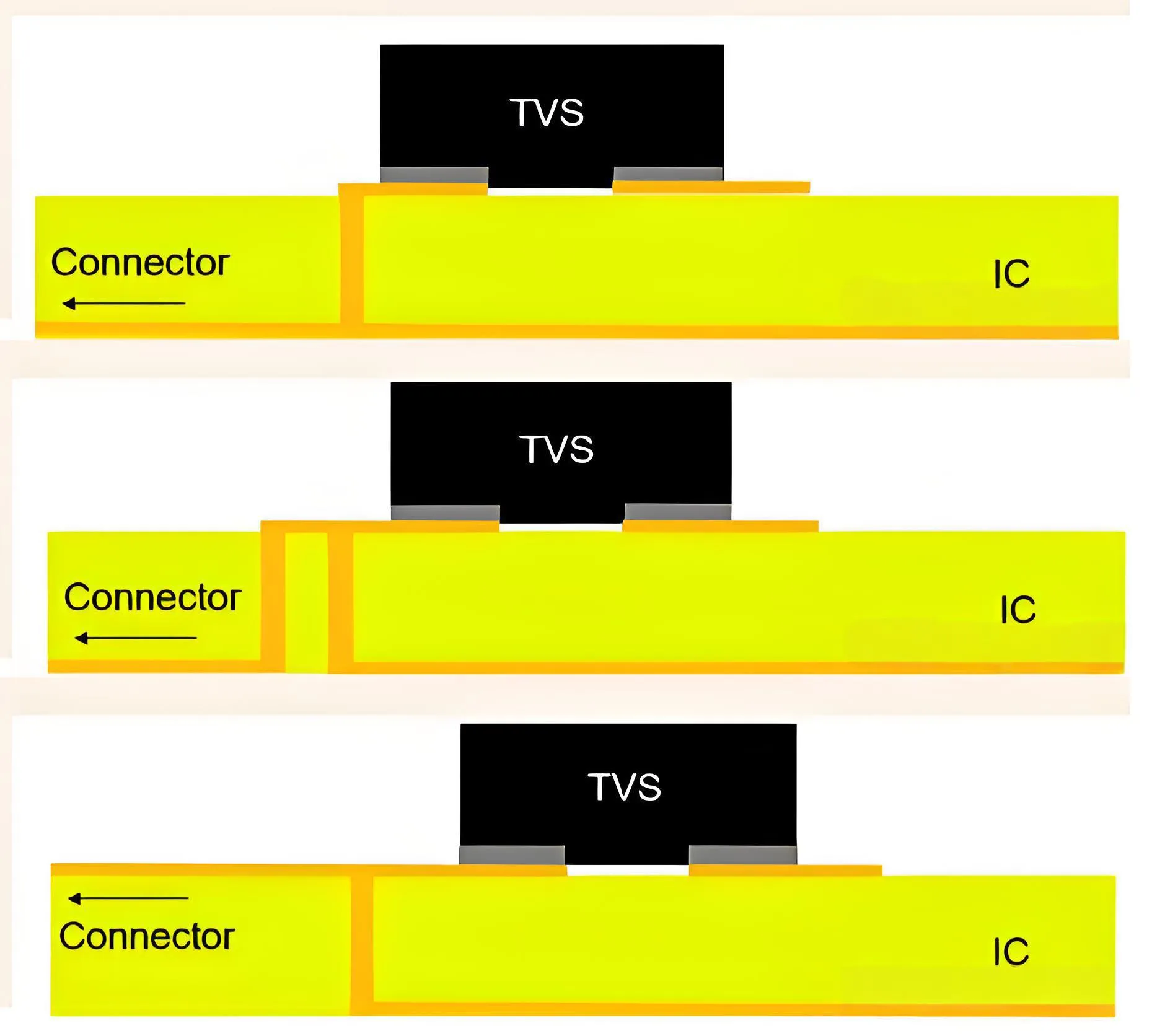

2.1 القواعد الذهبية لتخطيط TVS

الحث الطفيلي هو العدو الأكبر لأداء TVS. تؤثر الحث الطفيلي في الدائرة - بما في ذلك الحث الطفيلي لدبابيس TVS نفسها - على جهد التثبيت (رأس المال الاستثماري) في الواجهة الخلفية لـ IC عند حدوث ESD أو حدوث زيادات.

يتبع تأثير الحماية لـ TVS الصيغة: VCL = VBR + آر دي × إي بي بي. فيما بينها:

- RD هي السعة الطفيلية لـ TVS نفسها; تتمتع المنتجات ذات قيم RD الأصغر بجهد تثبيت أفضل ويمكنها حماية المرحلية بشكل أكثر فعالية.

- IPP هو التيار الذي يمر عبر TVS أثناء لحظة الاختبار.

لتعظيم تأثير الحماية من TVS, يجب عليك التأكد من أن الاتصال الأرضي قصير قدر الإمكان ووضع TVS بالقرب من مصدر ESD قدر الإمكان. هذا لا يقلل فقط من EMI (التداخل الكهرومغناطيسي) على PCB ولكنه يقلل أيضًا من الاقتران مع المسارات الأخرى. يوفر اختيار جهاز TVS بوقت استجابة أقل من 1ns حماية مثالية للواجهات عالية السرعة - وهو أمر بالغ الأهمية لـ PCBA (مجموعة لوحة الدوائر المطبوعة) مصداقية.

3. تخطيط ثنائي الفينيل متعدد الكلور والتأريض: مؤسسة حماية البيئة والتنمية المستدامة

معقول تخطيط ثنائي الفينيل متعدد الكلور والتصميم التأريض هما حجر الزاوية في حماية البيئة والتنمية المستدامة. حتى بدون مكونات حماية إضافية, يمكنهم تحسين مناعة المنتج من أجل البيئة المستدامة بشكل كبير.

3.1 النقاط الرئيسية لتخطيط ثنائي الفينيل متعدد الكلور

- يجب أن تكون خطوط الإشارة عالية السرعة بعيدة عن حافة اللوحة بمقدار ≥3 مم, بينما يجب أن تكون الإشارات الحساسة ذات التردد المنخفض على بعد ≥2 مم.

- يجب أن تكون الإشارات الحرجة مثل خطوط الساعة وخطوط إعادة الضبط محاطة بالأرض (التدريع الأرضي). قم بترتيب الخطوط الأرضية على كلا الجانبين وأضف فتحات أرضية كل 50 مم.

- يجب أن تكون جميع العبوات المعدنية المكشوفة مؤرضة بنقطة واحدة من خلال مقاومة 1MΩ لتجنب تشكيل حلقة منخفضة المعاوقة من خلال التأريض المباشر.

- يجب الحفاظ على مسافة زحف تبلغ ≥5 مم بين مكونات اتصال المستخدم (مثل الأزرار والمقابض) واللوحة الرئيسية. استخدم رغوة موصلة أو نوابض معدنية لتحقيق اتصال متساوي الجهد.

- ضبط فجوات الشرارة (مع تباعد 0.2 مم - 0.5 مم) عند موضع Pin1 للموصل ونقطة التأريض للحاوية المعدنية. يمكن لهذه التدابير توجيه تيار ESD بشكل فعال لتفريغه بأمان وتجنب تلف الدوائر الحساسة.

3.2 مبادئ لتصميم التأريض ثنائي الفينيل متعدد الكلور

عند تصميم طبقة مزدوجة أو ثنائي الفينيل متعدد الكلور متعدد الطبقات, حاول التأكد من مستوى أرضي كامل وواسع المساحة. يشبه المستوى الأرضي الكامل سهلًا واسعًا، حيث يمكنه امتصاص طاقة ESD وتشتيتها بسرعة, منع الطاقة من التراكم في نقطة واحدة. في نفس الوقت, فهو يوفر مسار تفريغ فعال لثنائيات TVS.

أثناء تخطيط ثنائي الفينيل متعدد الكلور, املأ الشبكة الأرضية بالنحاس وتأكد من أن النحاس الأرضي يغطي أكبر قدر من المساحة الفارغة على اللوحة (بدون آثار) قدر الإمكان. لجميع الواجهات الخارجية (مثل منافذ USB ومآخذ الطاقة DC), قم بتوصيل العلبة المعدنية بأرضية اللوحة من خلال مكثف عالي الجهد أو مباشرة. من هنا, سيتم تحويل ESD من خلال العلبة أولاً قبل دخول الدائرة - مما يعزز حماية PCB ESD على مستوى الواجهة.

4. عملية التصفيح: حاجز الحماية الداخلي لمركبات ثنائي الفينيل متعدد الكلور متعدد الطبقات

في مركبات ثنائي الفينيل متعدد الكلور متعدد الطبقات, ترتبط جودة عملية التصفيح ارتباطًا مباشرًا بقدرة الحماية الداخلية للوحة من التفريغ الكهروستاتيكي (ESD).. إذا كان العازل بين طبقتين موصلتين رقيقًا جدًا, يمكن لـ ESD عالي الجهد أن يعطله بسهولة, مما يسبب ضررا دائما.

4.1 الدور الأساسي للتحضير المسبق

prepreg (مادة مركبة مشربة مسبقًا) يعمل بمثابة عازل عازل بيني في مركبات ثنائي الفينيل متعدد الكلور متعدد الطبقات. إنها "مادة مركبة وظيفية" يتم التحكم فيها من خلال عمليات التصنيع الدقيقة, مع ميزته الأساسية وهي أن الراتينج في "حالة شبه معالجة للمرحلة B" - وهي خاصية أساسية لتحقيق تصفيح الألواح متعددة الطبقات.

لا يوفر Prepreg الترابط الجسدي فحسب، بل يحقق أيضًا ثلاثة تأثيرات: العزل الكهربائي + الدعم الهيكلي. يحدد أداء العزل وخصائص العزل الكهربائي بشكل مباشر الموثوقية الكهربائية لثنائي الفينيل متعدد الكلور: بعد المعالجة, مقاومة الحجم هي ≥10¹⁴Ω·سم, ومقاومة جهد الانهيار هي ≥20kV/mm, والتي يمكن أن تمنع تسرب الطبقة البينية - وهو أمر بالغ الأهمية لمنع تلف الطبقة البينية الناجم عن ESD.

تتضمن المعلمات الأساسية لبرنامج Prepreg:

- محتوى الراتنج (أرسي٪): عادة 50% ~ 70%, الذي يحدد قوة الترابط بين الطبقات وسمك الطبقة العازلة.

- الانسيابية: 15~ 30 ملم.

- درجة حرارة انتقال الزجاج (تيراغرام): عادة 150 ~ 200 درجة مئوية.

- ثابت العزل الكهربائي (DK): 4.2±0.2 لـ FR-4 التمهيدي العادي.

4.2 مراقبة الجودة لعملية التصفيح

لضمان جودة التصفيح, معامل التمدد الحراري (CTE) يجب أن يتطابق Prepreg مع الألواح الأساسية FR-4 والرقائق النحاسية. إذا تجاوز انحراف CTE للمحور Z 5 جزء في المليون/درجة مئوية, من المحتمل أن يحدث تكسير الطبقات البينية أثناء دورة درجة الحرارة.

أثناء التصفيح:

- عندما تكون درجة حرارة الطبقة الوسطى 80 ~ 130 درجة مئوية, يجب ألا يتجاوز فرق درجة الحرارة بين الطبقة العليا للوحة الحاملة والطبقة الوسطى 25 درجة مئوية, ويجب ألا يتجاوز معدل التسخين 1.3~5 درجة مئوية/دقيقة.

- عندما تصل درجة الحرارة إلى 85±5 درجة مئوية, تحديد زمن التحول من الضغط المنخفض إلى الضغط المتوسط.

- عندما تصل درجة الحرارة إلى 110 ± 5 درجة مئوية, تحديد زمن التحول من الضغط المتوسط إلى الضغط المرتفع.

في تصنيع ثنائي الفينيل متعدد الكلور الحديث, لقد أدت تقنية الضغط الفراغي إلى تحسين جودة التصفيح بشكل ملحوظ. بيئة الفراغ تتجنب تكوين الفقاعات والفراغات, ضمان التدفق الموحد وملء راتينج Prepreg - مما يعزز مقاومة PCB متعدد الطبقات لانهيار ESD.

5. العمليات المتقدمة والتحقق من الجودة

مع تطور الأجهزة الإلكترونية نحو الترددات العالية والكثافة العالية, تواجه حماية البيئة والتنمية المستدامة تحديات جديدة وتتطلب حلول عملية أكثر تقدمًا.

5.1 تحسينات العملية للتطبيقات الخاصة

- سيناريوهات الاتصالات عالية التردد: Prepreg منخفض DK (دك = 3.48 ± 0.03, دف <0.004) يمكن أن يلبي متطلبات نقل الإشارة 28 جيجا هرتز/77 جيجا هرتز مع توفير حماية عزل موثوقة - وهو أمر بالغ الأهمية للحفاظ على سلامة الإشارة ومقاومة ESD في 5G أو مركبات ثنائي الفينيل متعدد الكلور لرادار السيارات.

- ألواح نحاسية سميكة (≥3oz): اعتماد "التصفيح المسبق للمحتوى المنخفض من الراتينج بطبقة مزدوجة" (52%±1% لكل طبقة, إجمالي محتوى الراتنج 56%) جنبا إلى جنب مع التصفيح عالي الضغط 8MPa. يمكن أن يؤدي ذلك إلى زيادة مقاومة جهد انهيار الطبقة العازلة إلى 3500 فولت، مما يعزز حماية البيئة والتنمية المستدامة لمركبات ثنائي الفينيل متعدد الكلور المرتبطة بالطاقة.

- مؤشر التنمية البشرية (ربط عالية الكثافة) لوحات: تتطلب قابلية منخفضة للتدفق المسبق (18± 2 مم) + التصفيح الفراغي لمعالجة مشكلة تجاوز راتنجات ميكروفيا 0.075 مم. لا تعمل معالجات العمليات الخاصة هذه على تحسين أداء المنتج فحسب، بل تعمل أيضًا على تعزيز قدرة الحماية الداخلية للتفريغ الإلكتروستاتيكي (ESD) للوحة الدائرة.

5.2 التحقق من الجودة ومعايير الاختبار

يعد نظام التحقق من الجودة ذو الحلقة المغلقة أمرًا بالغ الأهمية لضمان قدرات حماية PCB ESD. ويشمل:

- التفتيش الوارد: استخدم مطياف الأشعة تحت الحمراء لاختبار المحتوى المتطاير ومطياف العزل الكهربائي للتحقق من استقرار Dk/Df.

- مراقبة العملية: جمع بيانات درجة الحرارة والضغط في الوقت الحقيقي أثناء التصفيح.

- التحقق من المنتج النهائي: إجراء اختبار قوة تقشير الطبقات البينية واختبار مقاومة العزل.

يجب أن يستوفي التحقق النهائي من الحماية من التفريغ الكهروستاتيكي (ESD). IEC61000-4-2 المستوى 4 معيار, أي., اختبار تفريغ التلامس يصل إلى ±8 كيلو فولت وتفريغ الهواء حتى ±15 كيلو فولت. بعد الاختبار, يجب استيفاء المعايير التالية:

- سلامة الإشارة (افتتاح مخطط العين >70%).

- معدل خطأ البت (<1×10^-12).

- التشغيل التقلبات الحالية (<± 5 ٪).

- إعادة ضبط الأوقات (0 مرات/دورة الاختبار).

أصبحت عمليات تصنيع الرقائق اليوم متطورة بشكل متزايد, ولكن هذا لا يعني أننا قادرون على خفض مستوى يقظتنا تجاه التعليم من أجل التنمية المستدامة. على العكس تماما, مع تقلص أحجام الدوائر وانخفاض جهد التشغيل, تصبح المكونات أكثر حساسية للتفريغ الكهروستاتيكي.

أصبحت عمليات تصنيع الرقائق اليوم متطورة بشكل متزايد, ولكن هذا لا يعني أننا قادرون على خفض مستوى يقظتنا تجاه التعليم من أجل التنمية المستدامة. على العكس تماما, مع تقلص أحجام الدوائر وانخفاض جهد التشغيل, تصبح المكونات أكثر حساسية للتفريغ الكهروستاتيكي.ينظر مهندسو PCB المتميزون إلى حماية ESD في مرحلة التصميم الأولية, دمج التدابير الوقائية في "الحمض النووي" للمنتج. وهذا ليس تحديًا تقنيًا فحسب، بل هو أيضًا اختبار للمسؤولية والكفاءة المهنية - لأن أفضل إصلاح للأخطاء هو منع حدوث الأعطال في المقام الأول.

شعار UGPCB

شعار UGPCB