Introdução: A guerra em escala de milímetro no design de PCB DDR5

O salto de DDR4 para DDR5 marca uma mudança de paradigma: As taxas de sinal surgem de 3,200 Mt/s para 6,400 Mt/s enquanto as tensões de operação despencam para 1.1V. Este duplo desafio transforma PCB roteamento da engenharia simples de conectividade para a guerra de precisão em escala de milímetro. Dados do setor revelam que 80% de falhas de design do DDR5 se originam dos problemas de roteamento, com 90% evitável através da simulação pré-layout. Este artigo disseca cinco armadilhas críticas de roteamento de DDR5, Suportado por dados empíricos e estudos de caso, Entregando soluções acionáveis para profissionais de PCB.

1. DDR5 Características físicas: Por que os métodos tradicionais de design de PCB falham

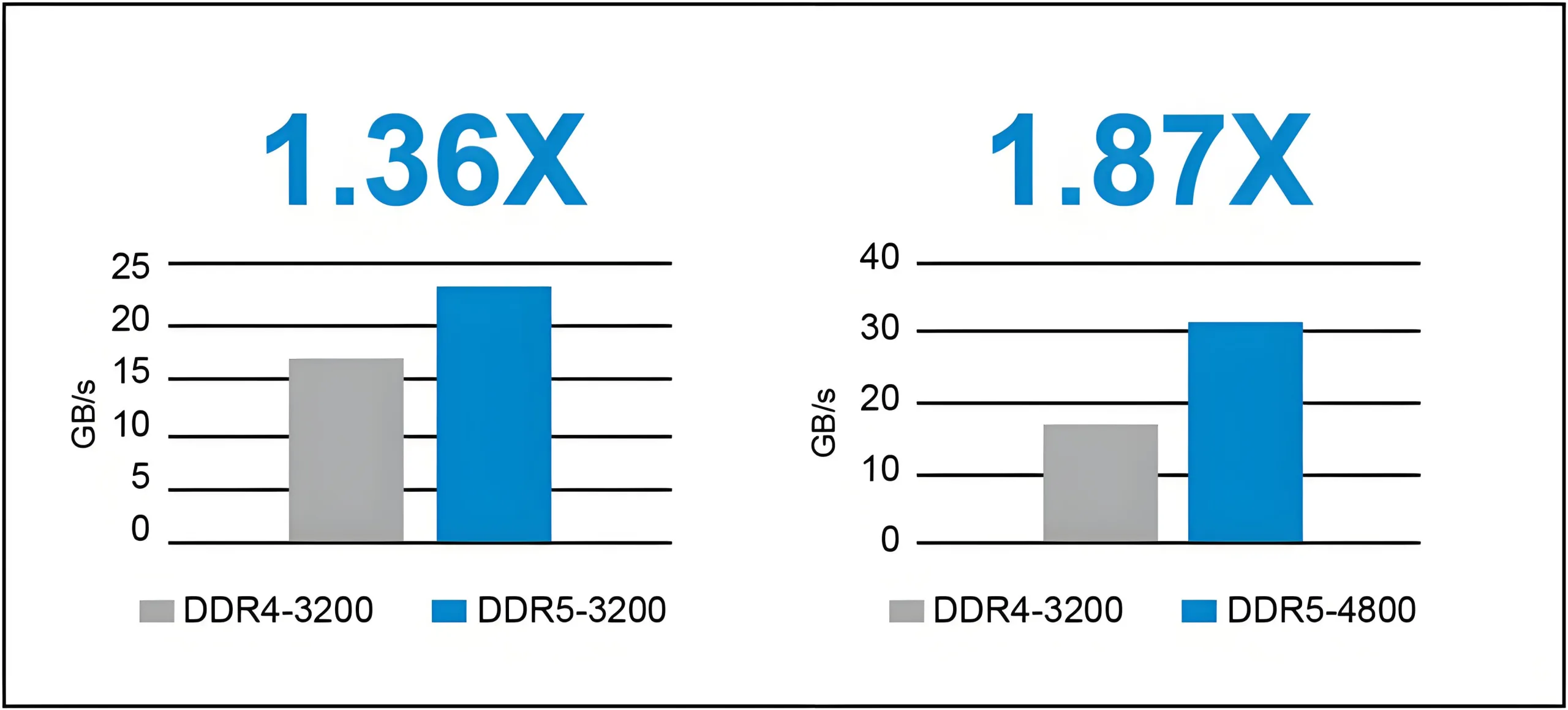

1.1 Taxa de sinal e revolução da largura de banda

Para DDR5-6400, A frequência de relógio efetiva atinge 3,200 MHz, com taxas de borda tão rápido quanto 0.5 ps (20-80% tempo de subida). Isso desencadeia:

-

Efeito agravado da pele: Correntes de alta frequência concentram-se em superfícies de condutores, reduzindo a espessura efetiva de cobre para 0.66 μm em 10 GHz.

-

Escalada de perda dielétrica: Substratos FR4 exibir uma perda tangente (Df) de 0.02 no 10 GHz, causando >3 Atenuação do sinal de dB/polegada.

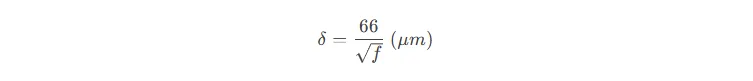

Validação da fórmula (Profundidade da pele):

No F = 10 GHz, Δven0,66 μm,Deixando de 1 onças de cobre tradicional (35 μm) com <2% utilização.

2. Cinco campos de minas e contramedidas de roteamento DDR5

2.1 Campo minado 1: Erro de tempo - o limite de sobrevivência de ± 15ps

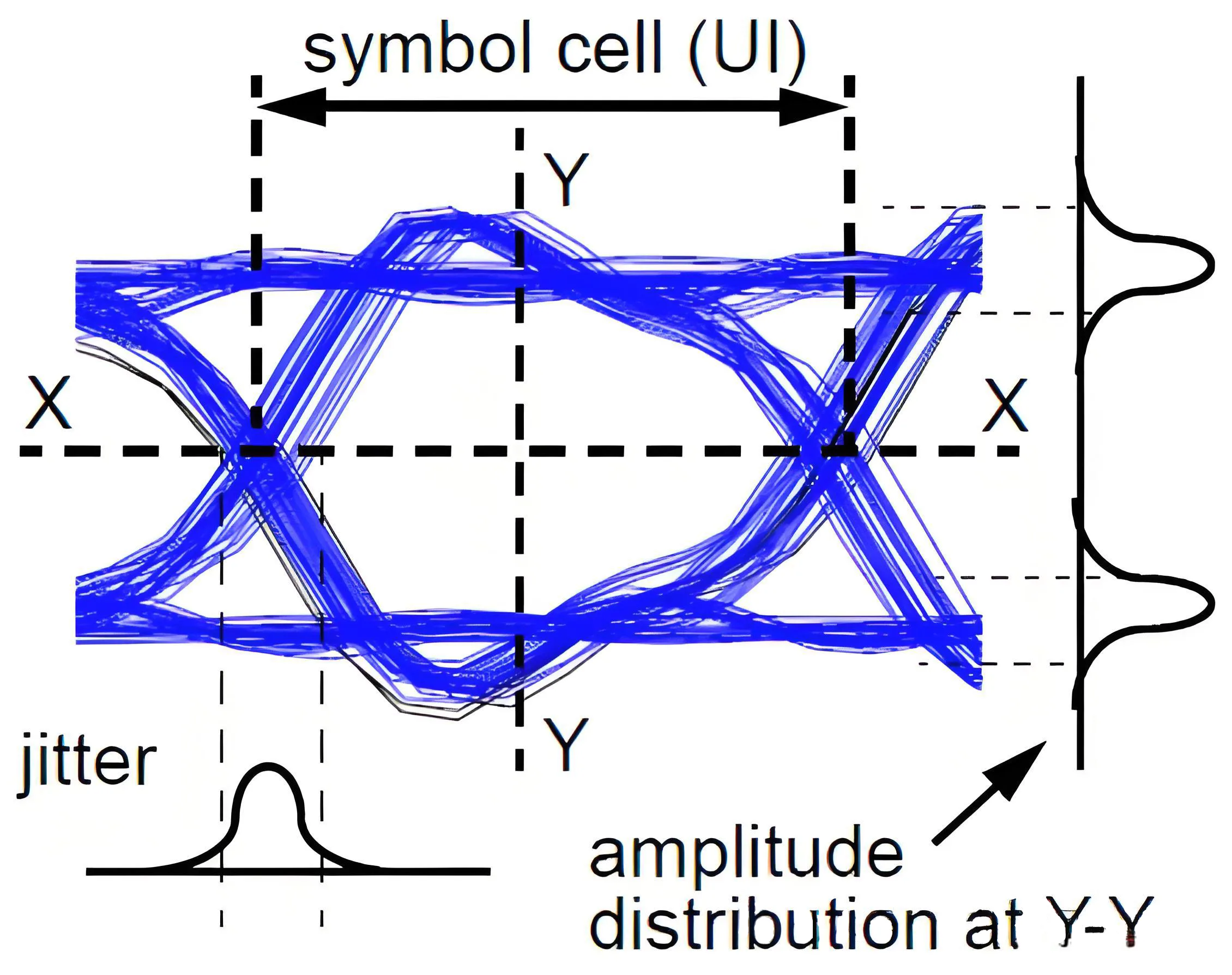

Impacto: Uma incompatibilidade de 5 mil de comprimento introduz ± 12ps atraso, largura de olho horizontal em colapso por 30%.

Estudo de caso: Um design de GPU sofreu degradação de BER de 10-12 para 10-7 Devido ao distorção de 8 mil dq/dqs.

Soluções:

-

3D Compensação de roteamento: Substitua os meandros de 90 ° por serpentinos de 45 °, reduzindo a capacitância parasita por 30%.

-

Calibração de tempo dinâmico: Realize simulações de Monte Carlo (Cadência Sigridade) cobrindo ± 10% de variações de processo.

Fórmula (Margem de tempo):

Tmargem= Tciclo-(Tco+Tvoo+TJitter)

Para DDR5-6400 (Tciclo= 0,3125 ), alertas do sistema acionam quando Tmargem<50 ps.

2.2 Campo minado 2: Descontinuidade de impedância - o sinal de 5Ω tsunami

Risco: Por meio da incompatibilidade de impedância causas >15 DB de perda de retorno, colapsando a altura vertical do olho por 40%.

Dados: Cada um não otimizado via adição 0.2 perda de inserção de banco de dados @5 ghz.

Soluções:

-

Via revolução: Implementar vias a laser-clínicas (≤4mil) com compensação antipad, Variação de impedância limitadora para ± 3Ω.

-

Otimização do bloco: Use almofadas elípticas (1.5:1 proporção de aspecto) para reduzir os efeitos capacitivos por 20%.

Fórmula (Via modelo de impedância):

ZVIA≈87ϵr⋅ln(5.98h/(0.8D1+D2))

Onde : espessura dielétrica, D1: via diâmetro, : diâmetro da almofada.

2.3 Campo minado 3: Atraso na camada cruzada-o efeito de borboleta de 0,1ps/mm

Efeito da tecelagem de fibra: Variação constante dielétrica (Δϵr = 0,3) de periodicidade de fibra de vidro causas 0.6 Ps/polegada de atraso.

Soluções:

-

Alinhamento do eixo Z.: Sinais de grupo de bytes de rota a ± 45 ° ângulos para cancelar a anisotropia dielétrica.

-

Compensação de camadas cruzadas: Pré -carga Substrato DK/DF Dados em ferramentas EDA para correção de atraso automático.

2.4 Campo minado 4: Ripple de potência - a reação em cadeia nuclear de 1MV

Sensibilidade: 50MV Ripple a 1,1V de suprimento aumenta o jitter de motorista por 20%.

Simulação: A impedância alvo do PDN deve ser ≤2 MΩ a 100 MHz - 5x mais rigorosa que os designs tradicionais.

Soluções:

-

3D Matriz do capacitor: Implantar 0,1μF (0402) + 10nf (0201) Capacitores perto de ICS, cobertura 10 KHZ - 2 GHz.

-

Pilares micro-cobre: Pilares de 200μm de diâmetro sob BGAs, Indutância de loop de corte por 30%.

2.5 Campo minado 5: Transrupção do caminho de retorno - a bomba emi invisível

Risco EMI: Planos de referência quebrados geram ruído de modo comum, excedendo os limites da EMI por 10 dB.

Soluções:

-

Costura do solo: Coloque vias terrestres (≤0.1o) todo 100 Mil entre camadas de sinal.

-

Bridging de plano dividido: Use capacitores enterrados (por exemplo, AVX 0402B) Para o acoplamento 10NF entre as divisões de energia.

3. DDR5 Design Regras de ouro: Fórmulas e cadeias de ferramentas

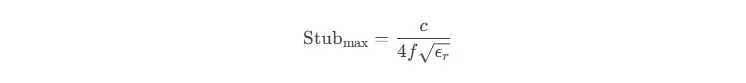

3.1 Via limitação de stub:Para DDR5-6400 (F = 3,2 GHz) no FR4: Stubmáx≤14,7 mm.

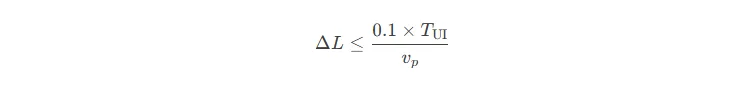

3.2 Tolerância de pares diferenciais:

Com TUi= 0,3125 ns e vp= 6 polegadas/: ΔL≤1,9 mil.

3.3 Alvo de impedância PDN:

Para ondulação de 50mv e corrente transitória de 10A: Zalvo≤5 MΩ.

4. Reengenharia de processo de design de PCB: De julgamento e erro a acionado por simulação

4.1 Planejamento de topologia:

-

Modelo VIAS em HFSS; Otimize as dimensões antipad.

-

Extrair impedância de empilhamento via Siwave; Construa bibliotecas de parâmetro S..

4.2 Execução de roteamento:

-

Ativar verificações de impedância em tempo real em Allegro; Violações de bandeira automática.

-

Implementar a topologia de mosca com ≤2 mil por meio intragrupo.

4.3 Validação:

-

Realizar testes de diagrama ocular (Anúncios Keysight) com altura dos olhos ≥70 mV.

-

Meça as curvas TDR; variação de impedância limite para ± 5%.

Conclusão: O “Três corpos” Lei do Design DDR5

Sob a velocidade GHZ, Mound Nuic, e restrições de tolerância a mícrons, DDR5 PCB Design entra em um “mecânica quântica” era. Vitória na guerra de integridade do sinal exige convergência de ciência do material (Substratos baixos DK), processos avançados (Map), e domínio da simulação.

LOGOTIPO UGPCB

LOGOTIPO UGPCB