аёҒаёІаёЈа№Ғаёҷаё°аёҷаёі: аёӘаёҮаё„аёЈаёІаёЎаёЈаё°аё”аёұаёҡаёЎаёҙаёҘаёҘаёҙа№ҖаёЎаё•аёЈа№ғаёҷаёҒаёІаёЈаёӯаёӯаёҒа№Ғаёҡаёҡ PCB DDR5

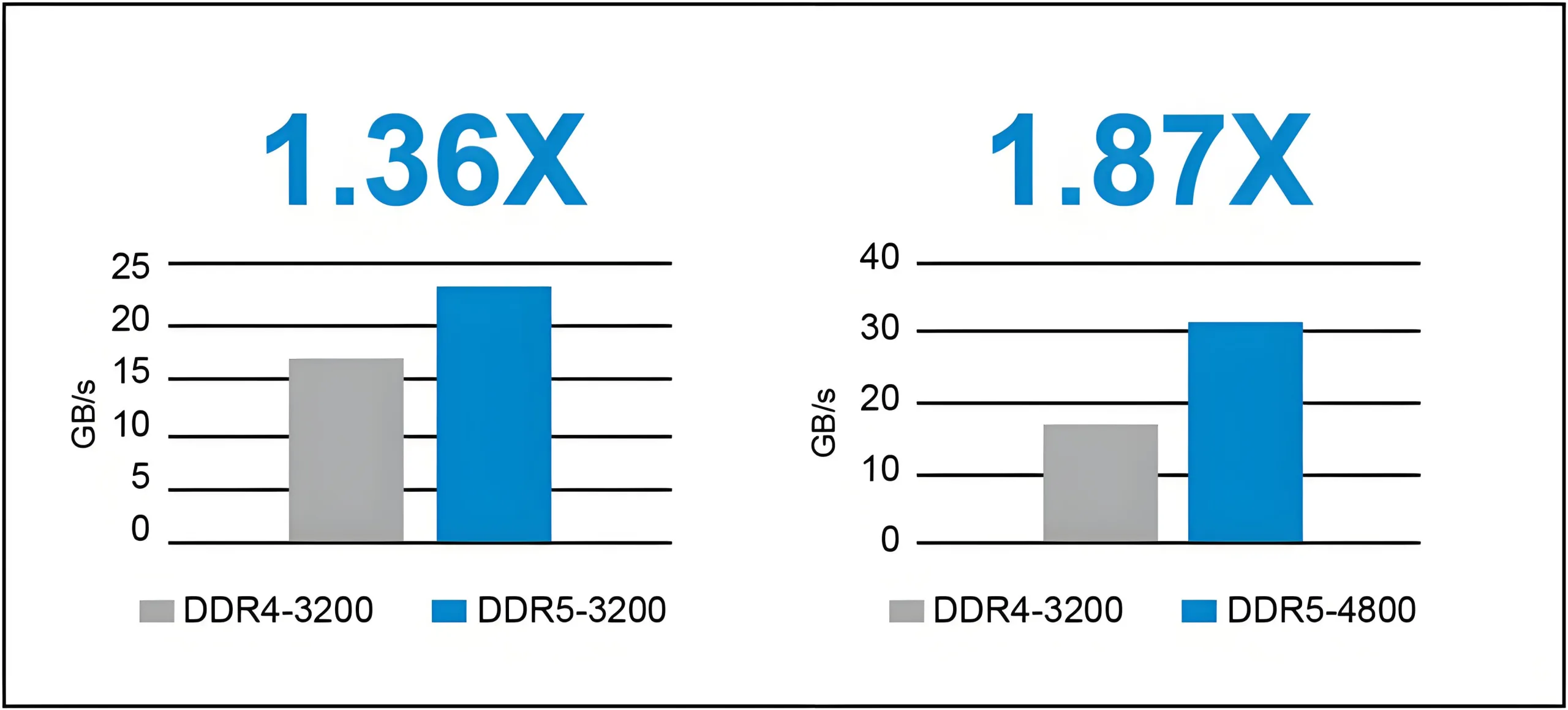

аёҒаёІаёЈаёҒа№үаёІаё§аёҒаёЈаё°а№Ӯаё”аё”аёҲаёІаёҒ DDR4 ไаёӣа№Җаёӣа№Үаёҷ DDR5 аё–аё·аёӯа№Җаёӣа№ҮаёҷаёҒаёІаёЈа№ҖаёӣаёҘаёөа№ҲаёўаёҷаёҒаёЈаё°аёҡаё§аёҷаё—аёұаёЁаёҷа№Ң: аёӯаёұаё•аёЈаёІаёӘаёұаёҚаёҚаёІаё“а№Җаёһаёҙа№ҲаёЎаёӮаё¶а№үаёҷаёҲаёІаёҒ 3,200 MT/s аё–аё¶аёҮ 6,400 MT/s а№ғаёҷаёӮаё“аё°аё—аёөа№Ҳа№ҒаёЈаёҮаё”аёұаёҷไаёҹаёҹа№үаёІа№ғаёҷаёҒаёІаёЈаё—аёіаёҮаёІаёҷаёҘаё”аёҘаёҮа№Җаё«аёҘаё·аёӯ 1.1V. аё„аё§аёІаёЎаё—а№үаёІаё—аёІаёўаё„аё№а№Ҳаёҷаёөа№үа№ҖаёӣаёҘаёөа№Ҳаёўаёҷа№ҒаёӣаёҘаёҮไаёӣ аёһаёөаёӢаёөаёҡаёө аёҒаёІаёЈаёҒаёіаё«аёҷаё”а№ҖаёӘа№үаёҷаё—аёІаёҮаёҲаёІаёҒаё§аёҙаёЁаё§аёҒаёЈаёЈаёЎаёҒаёІаёЈа№ҖаёҠаё·а№ҲаёӯаёЎаё•а№Ҳаёӯаё—аёөа№Ҳа№ҖаёЈаёөаёўаёҡаёҮа№ҲายไаёӣаёӘаё№а№ҲаёӘаёҮаё„аёЈаёІаёЎаё—аёөа№ҲаёЎаёөаё„аё§аёІаёЎа№ҒаёЎа№ҲаёҷаёўаёіаёЈаё°аё”аёұаёҡаёЎаёҙаёҘаёҘаёҙа№ҖаёЎаё•аёЈ. аёӮа№үаёӯаёЎаё№аёҘаёӯаёёаё•аёӘаёІаё«аёҒаёЈаёЈаёЎа№Җаёӣаёҙаё”а№Җаёңаёўаё§а№ҲаёІ 80% аё„аё§аёІаёЎаёҘа№үаёЎа№Җаё«аёҘаё§а№ғаёҷаёҒаёІаёЈаёӯаёӯаёҒа№Ғаёҡаёҡ DDR5 а№ҖаёҒаёҙаё”аёҲаёІаёҒаёӣаёұаёҚаё«аёІаёҒаёІаёЈаёҒаёіаё«аёҷаё”а№ҖаёӘа№үаёҷаё—аёІаёҮ, аёҒаёұаёҡ 90% аёӣа№үаёӯаёҮаёҒаёұаёҷไดа№үаё”а№үаё§аёўаёҒаёІаёЈаёҲаёіаёҘаёӯаёҮа№Җаё„а№үаёІа№Ӯаё„аёЈаёҮаёҘа№Ҳаё§аёҮаё«аёҷа№үаёІ. аёҡаё—аё„аё§аёІаёЎаёҷаёөа№үаёҲаё°аё§аёҙа№Җаё„аёЈаёІаё°аё«а№ҢаёӮа№үаёӯаёңаёҙаё”аёһаёҘаёІаё”аёҒаёІаёЈаёҒаёіаё«аёҷаё”а№ҖаёӘа№үаёҷаё—аёІаёҮ DDR5 аё—аёөа№ҲаёӘаёіаё„аёұаёҚаё«а№үаёІаёӣаёЈаё°аёҒаёІаёЈ, аёӘаёҷаёұаёҡаёӘаёҷаёёаёҷа№Ӯаё”аёўаёӮа№үаёӯаёЎаё№аёҘа№ҖаёҠаёҙаёҮаёӣаёЈаё°аёҲаёұаёҒаё©а№Ңа№ҒаёҘаё°аёҒаёЈаё“аёөаёЁаё¶аёҒаё©аёІ, аёҷаёіа№ҖаёӘаёҷаёӯа№ӮаёӢаёҘаё№аёҠаёұа№Ҳаёҷаё—аёөа№ҲаёӘаёІаёЎаёІаёЈаё–аёҷำไаёӣаёӣаёҸаёҙаёҡаёұаё•аёҙไดа№үаёӘаёіаё«аёЈаёұаёҡаёЎаё·аёӯаёӯаёІаёҠаёөаёһаё”а№үаёІаёҷ PCB.

1. аёҘаёұаёҒаё©аё“аё°аё—аёІаёҮаёҒаёІаёўаё аёІаёһ DDR5: а№Җаё«аё•аёёа№ғаё”аё§аёҙаёҳаёөаёҒаёІаёЈаёӯаёӯаёҒа№Ғаёҡаёҡ PCB а№Ғаёҡаёҡаё”аёұа№үаёҮа№Җаё”аёҙаёЎаёҲаё¶аёҮаёҘа№үаёЎа№Җаё«аёҘаё§

1.1 аёӯаёұаё•аёЈаёІаёӘаёұаёҚаёҚаёІаё“а№ҒаёҘаё°аёҒаёІаёЈаёӣаёҸаёҙаё§аёұаё•аёҙа№Ғаёҡаёҷаё”а№Ңаё§аёҙаёҳ

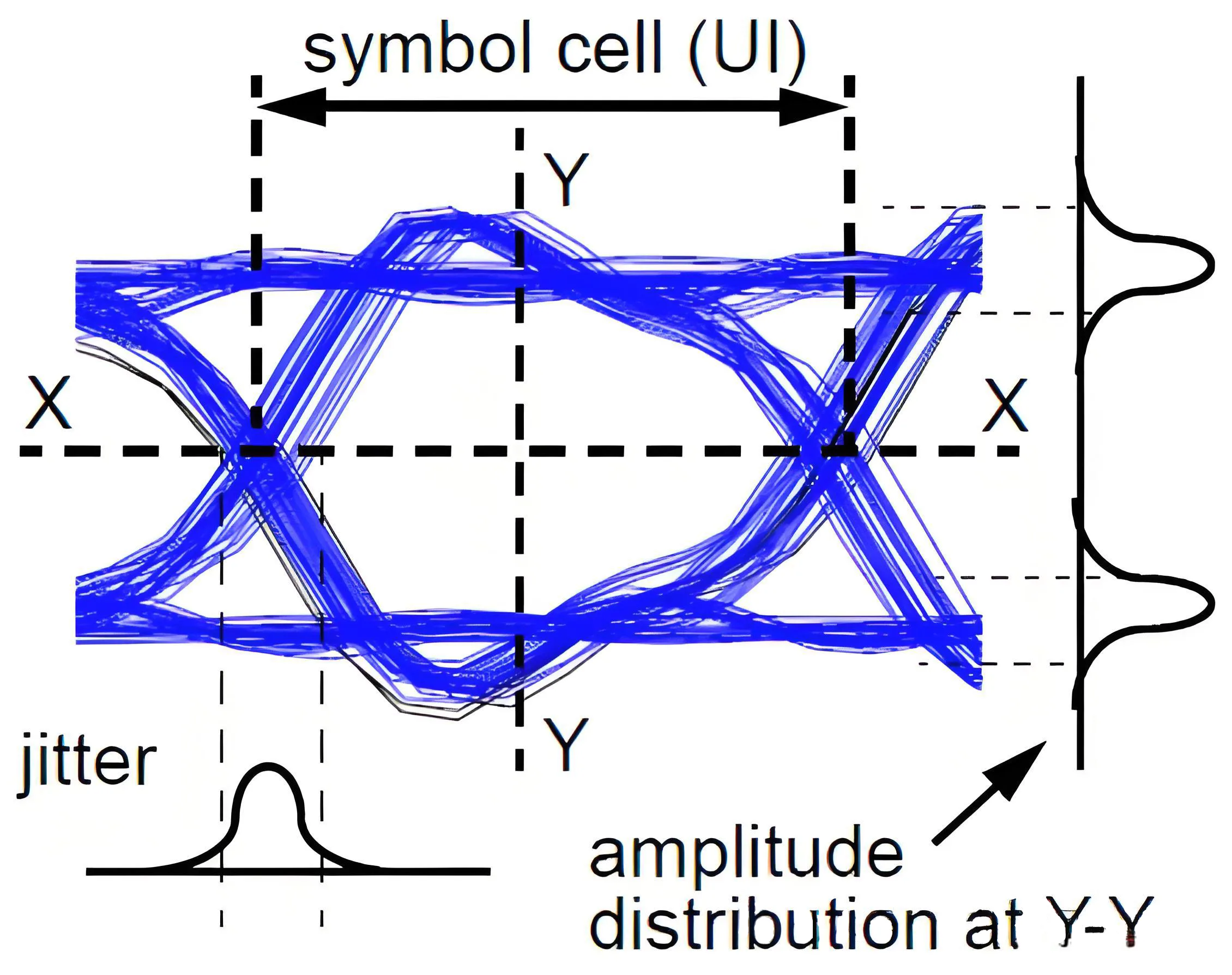

аёӘаёіаё«аёЈаёұаёҡ DDR5-6400, аё„аё§аёІаёЎаё–аёөа№ҲаёӘаёұаёҚаёҚаёІаё“аёҷаёІаё¬аёҙаёҒаёІаё—аёөа№ҲаёЎаёөаёӣаёЈаё°аёӘаёҙаё—аёҳаёҙаё аёІаёһаё–аё¶аёҮ 3,200 а№ҖаёЎаёҒаё°а№Җаё®аёҙаёЈаё•аёӢа№Ң, аё”а№үаё§аёўаёӯаёұаё•аёЈаёІаёӮаёӯаёҡаё—аёөа№ҲаёЈаё§аё”а№ҖаёЈа№Үаё§аё—аёөа№ҲаёӘаёёаё” 0.5 аёӣаёҘ (20-80% а№Җаё§аёҘаёІа№Җаёһаёҙа№ҲаёЎаёӮаё¶а№үаёҷ). аёӘаёҙа№ҲаёҮаёҷаёөа№үаё—аёіа№ғаё«а№үа№ҖаёҒаёҙаё”:

-

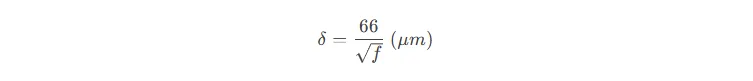

аёңаёҘаёҒаёЈаё°аё—аёҡаё•а№Ҳаёӯаёңаёҙаё§аё«аёҷаёұаёҮаё—аёөа№ҲаёЈаёёаёҷа№ҒаёЈаёҮаёӮаё¶а№үаёҷ: аёҒаёЈаё°а№ҒаёӘаё„аё§аёІаёЎаё–аёөа№ҲаёӘаё№аёҮаёЎаёёа№ҲаёҮаё„аё§аёІаёЎаёӘаёҷа№ғаёҲไаёӣаё—аёөа№Ҳаёһаё·а№үаёҷаёңаёҙаё§аё•аёұаё§аёҷаёі, аёҘаё”аё„аё§аёІаёЎаё«аёҷаёІаёӮаёӯаёҮаё—аёӯаёҮа№Ғаё”аёҮаё—аёөа№ҲаёЎаёөаёӣаёЈаё°аёӘаёҙаё—аёҳаёҙаё аёІаёһаёҘаёҮ 0.66 ไมа№Ӯаё„аёЈа№ҖаёЎаё•аёЈаё—аёөа№Ҳ 10 аёҒаёҙаёҒаё°а№Җаё®аёҙаёЈаё•аёӢа№Ң.

-

аёҒаёІаёЈа№Җаёһаёҙа№ҲаёЎаёҒаёІаёЈаёӘаё№аёҚа№ҖаёӘаёөаёўаёӯаёҙа№ҖаёҘа№ҮаёҒаё—аёЈаёҙаёҒ: аёһаё·а№үаёҷаёңаёҙаё§ FR4 а№ҒаёӘаё”аёҮаёҒаёІаёЈаёӘаё№аёҚа№ҖаёӘаёөаёўа№Ғаё—аёҷа№ҖаёҲаёҷаё•а№Ң (аёҹ) аёӮаёӯаёҮ 0.02 аё—аёөа№Ҳ 10 аёҒаёҙаёҒаё°а№Җаё®аёҙаёЈаё•аёӢа№Ң, аёҒа№Ҳаёӯа№ғаё«а№үа№ҖаёҒаёҙаё” >3 аёҒаёІаёЈаёҘаё”аё—аёӯаёҷаёӘаёұаёҚаёҚаёІаё“ dB/аёҷаёҙа№үаё§.

аёҒаёІаёЈаё•аёЈаё§аёҲаёӘаёӯаёҡаёӘаё№аё•аёЈ (аё„аё§аёІаёЎаёҘаё¶аёҒаёӮаёӯаёҮаёңаёҙаё§аё«аёҷаёұаёҮ):

аё—аёөа№Ҳ аёү=10аёҒаёҙаёҒаё°а№Җаё®аёҙаёЈаё•аёӢа№Ң, ОҙОі0.66 ไมа№Ӯаё„аёЈа№ҖаёЎаё•аёЈ,а№Җаё«аёҘаё·аёӯаё—аёӯаёҮа№Ғаё”аёҮ 1 аёӯаёӯаёҷаёӢа№Ңа№Ғаёҡаёҡаё”аёұа№үаёҮа№Җаё”аёҙаёЎ (35 Ојm) аёҒаёұаёҡ <2% аёҒаёІаёЈа№ғаёҠа№үаёӣаёЈаё°а№ӮаёўаёҠаёҷа№Ң.

2. а№ҖаёӮаё•аё—аёёа№ҲаёҷаёЈаё°а№Җаёҡаёҙаё”аёҒаёІаёЈаёҒаёіаё«аёҷаё”а№ҖаёӘа№үаёҷаё—аёІаёҮ DDR5 аё«а№үаёІа№Ғаё«а№ҲаёҮа№ҒаёҘаё°аёЎаёІаё•аёЈаёҒаёІаёЈаё•аёӯаёҡа№Ӯаё•а№ү

2.1 а№ҖаёӮаё•аё—аёөа№Ҳаё§аёІаёҮаё—аёёа№ҲаёҷаёЈаё°а№Җаёҡаёҙаё” 1: аёӮа№үаёӯаёңаёҙаё”аёһаёҘаёІаё”аё”а№үаёІаёҷа№Җаё§аёҘаёІ вҖ“ Вұ15ps а№ҖаёҒаё“аё‘а№ҢаёҒаёІаёЈа№ҖаёӯаёІаёҠаёөаё§аёҙаё•аёЈаёӯаё”

аёңаёҘаёҒаёЈаё°аё—аёҡ: ความยาวไมа№Ҳаё•аёЈаёҮаёҒаёұаёҷ 5 аёЎаёҙаёҘаё—аёіа№ғаё«а№үа№ҖаёҒаёҙаё”аё„аё§аёІаёЎаёҘа№ҲаёІаёҠа№үаёІ Вұ12ps, аёўаёёаёҡаё„аё§аёІаёЎаёҒаё§а№үаёІаёҮаёӮаёӯаёҮаё•аёІа№Ғаёҷаё§аёҷаёӯаёҷаёҘаёҮаё”а№үаё§аёў 30%.

аёҒаёЈаё“аёөаёЁаё¶аёҒаё©аёІ: аёҒаёІаёЈаёӯаёӯаёҒа№Ғаёҡаёҡ GPU ไดа№үаёЈаёұаёҡаёңаёҘаёҒаёЈаё°аё—аёҡаёҲаёІаёҒаёҒаёІаёЈа№ҖаёӘаё·а№ҲаёӯаёЎаёӘаё аёІаёһаёӮаёӯаёҮ BER 10вҲ’12 аё–аё¶аёҮ 10вҲ’7 а№Җаёҷаё·а№ҲаёӯаёҮаёҲаёІаёҒаёҒаёІаёЈа№ҖаёӯаёөаёўаёҮ DQ/DQS 8 аёҘа№үаёІаёҷ.

аёҒаёІаёЈа№ҒаёҒа№үаёӣаёұаёҚаё«аёІ:

-

3D аёҒаёІаёЈаёҠаё”а№ҖаёҠаёўа№ҖаёӘа№үаёҷаё—аёІаёҮ: а№Ғаё—аёҷаё—аёөа№Ҳаё„аё”а№Җаё„аёөа№үаёўаё§ 90В° аё”а№үаё§аёўаё„аё”а№Җаё„аёөа№үаёўаё§ 45В°, аёҘаё”аё„аё§аёІаёЎаёҲаёёаёӮаёӯаёҮаёӣаёЈаёӘаёҙаё•аё”а№үаё§аёў 30%.

-

аёҒаёІаёЈаёӘаёӯаёҡа№Җаё—аёөаёўаёҡไทมа№ҢаёЎаёҙа№ҲаёҮа№ҒаёҡаёҡไดаёҷаёІаёЎаёҙаёҒ: аё—аёіаёҒаёІаёЈаёҲаёіаёҘаёӯаёҮаёЎаёӯаёҷаё•аёҙаё„аёІаёЈа№Ңа№ӮаёҘ (аёҲаёұаёҮаё«аё§аё° Sigrity) аё„аёЈаёӯаёҡаё„аёҘаёёаёЎаё„аё§аёІаёЎа№ҒаёӣаёЈаёңаёұаёҷаёӮаёӯаёҮаёҒаёЈаё°аёҡаё§аёҷаёҒаёІаёЈ Вұ10%.

аёӘаё№аё•аёЈ (аёЈаё°аёўаё°аёӮаёӯаёҡа№Җаё§аёҘаёІ):

TаёЈаё°аёўаё°аёӮаёӯаёҡ=аё•аё§аёҮаёҲаёЈвҲ’(TаёЈа№Ҳаё§аёЎ+Tа№Җаё—аёөа№Ҳаёўаё§аёҡаёҙаёҷ+TаёҒаёЈаё°аё§аёҷаёҒаёЈаё°аё§аёІаёўа№ғаёҲ)

аёӘаёіаё«аёЈаёұаёҡ DDR5-6400 (Tаё§аёҮаёҲаёЈ=0.3125 ), аёҒаёІаёЈа№ҒаёҲа№үаёҮа№Җаё•аё·аёӯаёҷаёӮаёӯаёҮаёЈаё°аёҡаёҡаё—аёЈаёҙаёҒа№ҖаёҒаёӯаёЈа№Ңа№ҖаёЎаё·а№Ҳаёӯ TаёЈаё°аёўаё°аёӮаёӯаёҡ<50 аёӣаёҘ.

2.2 а№ҖаёӮаё•аё—аёөа№Ҳаё§аёІаёҮаё—аёёа№ҲаёҷаёЈаё°а№Җаёҡаёҙаё” 2: ความไมа№Ҳаё•а№Ҳаёӯа№Җаёҷаё·а№ҲаёӯаёҮаёӮаёӯаёҮаё„аё§аёІаёЎаё•а№үаёІаёҷаё—аёІаёҷ - аё„аёҘаё·а№ҲаёҷаёӘаё¶аёҷаёІаёЎаёҙаёӘаёұаёҚаёҚаёІаё“5О©

а№ҖаёӘаёөа№ҲаёўаёҮ: аёӘаёІа№Җหตุไมа№Ҳаё•аёЈаёҮаёҒаёұаёҷаёӮаёӯаёҮаёӯаёҙаёЎаёһаёөа№Ғаё”аёҷаёӢа№Ң >15 аёҒаёІаёЈаёӘаё№аёҚа№ҖаёӘаёөаёўаёңаёҘаё•аёӯаёҡа№Ғаё—аёҷ dB, аёўаёёаёҡаё„аё§аёІаёЎаёӘаё№аёҮаёӮаёӯаёҮаё”аё§аёҮаё•аёІа№Ғаёҷаё§аё•аёұа№үаёҮаёҘаёҮаё”а№үаё§аёў 40%.

аёӮа№үаёӯаёЎаё№аёҘ: а№Ғаё•а№ҲаёҘаё°аёӯаёұаёҷไมа№Ҳไดа№үаёЈаёұаёҡаёҒаёІаёЈа№Җаёһаёҙа№ҲаёЎаёӣаёЈаё°аёӘаёҙаё—аёҳаёҙаё аёІаёһаёңа№ҲаёІаёҷаёҒаёІаёЈа№Җаёһаёҙа№ҲаёЎ 0.2 аёҒаёІаёЈаёӘаё№аёҚа№ҖаёӘаёөаёўаёҒаёІаёЈа№Ғаё—аёЈаёҒ dB аё—аёөа№Ҳ 5 GHz.

аёҒаёІаёЈа№ҒаёҒа№үаёӣаёұаёҚаё«аёІ:

-

аёңа№ҲаёІаёҷаёҒаёІаёЈаёӣаёҸаёҙаё§аёұаё•аёҙ: а№ғаёҠа№үаёҲаёёаё”аёӯа№Ҳаёӯаёҷа№Ғаёҡаёҡа№ҖаёҘа№ҖаёӢаёӯаёЈа№Ңаёҡаёӯаё” (вүӨ4аёҘа№үаёІаёҷ) аёһаёЈа№үаёӯаёЎаёҒаёІаёЈаёҠаё”а№ҖаёҠаёўа№Ғаёӯаёҷаё•аёҙа№Ғаёһаё”, аёҲаёіаёҒаёұаё”аё„аё§аёІаёЎа№ҒаёӣаёЈаёңаёұаёҷаёӮаёӯаёҮаёӯаёҙаёЎаёһаёөа№Ғаё”аёҷаёӢа№Ңไวа№үаё—аёөа№Ҳ Вұ3О©.

-

аёҒаёІаёЈа№Җаёһаёҙа№ҲаёЎаёӣаёЈаё°аёӘаёҙаё—аёҳаёҙаё аёІаёһа№Ғаёһаё”: а№ғаёҠа№үа№Ғаёңа№ҲаёҷаёӯаёҙаёҘаёҙаёӣаё•аёҙаё„аёӯаёҘ (1.5:1 аёӯаёұаё•аёЈаёІаёӘа№Ҳаё§аёҷаё аёІаёһ) а№Җаёһаё·а№ҲаёӯаёҘаё”аёңаёҘаёҒаёЈаё°аё—аёҡаёӮаёӯаёҮаё•аёұаё§а№ҖаёҒа№ҮаёҡаёӣаёЈаё°аёҲаёёаё”а№үаё§аёў 20%.

аёӘаё№аё•аёЈ (аёңа№ҲаёІаёҷа№ӮаёЎа№Җаё”аёҘаёӯаёҙаёЎаёһаёөа№Ғаё”аёҷаёӢа№Ң):

аёӢа№Җаё§аёөаёўаё«аёўаёІаёҡаё„аёІаёў87ПөrвӢ…lnвҒЎ(5.98аёҠаёЎ/(0.8d1+d2))

аё—аёөа№Ҳไหаёҷ : аё„аё§аёІаёЎаё«аёҷаёІаёӯаёҙа№ҖаёҘа№ҮаёҒаё—аёЈаёҙаёҒ, аёҮ1: аёңа№ҲаёІаёҷа№ҖаёӘа№үаёҷаёңа№ҲаёІаёҷаёЁаё№аёҷаёўа№ҢаёҒаёҘаёІаёҮ, : а№ҖаёӘа№үаёҷаёңа№ҲаёІаёҷаёЁаё№аёҷаёўа№ҢаёҒаёҘаёІаёҮа№Ғаёңа№Ҳаёҷ.

2.3 а№ҖаёӮаё•аё—аёөа№Ҳаё§аёІаёҮаё—аёёа№ҲаёҷаёЈаё°а№Җаёҡаёҙаё” 3: Cross-Layer Delay вҖ“ а№Җаёӯаёҹа№ҖаёҹаёҒаё•а№Ңаёңаёөа№ҖаёӘаё·а№үаёӯ 0.1ps/mm

аёңаёҘаёҒаёІаёЈаёӘаёІаёҷไаёҹа№ҖаёҡаёӯаёЈа№Ң: аёҒаёІаёЈа№ҒаёӣаёЈаёңаёұаёҷаё„аёҮаё—аёөа№ҲаёӮаёӯаёҮаёӯаёҙа№ҖаёҘа№ҮаёҒаё—аёЈаёҙаёҒ (О”Пөr=0.3) аёҲаёІаёҒаёӘаёІа№Җаё«аё•аёёаё„аё§аёІаёЎа№Җаёӣа№ҮаёҷаёЈаё°аёўаё°аёӮаёӯаёҮа№ғаёўа№ҒаёҒа№үаё§ 0.6 PS/аёҷаёҙа№үаё§ аёҒаёІаёЈаё«аёҷа№Ҳаё§аёҮа№Җаё§аёҘаёІа№ҖаёӯаёөаёўаёҮ.

аёҒаёІаёЈа№ҒаёҒа№үаёӣаёұаёҚаё«аёІ:

-

аёҒаёІаёЈаёҲаёұаё”а№Ғаёҷаё§а№ҒаёҒаёҷ Z: аёҒаёіаё«аёҷаё”а№ҖаёӘа№үаёҷаё—аёІаёҮаёӘаёұаёҚаёҚаёІаё“аёҒаёҘаёёа№Ҳมไаёҡаё•а№Ңаё—аёөа№ҲаёЎаёёаёЎ Вұ45В° а№Җаёһаё·а№ҲаёӯаёўаёҒа№ҖаёҘаёҙаёҒไดаёӯаёҙа№ҖаёҘа№ҮаёҒаё•аёЈаёҙаёҒа№Ғаёӯаёҷไаёӯа№ӮаёӢа№Ӯаё—аёЈаёӣаёө.

-

аёҒаёІаёЈаёҠаё”а№ҖаёҠаёўаёӮа№үаёІаёЎа№ҖаёҘа№ҖаёўаёӯаёЈа№Ң: а№Ӯаё«аёҘаё”аёӮа№үаёӯаёЎаё№аёҘ Dk/Df аёӮаёӯаёҮаё§аёұаёӘаё”аёёаёһаёҙаёЎаёһа№ҢаёҘа№Ҳаё§аёҮаё«аёҷа№үаёІаёҘаёҮа№ғаёҷа№Җаё„аёЈаё·а№ҲаёӯаёҮаёЎаё·аёӯ EDA а№Җаёһаё·а№Ҳаёӯа№ҒаёҒа№үไаёӮаёҒаёІаёЈаё«аёҷа№Ҳаё§аёҮа№Җаё§аёҘаёІаёӯаёұаё•а№ӮаёҷаёЎаёұаё•аёҙ.

2.4 а№ҖаёӮаё•аё—аёөа№Ҳаё§аёІаёҮаё—аёёа№ҲаёҷаёЈаё°а№Җаёҡаёҙаё” 4: Power Ripple вҖ“ аёӣаёҸаёҙаёҒаёҙаёЈаёҙаёўаёІаёҘаё№аёҒа№ӮаёӢа№Ҳаёҷаёҙаё§а№Җаё„аёҘаёөаёўаёЈа№Ң 1mV

ความไว: 50mV аёЈаё°аёҘаёӯаёҒаё—аёөа№Ҳа№Ғаё«аёҘа№ҲаёҮаёҲа№ҲаёІаёў 1.1V а№Җаёһаёҙа№ҲаёЎаё„аё§аёІаёЎаёҒаёЈаё°аё§аёҷаёҒаёЈаё°аё§аёІаёўа№ғаёҲаёӮаёӯаёҮไดรа№Җаё§аёӯаёЈа№Ң 20%.

аёҒаёІаёЈаёҲаёіаёҘаёӯаёҮ: аё„аё§аёІаёЎаё•а№үаёІаёҷаё—аёІаёҷа№Җаёӣа№үаёІаё«аёЎаёІаёў PDN аёҲаё°аё•а№үаёӯаёҮа№Җаёӣа№Үаёҷ вүӨ2 mО©@100 MHz вҖ“ а№ҖаёӮа№үаёЎаёҮаё§аё”аёҒаё§а№ҲаёІаёҒаёІаёЈаёӯаёӯаёҒа№Ғаёҡаёҡа№Ғаёҡаёҡаё”аёұа№үаёҮа№Җаё”аёҙаёЎаё–аё¶аёҮ 5 а№Җаё—а№ҲаёІ.

аёҒаёІаёЈа№ҒаёҒа№үаёӣаёұаёҚаё«аёІ:

-

3D а№ҖаёЎаё—аёЈаёҙаёҒаёӢа№Ңаё•аёұаё§а№ҖаёҒа№ҮаёҡаёӣаёЈаё°аёҲаёё: аёӣаёЈаёұаёҡа№ғаёҠа№ү 0.1ОјF (0402) + 10а№Җаёӯа№Үаёҷа№Җаёӯаёҹ (0201) аё•аёұаё§а№ҖаёҒа№ҮаёҡаёӣаёЈаё°аёҲаёёа№ғаёҒаёҘа№үไаёӯаёӢаёө, аё„аёЈаёӯаёҡаё„аёҘаёёаёЎ 10 аёҒаёҙа№ӮаёҘа№Җаё®аёҙаёЈаё•аёӢа№ҢвҖ“2 аёҒаёҙаёҒаё°а№Җаё®аёҙаёЈаё•аёӢа№Ң.

-

а№ҖаёӘาไมа№Ӯаё„аёЈаё—аёӯаёҮа№Ғаё”аёҮ: аёқаёұаёҮа№ҖаёӘаёІаёӮаёҷаёІаё”а№ҖаёӘа№үаёҷаёңа№ҲаёІаёҷаёЁаё№аёҷаёўа№ҢаёҒаёҘаёІаёҮ 200Ојm ไวа№үа№ғаё•а№ү BGA, аё•аёұаё”аё„аё§аёІаёЎа№Җаё«аёҷаёөа№Ҳаёўаё§аёҷаёіаё§аёҮа№Ӯаё”аёў 30%.

2.5 а№ҖаёӮаё•аё—аёөа№Ҳаё§аёІаёҮаё—аёёа№ҲаёҷаёЈаё°а№Җаёҡаёҙаё” 5: аёҒаёІаёЈаё«аёўаёёаё”аёҠаё°аёҮаёұаёҒаёӮаёӯаёҮа№ҖаёӘа№үаёҷаё—аёІаёҮаёҒаёҘаёұаёҡ вҖ“ аёЈаё°а№Җаёҡаёҙаё” EMI аё—аёөа№ҲаёЎаёӯаёҮไมа№Ҳа№Җаё«а№Үаёҷ

аё„аё§аёІаёЎа№ҖаёӘаёөа№ҲаёўаёҮаёҲаёІаёҒаёӯаёөа№Җаёӯа№Үมไаёӯ: аёЈаё°аёҷаёІаёҡаёӯа№үаёІаёҮаёӯаёҙаёҮаё—аёөа№Ҳа№ҖаёӘаёөаёўаё«аёІаёўаёҲаё°аёӘаёЈа№үаёІаёҮаёӘаёұаёҚаёҚаёІаё“аёЈаёҡаёҒаё§аёҷа№ғаёҷа№Ӯаё«аёЎаё”аё—аёұа№Ҳวไаёӣ, а№ҖаёҒаёҙаёҷаёӮаёөаё”аёҲаёіаёҒаёұаё” EMI а№Ӯаё”аёў 10 DB.

аёҒаёІаёЈа№ҒаёҒа№үаёӣаёұаёҚаё«аёІ:

-

аёҒаёІаёЈа№Җаёўа№Үаёҡаёһаё·а№үаёҷ: аё§аёІаёҮаёҲаёёаё”а№Ғаё§аё°аё аёІаё„аёһаё·а№үаёҷаё”аёҙаёҷ (вүӨ0.1О©) аё—аёұа№үаёҮаё«аёЎаё” 100 аёҘа№үаёІаёҷаёЈаё°аё«аё§а№ҲаёІаёҮаёҠаёұа№үаёҷаёӘаёұаёҚаёҚаёІаё“.

-

аёҒаёІаёЈа№ҖаёҠаё·а№ҲаёӯаёЎаё•а№Ҳаёӯа№Ғаёҡаёҡа№ҒаёўаёҒаёӘа№Ҳаё§аёҷ: а№ғаёҠа№үаё•аёұаё§а№ҖаёҒа№ҮаёҡаёӣаёЈаё°аёҲаёёа№ҒаёҡаёҡаёқаёұаёҮ (а№ҖаёҠа№Ҳаёҷ, а№Җаёӯаё§аёөа№Җаёӯа№ҮаёҒаёӢа№Ң 0402B) аёӘаёіаё«аёЈаёұаёҡаёҒаёІаёЈа№ҖаёҠаё·а№ҲаёӯаёЎаё•а№Ҳаёӯ 10nF аёӮа№үаёІаёЎаёҒаёІаёЈа№ҒаёўаёҒаёҒаёіаёҘаёұаёҮ.

3. аёҒаёҺаё—аёӯаёҮаёӮаёӯаёҮаёҒаёІаёЈаёӯаёӯаёҒа№Ғаёҡаёҡ DDR5: аёӘаё№аё•аёЈа№ҒаёҘаё° Toolchains

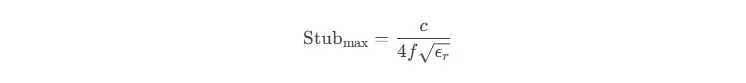

3.1 аёңа№ҲаёІаёҷаёӮа№үаёӯаёҲаёіаёҒаёұаё” Stub:аёӘаёіаё«аёЈаёұаёҡ DDR5-6400 (аёү=3.2аёҒаёҙаёҒаё°а№Җаё®аёҙаёЈаё•аёӢа№Ң) аёҡаёҷ FR4: аё•а№үаёҷаёӮаёұа№үаё§аёӘаё№аёҮаёӘаёёаё”вүӨ14.7 аёЎаёЎ.

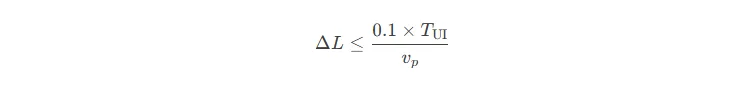

3.2 аё„аё§аёІаёЎаёӯаё”аё—аёҷаё•а№Ҳаёӯаё„аё№а№Ҳаё—аёөа№Ҳа№Ғаё•аёҒаё•а№ҲаёІаёҮаёҒаёұаёҷ:

аёҒаёұаёҡ TUI=0.3125 аёҷаёӘ а№ҒаёҘаё° Vаёһаёө=6 аёҷаёҙа№үаё§/: О”LвүӨ1.9аёҘа№үаёІаёҷ.

3.3 а№Җаёӣа№үаёІаё«аёЎаёІаёўаё„аё§аёІаёЎаё•а№үаёІаёҷаё—аёІаёҷ PDN:

аёӘаёіаё«аёЈаёұаёҡаёҒаёЈаё°а№ҒаёӘаёҒаёЈаё°а№Җаёһаё·а№ҲаёӯаёЎ 50mV а№ҒаёҘаё°аёҒаёЈаё°а№ҒаёӘаёҠаёұа№Ҳаё§аё„аёЈаёІаё§ 10A: аёӢаёөа№Җаёӣа№үаёІвүӨ5 mО©.

4. аёҒаёІаёЈаёЈаё·а№үаёӯаёӣаёЈаёұаёҡаёҒаёЈаё°аёҡаё§аёҷаёҒаёІаёЈаёӯаёӯаёҒа№Ғаёҡаёҡ PCB: аёҲаёІаёҒаёҒаёІаёЈаёҘаёӯаёҮаёңаёҙаё”аёҘаёӯаёҮаё–аё№аёҒไаёӣаёҲаёҷаё–аё¶аёҮаёҒаёІаёЈаёӮаёұаёҡа№Җаё„аёҘаё·а№Ҳаёӯаёҷаё”а№үаё§аёўаёҒаёІаёЈаёҲаёіаёҘаёӯаёҮ

4.1 аёҒаёІаёЈаё§аёІаёҮа№Ғаёңаёҷа№Ӯаё—а№Ӯаёһа№ӮаёҘаёўаёө:

-

аёҲаёёаё”а№Ғаё§аё°а№ӮаёЎа№Җаё”аёҘа№ғаёҷ HFSS; аёӣаёЈаёұаёҡаёӮаёҷаёІаё”а№Ғаёӯаёҷаё•аёҙа№Ғаёһаё”а№ғаё«а№үа№Җаё«аёЎаёІаё°аёӘаёЎ.

-

а№ҒаёўаёҒаё„аё§аёІаёЎаё•а№үаёІаёҷаё—аёІаёҷаёӘа№Ғаё•а№Үаё„аёӯаёұаёһаёңа№ҲаёІаёҷ SIwave; аёӘаёЈа№үаёІаёҮไаёҘаёҡаёЈаёІаёЈаёөаёһаёІаёЈаёІаёЎаёҙа№Җаё•аёӯаёЈа№Ң S.

4.2 аёҒаёІаёЈаё”аёіа№ҖаёҷаёҙаёҷаёҒаёІаёЈаёҒаёіаё«аёҷаё”а№ҖаёӘа№үаёҷаё—аёІаёҮ:

-

а№Җаёӣаёҙаё”а№ғаёҠа№үаёҮаёІаёҷаёҒаёІаёЈаё•аёЈаё§аёҲаёӘаёӯаёҡаё„аё§аёІаёЎаё•а№үаёІаёҷаё—аёІаёҷа№Ғаёҡаёҡа№ҖаёЈаёөаёўаёҘไทมа№Ңа№ғаёҷ Allegro; аёҒаёІаёЈаёҘаё°а№ҖаёЎаёҙаё”аёҒаёІаёЈаё•аёұа№үаёҮаё„а№ҲаёІаёӘаё–аёІаёҷаё°аёӯаёұаё•а№ӮаёҷаёЎаёұаё•аёҙ.

-

а№ғаёҠа№үа№Ӯаё—а№Ӯаёһа№ӮаёҘаёўаёөа№Ғаёҡаёҡ fly-by а№Ӯаё”аёўаёЎаёөаё„аё§аёІаёЎа№ҖаёӯаёөаёўаёҮаё аёІаёўа№ғаёҷаёҒаёҘаёёа№ҲаёЎ вүӨ2 аёҘа№үаёІаёҷ.

4.3 аёҒаёІаёЈаё•аёЈаё§аёҲаёӘаёӯаёҡ:

-

аё—аёіаёҒаёІаёЈаё—аё”аёӘаёӯаёҡа№Ғаёңаёҷаё аёІаёһаё•аёІ (а№ӮаёҶаё©аё“аёІаё„аёөаёўа№ҢไаёӢаё—а№Ң) аё”а№үаё§аёўаё„аё§аёІаёЎаёӘаё№аёҮаёӮаёӯаёҮаё•аёІ вүҘ70 mV.

-

аё§аёұаё”а№ҖаёӘа№үаёҷа№Ӯаё„а№үаёҮ TDR; аёҲаёіаёҒаёұаё”аёҒаёІаёЈа№ҖаёӣаёҘаёөа№Ҳаёўаёҷа№ҒаёӣаёҘаёҮаё„аё§аёІаёЎаё•а№үаёІаёҷаё—аёІаёҷไวа№үаё—аёөа№Ҳ Вұ 5%.

аёҡаё—аёӘаёЈаёёаёӣ: аё—аёөа№Ҳ “аёӘаёІаёЎаё•аёұаё§” аёҒаёҺаё«аёЎаёІаёўаёҒаёІаёЈаёӯаёӯаёҒа№Ғаёҡаёҡ DDR5

аё аёІаёўа№ғаё•а№үаё„аё§аёІаёЎа№ҖаёЈа№Үаё§ GHz, аёЎаёҙаёҘаёҘаёҙа№Ӯаё§аёҘаё•а№Ң-а№ҖаёӘаёөаёўаёҮ, а№ҒаёҘаё°аёӮа№үаёӯаёҲаёіаёҒаёұаё”аё”а№үаёІаёҷаё„аё§аёІаёЎаё—аёҷаё—аёІаёҷаё•а№Ҳаёӯไมครаёӯаёҷ, аёҒаёІаёЈаёӯаёӯаёҒа№Ғаёҡаёҡ PCB DDR5 а№ҖаёӮа№үаёІаёӘаё№а№Ҳ “аёҒаёҘаёЁаёІаёӘаё•аёЈа№Ңаё„аё§аёӯаёҷаё•аёұаёЎ” аёўаёёаё„. аёҠаёұаёўаёҠаёҷаё°а№ғаёҷаёӘаёҮаё„аёЈаёІаёЎаё„аё§аёІаёЎаёӘаёЎаёҡаё№аёЈаё“а№ҢаёӮаёӯаёҮаёӘаёұаёҚаёҚаёІаё“аёҲаёіа№Җаёӣа№Үаёҷаё•а№үаёӯаёҮаёӯаёІаёЁаёұаёўаёҒаёІаёЈаёҡаёЈаёЈаёҲаёҡаёҒаёұаёҷаёӮаёӯаёҮаё§аёұаёӘаё”аёёаёЁаёІаёӘаё•аёЈа№Ң (аё§аёұаёӘаё”аёёаёһаёҙаёЎаёһа№Ңаё—аёөа№ҲаёЎаёө Dk аё•а№Ҳаёі), аёҒаёЈаё°аёҡаё§аёҷаёҒаёІаёЈаёӮаёұа№үаёҷаёӘаё№аёҮ (mSAP), а№ҒаёҘаё°аё„аё§аёІаёЎа№ҖаёҠаёөа№Ҳаёўаё§аёҠаёІаёҚаё”а№үаёІаёҷаёҒаёІаёЈаёҲаёіаёҘаёӯаёҮ.

а№ӮаёҘа№ӮаёҒа№ү UGPCB

а№ӮаёҘа№ӮаёҒа№ү UGPCB