การแนะนำ

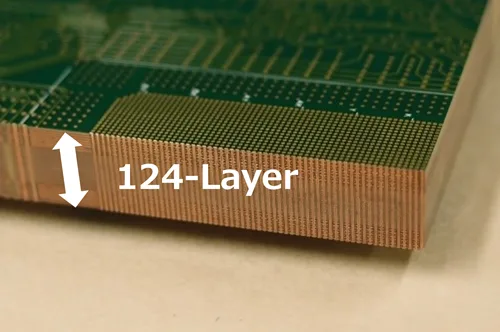

ขับเคลื่อนด้วยปัญญาประดิษฐ์ (AI) และคอมพิวเตอร์ประสิทธิภาพสูง (HPC), อุตสาหกรรมอิเล็กทรอนิกส์ทั่วโลกกำลังอยู่ระหว่างการปฏิวัติทางเทคโนโลยีโดยมีศูนย์กลางอยู่ที่ “ความหนาแน่นสูง, ความเร็วสูง, และความน่าเชื่อถือสูง” ในเดือนพฤษภาคม 2025, ผู้นำ ผู้ผลิต PCB เปิดตัวแผงวงจรพิมพ์ 124 ชั้นเชิงพาณิชย์แห่งแรกของโลก, ทำลายอุปสรรคอุตสาหกรรม 108 ชั้นที่มีมายาวนานในขณะที่รักษาความหนาของบอร์ด 7.6 มม. มาตรฐาน. เหตุการณ์สำคัญนี้ไม่เพียง แต่ให้การสนับสนุนฮาร์ดแวร์ที่สำคัญสำหรับเซิร์ฟเวอร์ AI, การทดสอบเซมิคอนดักเตอร์, และระบบการป้องกัน แต่ยังปลดล็อคพรมแดนใหม่ในเทคโนโลยีบรรจุภัณฑ์อิเล็กทรอนิกส์.

ทำลายอุปสรรค 108 ชั้น: โซลูชั่นด้านวิศวกรรมเบื้องหลัง PCBs 124 ชั้น

นวัตกรรมการผลิตที่แม่นยำ

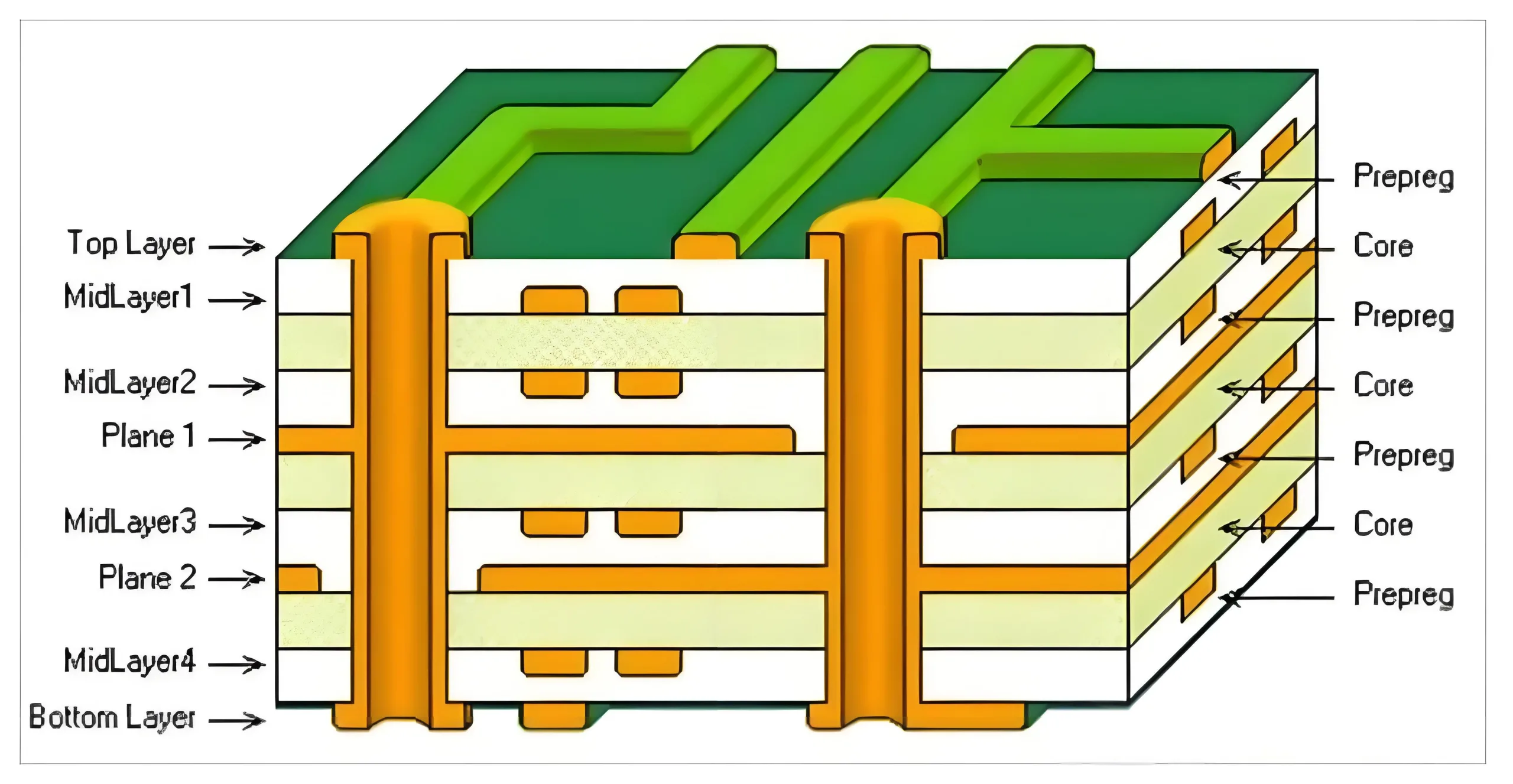

แบบดั้งเดิม การออกแบบ PCB เผชิญข้อ จำกัด เชิงกลและความร้อนที่ 100 เลเยอร์เนื่องจากการไหลของเรซิ่นไม่สอดคล้องกัน, ผ่านการล่มสลาย, และการเยื้องศูนย์. PCB 124 ชั้นที่ก้าวหน้าได้สำเร็จ 15% เลเยอร์เพิ่มขึ้น:

-

ไดอิเล็กตริกบางเฉียบ: 25µm เลเยอร์โดยใช้วัสดุที่สูญเสียต่ำ (เช่น, ล้ม 7) ด้วยการควบคุมอิมพีแดนซ์± 5% สำหรับ 112+ สัญญาณ GHz

-

3การเพิ่มประสิทธิภาพการเชื่อมต่อระหว่างกัน D: อาร์เรย์ Microvia เปิดใช้งานความหนาแน่นของสัญญาณ0.15mm²/mm, สอดคล้องกับ PCIE Gen6 และ CXL 3.0 โปรโตคอล

การรับรองความน่าเชื่อถือทางความร้อน

ได้รับการรับรองภายใต้มาตรฐาน MIL-STD-883G, PCB 124 ชั้นสามารถทนทานได้ 1,000+ วงจรความร้อน (-55° C ถึง 125 ° C) ในขณะที่รักษา <1% การสูญเสียสัญญาณที่ 80 MPA Mechanical Stress - ทำให้เหมาะสำหรับการบินและอวกาศและการป้องกัน.

การใช้งาน: เร่งฮาร์ดแวร์ AI และความก้าวหน้าของเซมิคอนดักเตอร์

เซิร์ฟเวอร์ AI & หน่วยความจำแบนด์วิดธ์สูง (HBM)

-

ความหนาแน่นของสัญญาณ: 18% เพิ่มการกำหนดเส้นทางคู่ที่แตกต่างกันต่อเลเยอร์

-

การจัดการความร้อน: microvias ที่เต็มไปด้วยทองแดงปรับปรุงการนำความร้อนโดย 30%, สำคัญสำหรับตัวเร่งความเร็ว 500W+ AI

การทดสอบระดับเวเฟอร์ & 3D บรรจุภัณฑ์

เปิดใช้งานความแม่นยำในการจัดตำแหน่งไมครอนย่อย (± 0.8 มม.) และการควบคุมการหน่วงของสัญญาณระดับ Picosecond สำหรับโมดูล HBM แบบซ้อนกัน-ตัวเปลี่ยนเกมสำหรับสถาปัตยกรรมที่ใช้ Chiplet.

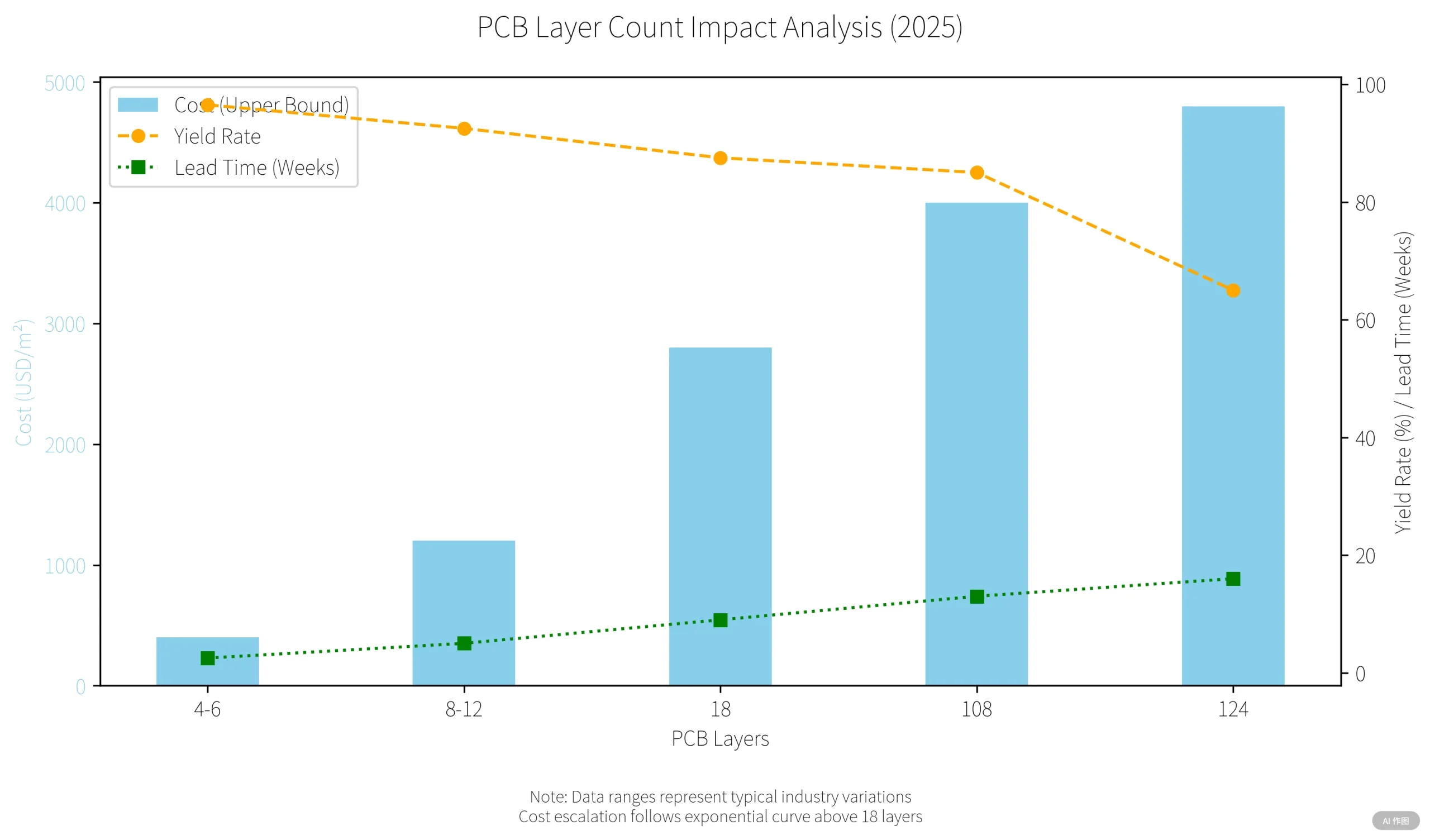

ความท้าทายด้านค่าใช้จ่าย & แผนงานที่ปรับขนาดได้

เศรษฐศาสตร์การผลิต

-

ค่าวัสดุ: 4,800/M2(VS.3,200/m²สำหรับ 108 ชั้น)

-

อัตราผลตอบแทน: 65% (16-รอบสัปดาห์) VS. 85% สำหรับแบบดั้งเดิม HDI

-

การวิเคราะห์ความล้มเหลว: จำเป็นต้องมีการทำลายล้างหน้าตัด 20% ข้อบกพร่องของความเครียดจากความร้อน

เส้นทางการยอมรับอุตสาหกรรม

-

การผลิตสารเติมแต่ง: ลดขั้นตอนการเคลือบด้วย 40%

-

EDA ที่ขับเคลื่อนด้วย AI: ทำนายผ่านจุดความเครียดด้วย 92% ความแม่นยำ, อาจเพิ่มอัตราผลตอบแทนให้ 75%

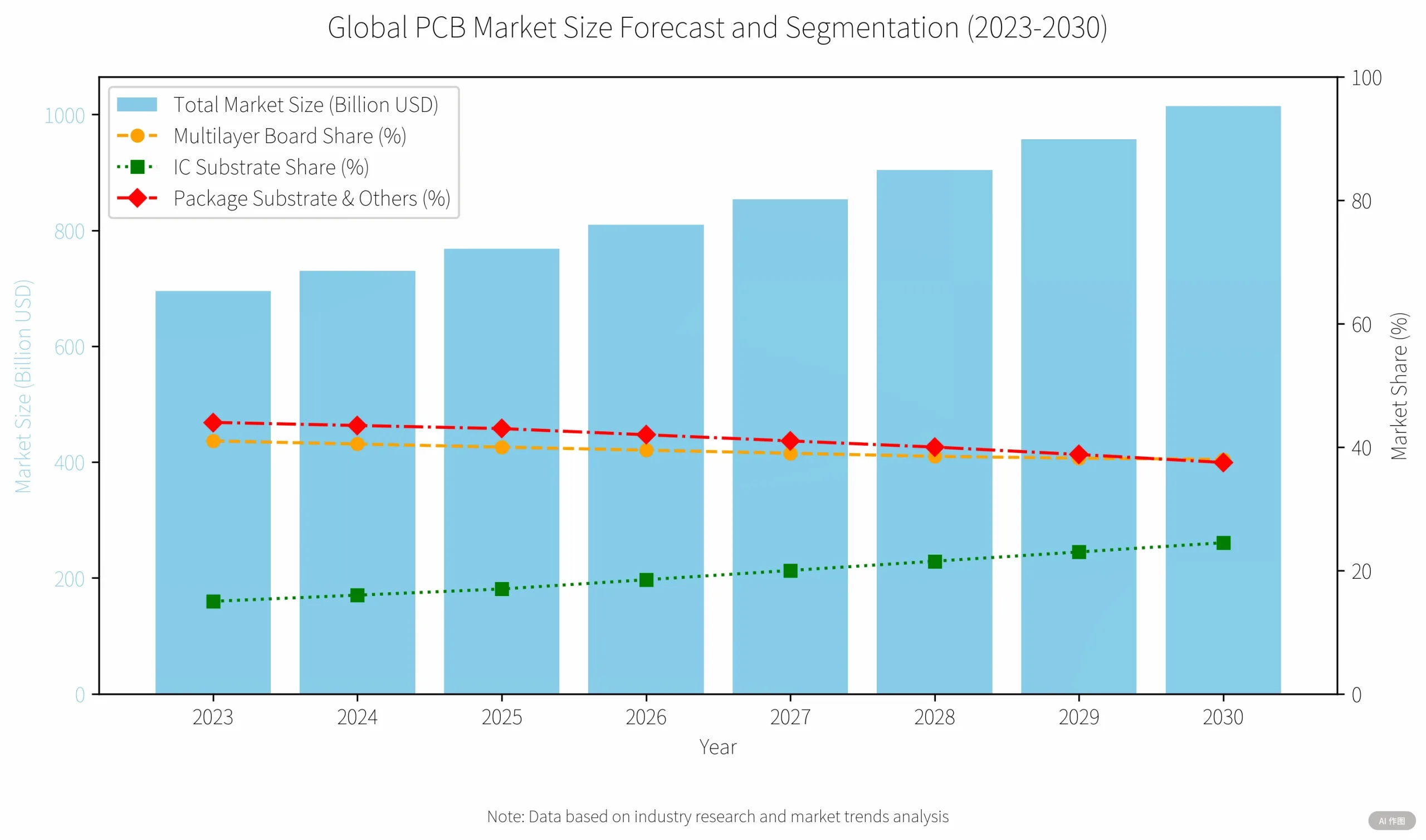

ตลาดแนวโน้ม: $49การเปลี่ยนแปลงอุตสาหกรรม B PCB

ไดรเวอร์การเจริญเติบโต

-

คลาวด์คอมพิวติ้ง: 70% CAGR ใน AI Server PCBS (หลักทรัพย์ Citic 2026 การฉายภาพ)

-

อุปกรณ์ AI ขอบ: 30% ค่าใช้จ่าย PCB เพิ่มขึ้นในสมาร์ทโฟนรุ่นถัดไป (ข้อมูลห่วงโซ่อุปทานของ Apple)

-

แนวโน้มการแปล: ผู้ผลิตจีนชอบ UGPCB การกำหนดเป้าหมายความจุ 3.6m m²/ปีสำหรับพื้นผิวขั้นสูง

บทสรุป: นวัตกรรมเชิงปฏิบัติเหนือบันทึกการนับเลเยอร์

ในขณะที่ไม่เกินต้นแบบ 129 ชั้นของ Denso (2012), PCB 124 ชั้นนี้กำหนดเกณฑ์มาตรฐานเชิงพาณิชย์ใหม่ผ่าน:

-

ความหนามาตรฐาน (7.6มม) สำหรับความเข้ากันได้ย้อนหลัง

-

ความน่าเชื่อถือของ mil-spec ที่ 85% ต้นทุนต้นแบบ

-

กระบวนการผลิตที่ปรับขนาดได้

เป็นควอนตัมคอมพิวเตอร์และ 6G เกิดขึ้น, นวัตกรรม PCB จะจัดลำดับความสำคัญความหนาแน่นของการทำงานมากกว่าจำนวนเลเยอร์ - การเปลี่ยนแปลงที่สำคัญสำหรับความก้าวหน้าทางเทคโนโลยีที่ยั่งยืน.

โลโก้ UGPCB

โลโก้ UGPCB