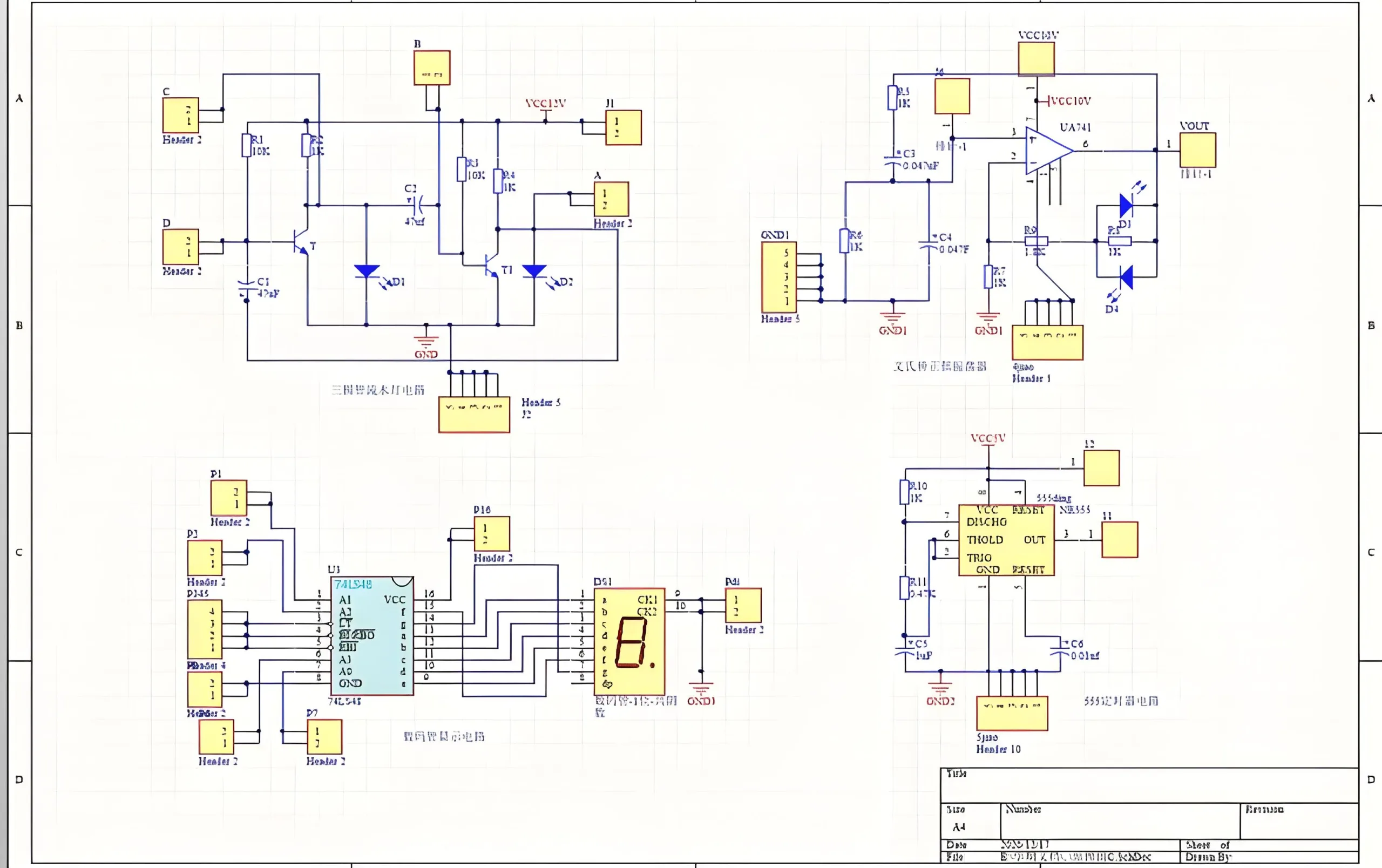

En la convergencia de circuitos digitales de alta velocidad y sistemas analógicos de precisión, un exquisitamente diseñado tarjeta de circuito impreso esquemático determina la viabilidad del producto - con 90% de fallas de diseño que se originan en el colapso de la integridad de poder.

Cuando los ingenieros enrutan la 37ª traza de longitud de longitud DDR4 en Altium Designer, impedancia Las discontinuidades ocultas en las pilas de capa degradan silenciosamente la integridad de la señal. Los datos de simulación UGPCB revelan: Los PCB con módulos de potencia no optimizados sufren 62% tasas de falla, mientras que los diseños que implementan nuestra tecnología de plano dividido reducen las tasas de error de bits a 10 ⁻¹².

La esencia de los circuitos: Principios básicos de los esquemas de PCB & Evolución

Desde diagramas de cableado hasta sistemas inteligentes

Los esquemas modernos han evolucionado a Ecosistemas de ingeniería inteligente:

-

Redes neuronales eléctricas: Incorporar 32 reglas de diseño (Ancho de rastreo/espaciado/impedancia/umbrales de diafonía); El gerente de restricciones de UGPCB sincroniza 12,000+ redes

-

Colaboración entre dominios: El análisis de Allegro SI muestra Margen de tiempo de ± 18ps Para caminos críticos en 6 capas Tablas de HDI, Requerir la co-optimización de la co-optimización de la empresa Schematic-PCB

Avances de herramientas de diseño revolucionarios

| Generación de herramientas | Software representativo | Ganancia de eficiencia | Caso de optimización de UGPCB |

|---|---|---|---|

| Diseño fundamental | Protel99SE | 1X línea de base | Compatibilidad de la biblioteca heredada para la migración del proyecto |

| Diseño de alta velocidad | Diseñador de Altius | 3.2incógnita | Error de coincidencia de longitud dinámica ≤0.01 mm |

| Diseño del sistema | Cadence Allegro | 5.7incógnita | 40% Mejora del margen del diagrama de los ojos a 16 Gbps |

Estudio de caso de UGPCB: La migración de Orcad a Allegro aumentó el éxito del enrutamiento de BGA de escape de 74% a 98%, reducir los ciclos de desarrollo por 21 días.

Metodología de diseño modular: Deconstrucción de circuitos complejos

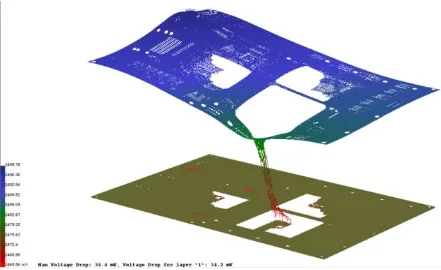

Integridad de poder: El diferenciador crítico

Fórmula de selección de topología:

H = frac{PAGS_{afuera}}{PAGS_{afuera} + PAGS_{sudoeste} + PAGS_{condición}} \Quad Texto{(Apuntar al>92\%)}

UGPCB 3D Análisis de árbol de energía:

-

Voltaje reducido caída de 220 mV a 35mV en ECU automotriz a través de Optimización de colocación de LDO

-

Aviones de energía híbridos: Las técnicas de plano dividido/mixto disminuyeron la ondulación por 67%

Control de precisión de rutas de señal de alta velocidad

Ecuación de control de impedancia:

Implementación de UGPCB:

-

Compensación de pares diferenciales: Asimilado logrado<2PS en módulos ópticos de 100 g

-

Em blindando paredes: 18Mejora de DB SNR en médico tarjeta de circuito impreso a través de aislamiento digital/analógico

Diseño de grado industrial: UGPCB 9 Tecnologías centrales

3D Optimización de la arquitectura de apilamiento

Configuración óptima de 8 capas:

L1: Señal (De alta velocidad) L2: Solid GND L3: Señal (Línea de strip) L4: Power L5: GND L6: Signal L7: Power L8: Señal (De baja velocidad)

Validación: 12Reducción de EMI DBμV/M, FCC Clase B certificado

Diseño impulsado por la fabricación (DFM) Precisión

UGPCB ± 0.025 mm de control de proceso:

-

Tecnología de microvia: 0.1ejercicios láser mm, 12:1 relación de aspecto

-

Espesor de cobre: ± 10% de tolerancia de grabado para capas externas de 2 oz

-

Puentes de máscara de soldadura: 0.075MM El ancho mínimo previene el puente SMT

Más allá del diseño: Servicios de ciclo de vida completo de UGPCB

Aseguramiento de la integridad de la señal

Fase de diseño: Hyperlynx La simulación previa a la capa elimina 90% riesgos

Fase de validación: La prueba TDR asegura <5% desviación de impedancia

Producción en masa: Base de datos de referencia dorada para el control de parámetros clave

Integración de fabricación inteligente

Resultados: 48-Entrega de prototipo de hora, 99.2% rendimiento de primer paso

Laboratorio futuro: Fronteras tecnológicas de UGPCB

Integración heterogénea del sustrato de silicio

2.5D TSV Interposers:

-

0.3Interconexiones de tono MM para la integración FPGA-HBM

-

Resistencia térmica reducida a 0.15 ° C/W

Revolución EDA impulsada por IA

Motor neuroroute:

-

8X Mejora de la eficiencia de enrutamiento

-

Función de optimización:

Min(ΔL, Crosstalk, Via_Count) -

Desplegado en una matriz de antena MMWave 5G tarjeta de circuito impreso diseños

UGPCB LOGO

UGPCB LOGO

WeChat

Escanea el código QR con WeChat