Cada avance microscópico en tecnología de envasado reforma los límites físicos de la electrónica.

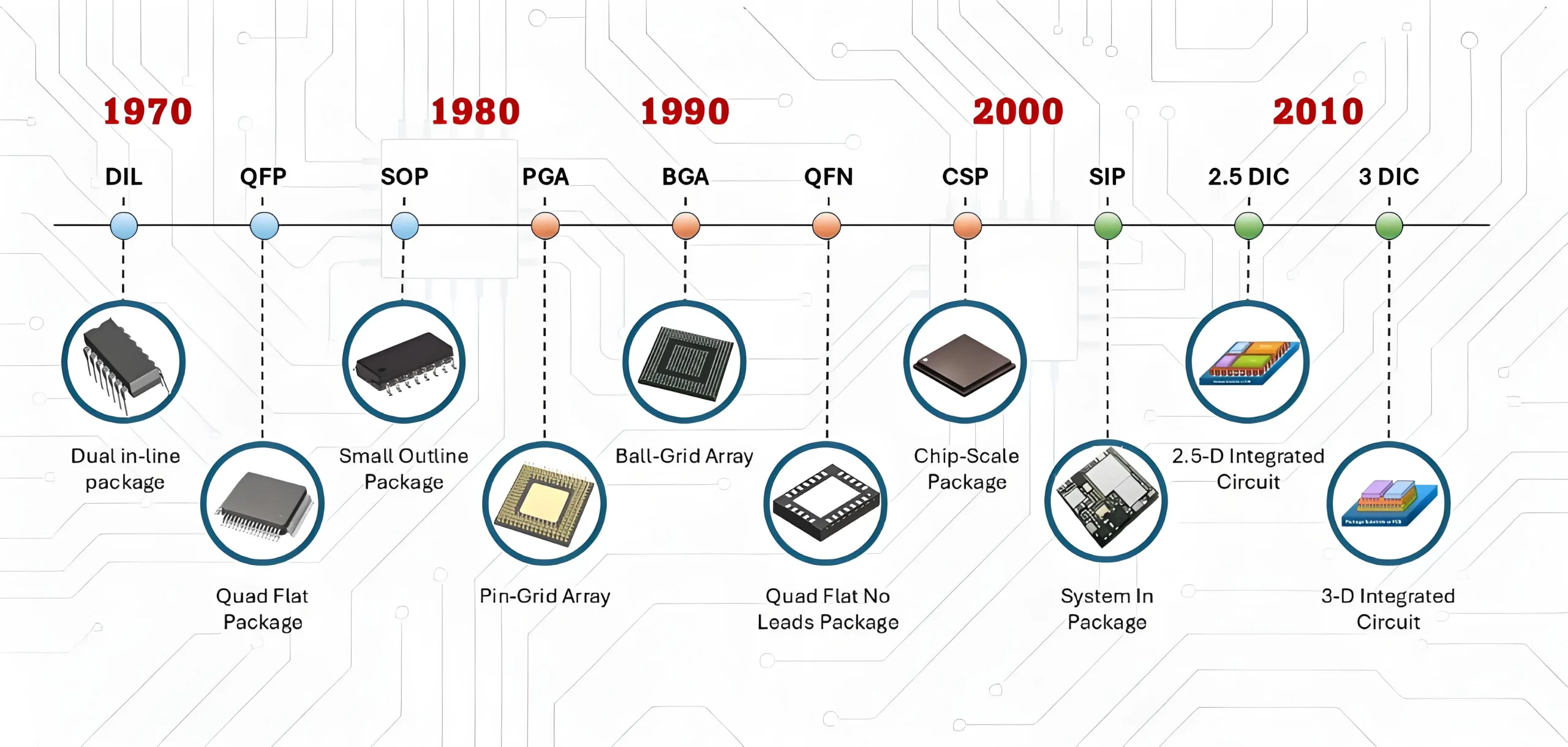

En la semana pasada Evolución del embalaje de chips: Desde DIP a X2SON - Cómo la miniaturización remodeló la electrónica, Exploramos la era del empaque de los agujeros (ADEREZO) y cómo los dispositivos de montaje en la superficie (COMPENSACIÓN, Observación, HIJO) miniaturización de dispositivo iniciado. Mientras que estas tecnologías colocaron cimientos de empaque modernos, el revolución de la miniaturización continúa. Hoy, Examinamos paquetes de mayor densidad, desde CSP a nivel de cuádruple a nivel de obleas, y su impacto en diseño de PCB límites.

Paquetes de quad-plato: El equilibrio de densidad de espacio

Paquetes de quad-plato (MFP, PLCC/QFJ, QFN) representar una evolución crítica hacia una mayor densidad de E/S utilizando los cuatro bordes de los paquetes.

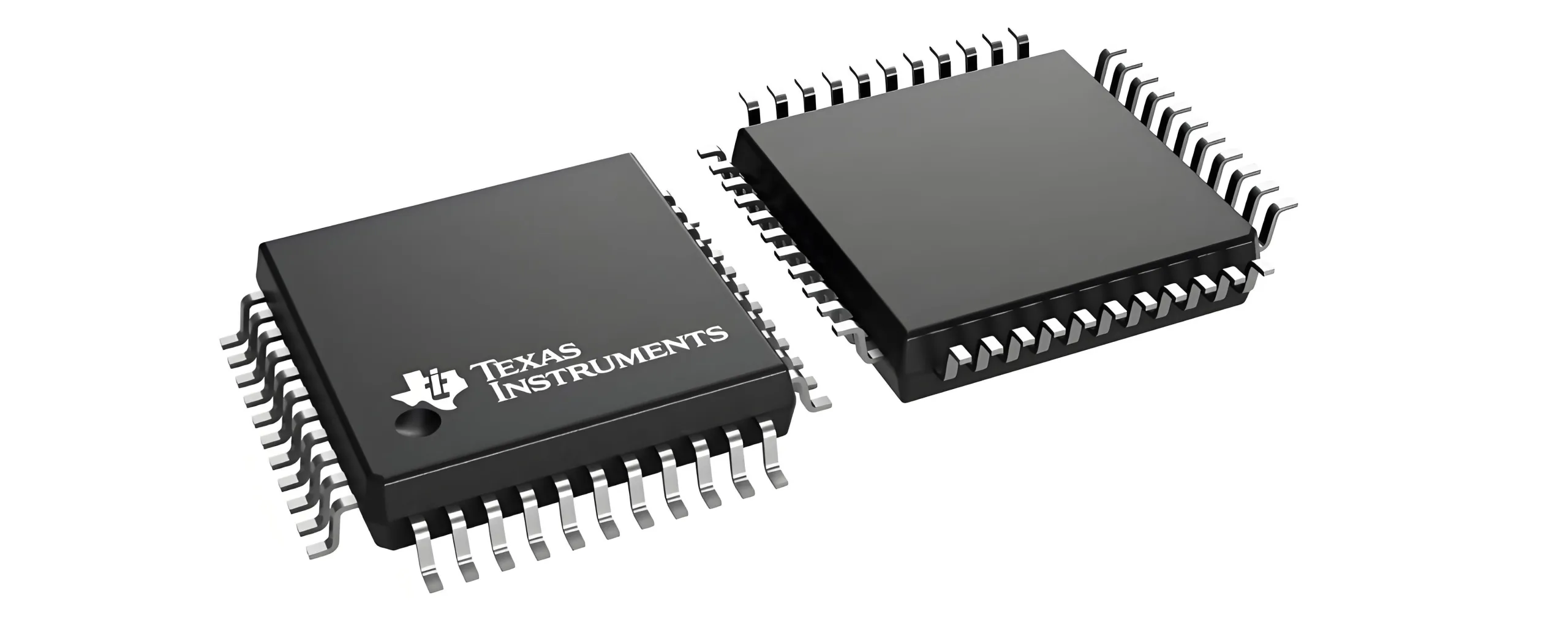

MFP: El pionero de la densidad de ala de gaviota

MFP (Paquete plano cuádruple) Características icónicas “ala de gaviota” (En forma de L) cables que se extienden desde todos los lados. Es pitch (0.4mm/0.5 mm/0.65 mm) dictados Enrutamiento de PCB Densidad y precisión de soldadura.

Variantes QFP:

-

Tamaño/grosor: LQFP (De bajo perfil), TQFP (Delgado), VQFP (Muy delgado)

-

Material: PQFP (Plástico), MQFP (Metal)

-

Mejorado térmico: HQFP, HLQFP, Htqfp, HVQFP

-

Protección: Bqfp (Bumpered: las almohadillas de la tela evitan los cables doblados)

La gestión térmica es crítica. La fórmula de resistencia térmica de unión a ambiente θja = (TJ - TA)/PAG (dónde TJ= temperatura de unión, Frente a= temperatura ambiente, PAG= potencia) gobierna el diseño de disipación de calor.

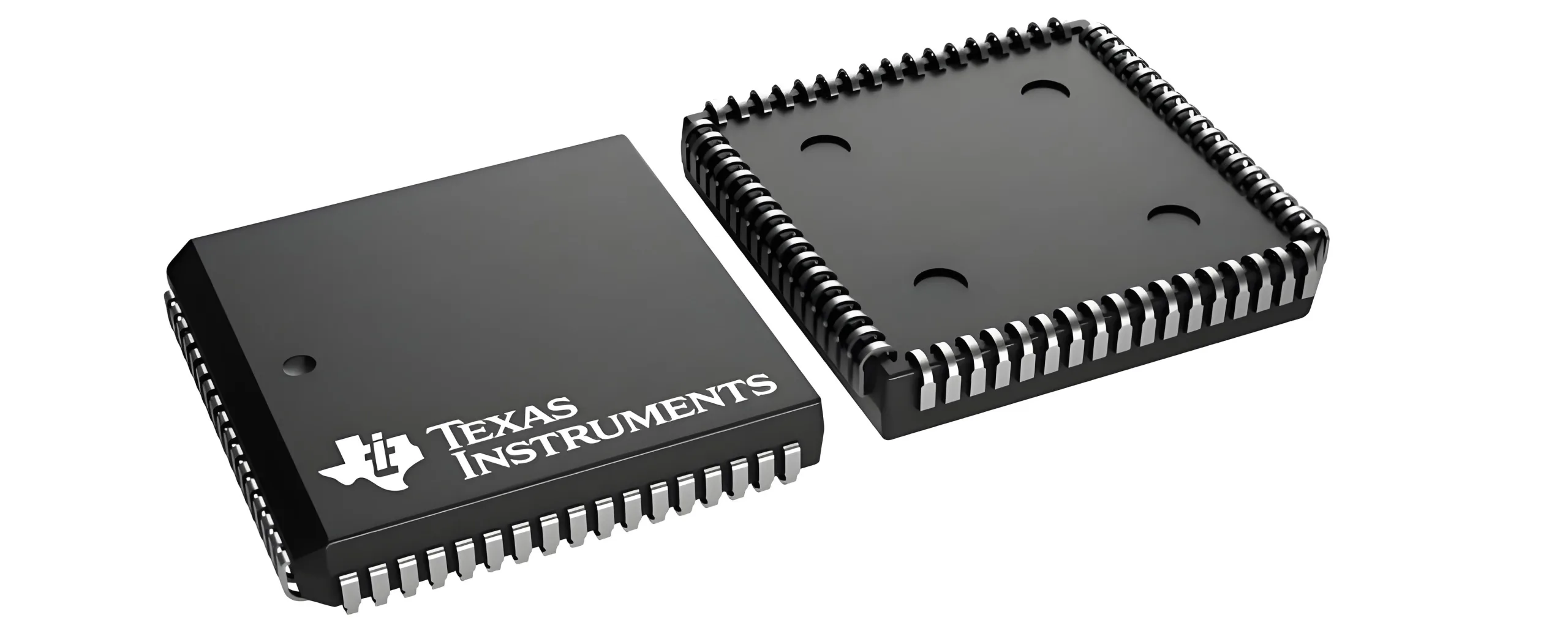

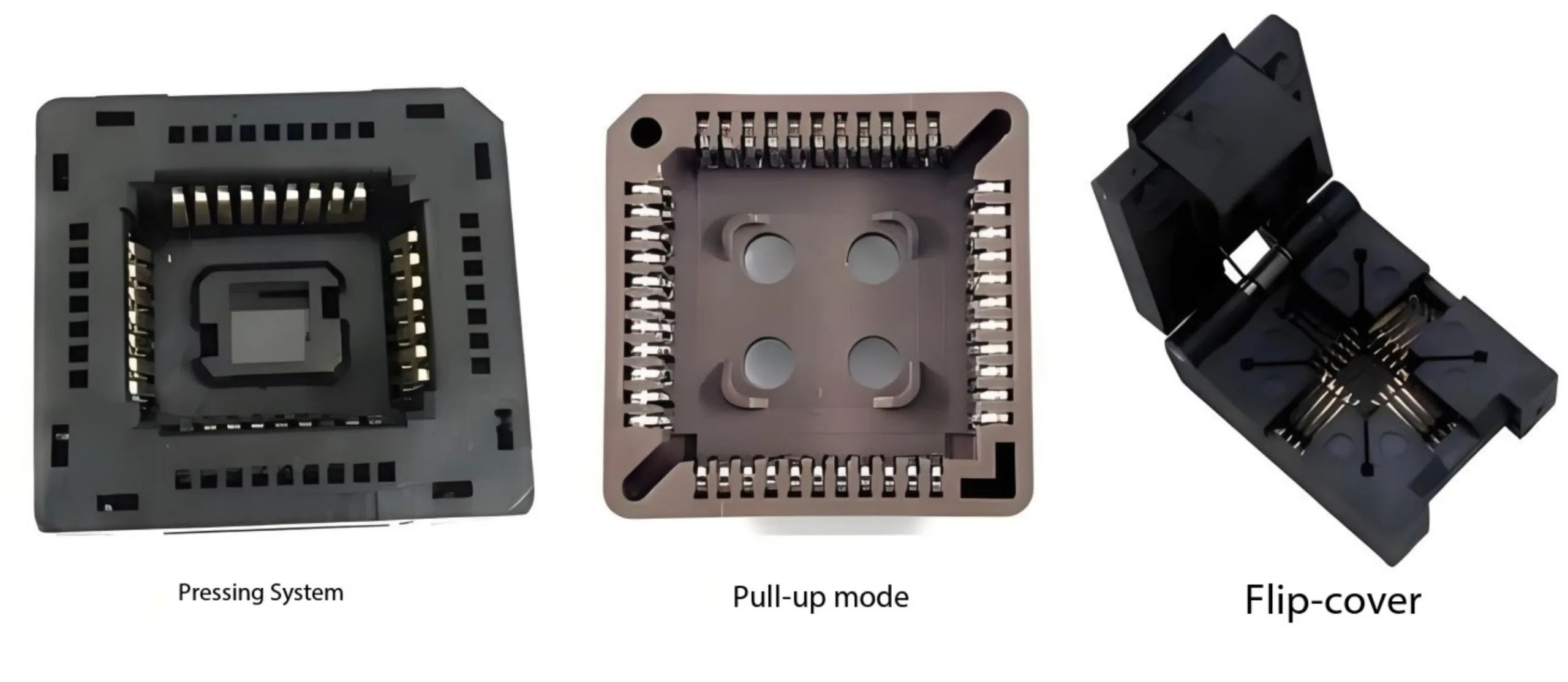

PLCC/QFJ: Estabilidad a través de J-Leads

PLCC (Portador de chips con plástico de plástico) o QFJ (Quad Flat J-leaded) Utiliza cables en forma de J hacia abajo para la estabilidad mecánica contra la vibración/estrés térmico.

Ventaja de estandarización: La alta compatibilidad de PLCC/QFJ con las pruebas de producción de Sockets de prueba universal. Aunque QFJ es técnicamente preciso, “PLCC” permanece preferido a la industria.

QFN: Avance de la miniaturización sin plomo

QFN (Quad Flat No-LEAD) Elimina los cables externos, Conectando a través de:

-

Almohadilla expuesta (EP): Camino térmico directo a tarjeta de circuito impreso cobre

-

Flancos humectables: Almohadillas de soldadura de pared lateral

Ventajas clave:

-

Ultra compacto: 40% más pequeño que QFP

-

Superioridad eléctrica: Las rutas más cortas reducen la inductancia parásita (L ≈ μ · L/W)

-

Eficiencia térmica: Inferior θja vs. QFP de la misma tamaño

Evolución del grosor: LQFN → UQFN → VQFN → WQFN → X1QFN → X2QFN. LCC (LPCC/LCCC) es su variante de cerámica/plástico sin plomo.

Paquetes de matriz: Límites de densidad de revolucionario

Cuando el quad-flat alcanza los límites de E/S, paquetes de matriz (LGA, BGA) Habilitar densidad de interconexión 2D.

LGA: Conexión elástica de precisión

LGA (Matriz de cuadrícula de tierra) usa contactos de metal alineados con precisión (p.ej., LGA775: 775 contactos) apareamiento con alfileres.

Valor central:

-

Capacidad: Actualizaciones/mantenimiento de la CPU

-

Baja inductancia: Rutas de señal cortas

-

Alta fiabilidad: Ideal para CPU (Intel/AMD)

Limitación: Altos costos de enchufe/tamaño favorecen BGA en dispositivos compactos. Nota: Las LGA pueden ser soldadas por SMT directamente.

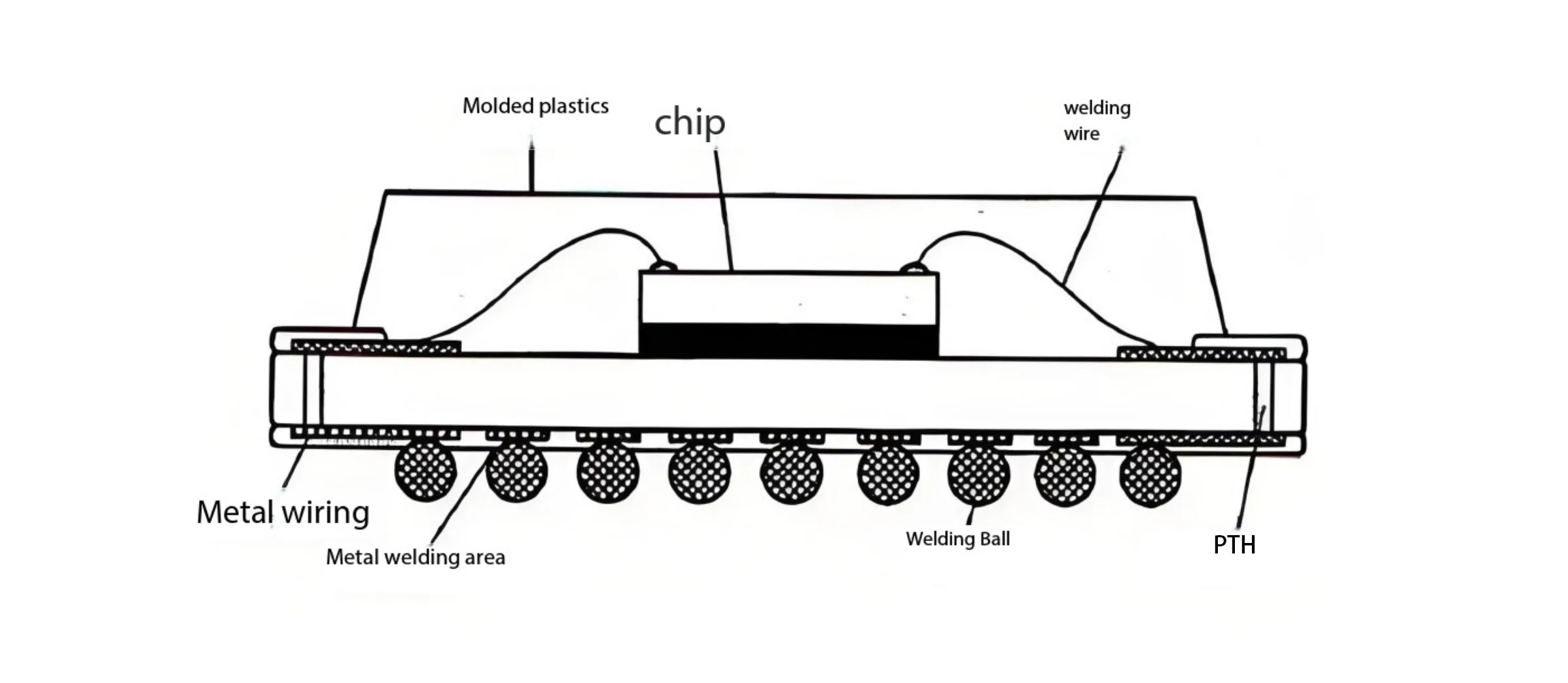

BGA: El dominio de la bola de soldadura

BGA (Matriz de rejilla de bolas) se conecta a través de una matriz de bola de soldadura. Bola de pelota (0.3–1.0 mm; <0.2MM para FBGA) es crítico.

Ventajas transformadoras:

-

Densidad alta: >1,000 Yo/nosotros (VS. QFP ~ 300)

-

Ahorro de espacio: 30%+ Reducción del área vs. MFP

-

Eléctrico/térmico: Delebre de señal bajo; Las bolas conducen calor

-

Autoalineación: Asamblea de ayudas de tensión superficial

Familia BGA:

-

Material: PBGA (Plástico), CBGA/CABGA (Cerámico)

-

Tamaño/tono: NFBGA/FBGA (Pitch), Tinybga, DSBGA/WCSP (Dimensionador), LFBGA/VFBGA (Delgado)

-

Integración:

-

FCBGA (Chip): Conexión directa de muerte a sus sustrato a través de Microbumps

-

Estallido (Paquete de paquete): Apilamiento vertical (p.ej., lógica + memoria)

-

PG-WF2BGA: Embalaje a nivel de oblea de ventilador

-

Desafíos: Inspección de rayos X (Axi), Reelaboración compleja, Coincidencia de cte Materiales de PCB.

Comparación de paquetes de matriz

| Característica | PGA (Matriz de cuadrícula) | LGA (Matriz de cuadrícula de tierra) | BGA (Matriz de rejilla de bolas) |

|---|---|---|---|

| Conexión | Alfileres rígidos | Contactos planos | Bolas de soldadura |

| Fuerza clave | Confiabilidad del socket | Densidad + encatible | Densidad máxima/tamaño mínimo |

| Retraso de la señal | El más alto | Medio | El más bajo |

| Aplicaciones | Legacy CPU/Industrial | CPU de escritorio/servidor | Móvil/GPU/SOC |

| Espacio PCB | Grande | Medio | Compacto |

Escala de chips & Paquetes a nivel de obleas: Acercándose a los límites físicos

CSP: Redefinir los límites del tamaño

CSP (Paquete de escala de chips) métrica clave: Tamaño del paquete ≤ 1.2 × Tamaño de muerte (VS. 2–5 × para tradicional). BGA esencialmente miniaturizado (FBGA/VFBGA) con tono más fino (0.2–0.5 mm).

Valor: Miniaturización definitiva para wearables/sensores.

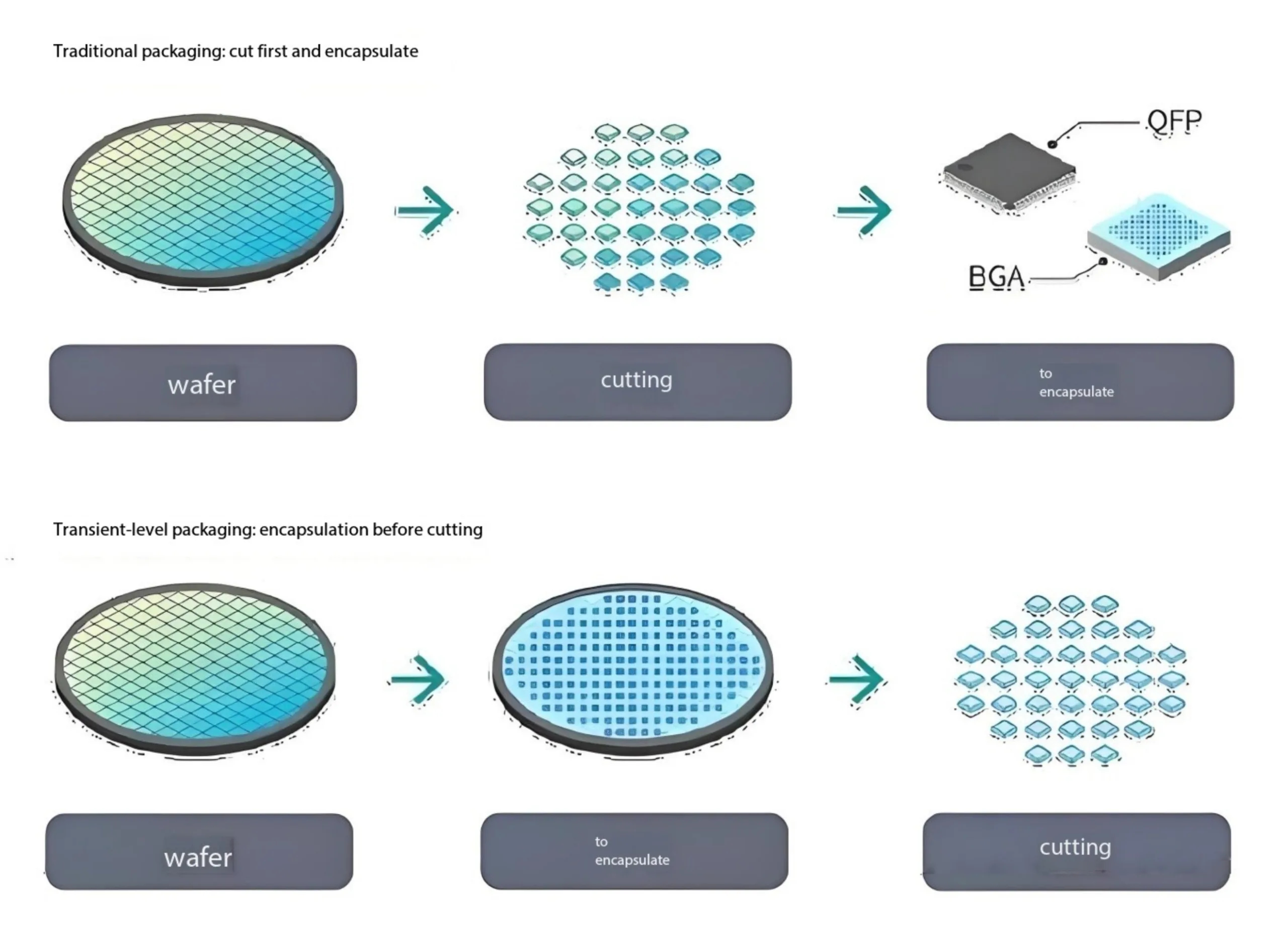

ULC: La revolución a nivel de oblea

El embalaje de nivel WLCSP/WAFER completa todos los pasos (RDL, balón) en la oblea antes de la cortesía.

Ventajas disruptivas:

-

Tamaño mínimo: ≈ dimensiones de die

-

Reducción de costos: 30-50% más económico (No hay sustratos/molduras)

-

Rendimiento máximo: Las interconexiones más cortas, Parasitarios más bajos

Tipos de WLCSP:

-

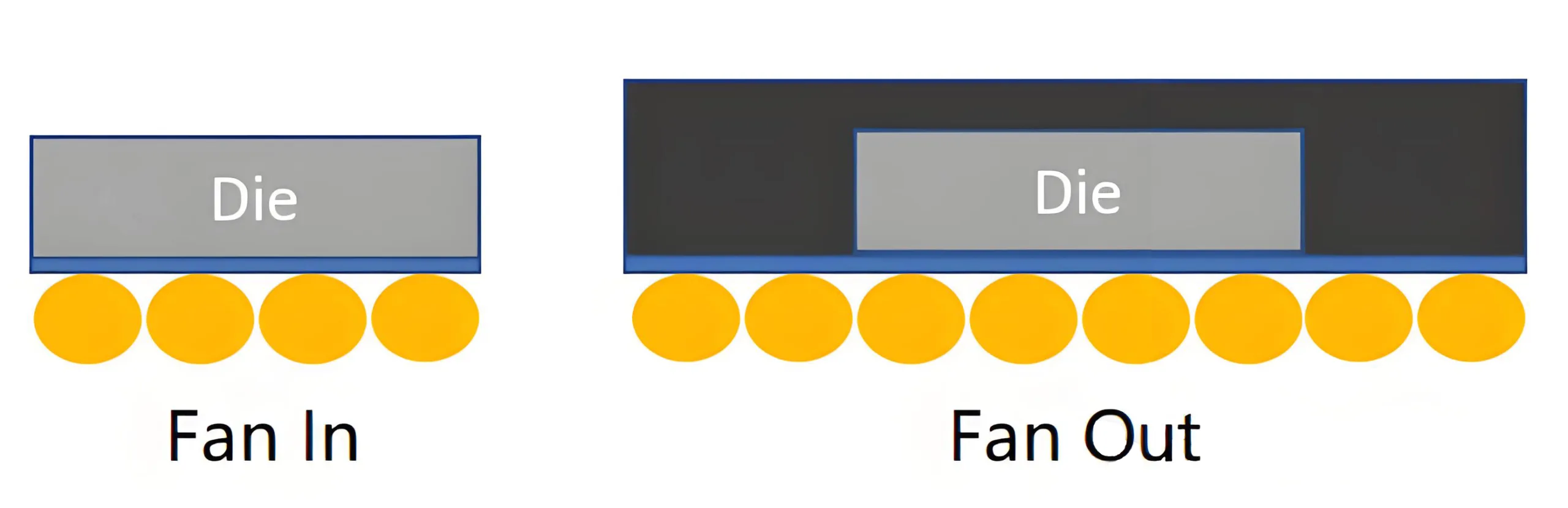

Fan-In WLCSP:

-

Bolas dentro del área de Die

-

Tamaño del paquete = tamaño de dado

-

Bajo costo para sensores/PMIC

-

-

Ventilador WLCSP (p.ej., Información TSMC, Samsung Fo-PLP):

-

Las pelotas se extienden más allá de la muerte

-

Tamaño del paquete > tamaño de matriz

-

Mayor densidad de E/S, integración múltiple

-

Para módulos premium SOCS/RF

-

ID de visual: Silicón no encapsulado (VS. DFN moldeado por resina).

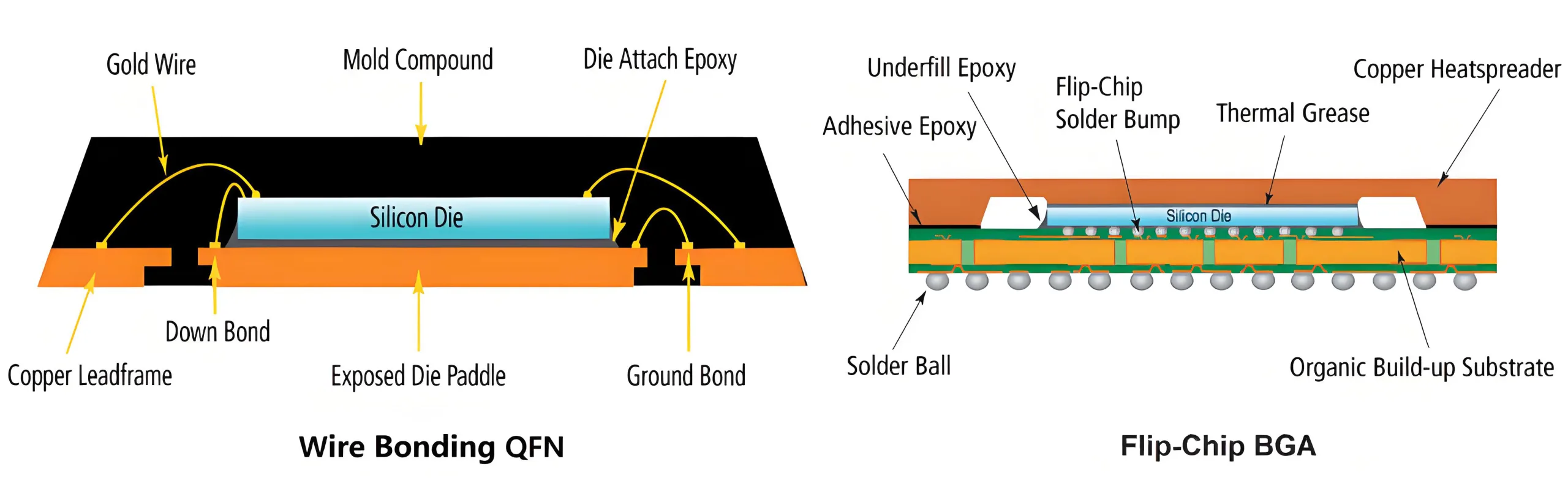

Morfología del embalaje & Técnicas de unión

Formulario de paquete externo (QFP/BGA/WLCSP) y la unión interna están intrínsecamente vinculadas:

-

Enlace de alambre:

-

Maduro, bajo costo

-

Domina QFP/QFN/BGAS de rango medio

-

Tener/con cables; E/S moderada

-

-

Chip:

-

Dies se une boca abajo a través de Microbumps

-

Las interconexiones más cortas, inductancia más baja

-

Esencial para FCBGA/WLCSP/CSP de alto rendimiento

-

Conclusión & Future Frontiers

De QFP a LGA/BGA y finalmente CSP/WLCSP, La evolución del embalaje de chips es un Crónica de compresión espacial, ganancias de rendimiento, y optimización de costos. Cada salto de miniaturización reorganiza el diseño de PCB: traza las huellas más finas, multicapa IDH, y materiales avanzados.

Siguiente frontera: Tecnologías como TSV (A través de Silicon a través de), Sorbo (Sistema en paquete), y 2.5D/3D IC ahora habilita la integración heterogénea 3D, Empujar el diseño de PCB en nuevas dimensiones: para ser explorado en nuestro próximo artículo.

Cuando mil millones de transistores encajan en un paquete de tamaño de grano de arena, Batallas de ingeniería electrónica a escala molecular.

UGPCB LOGO

UGPCB LOGO

Gracias por compartir la información con nosotros..

Vaya, este blog es magnífico. Me gusta mucho leer tus artículos.. Sigan con las buenas pinturas.! tu reconoces, Mucha gente está buscando esta información., puedes ayudarlos mucho.