Introducción: Importancia industrial y desafíos técnicos de a través del llenado

En 2023, lo global tarjeta de circuito impreso mercado superado $89.3 mil millones (Prismark), con a través de la tecnología de llenado que influye críticamente sobre 30% Fluctuaciones de rendimiento en dispositivos de comunicación 5G. Este artículo analiza las ecuaciones termodinámicas y las matrices de procesos para revelar cómo mediante el relleno de impactos de la integridad de la señal y la confiabilidad térmica.

1. A través del marco de tecnología de llenado

1.1 Microvia Física y ventana de proceso

Por IPC-6012E, Los VIA se definen como agujeros conductores ≤0.70 mm (28mil). La ventana del proceso de llenado sigue:

D = (K × T)/(σ × η)

Dónde:

- D: Diámetro máximo de relleno (milímetros)

- t: Sustrato TG (°C)

- a: Tensión superficial de resina (MN/M)

- o: Viscosidad de relleno (Pa · s)

- k: Coeficiente de proceso (0.02–0.05)

Para sustratos FR-4 (TG = 140 ° C), relleno de agujeros >0.40mm requiere materiales con σ<25mn/my η<120Pa · s.

2. Física de llenado de resina

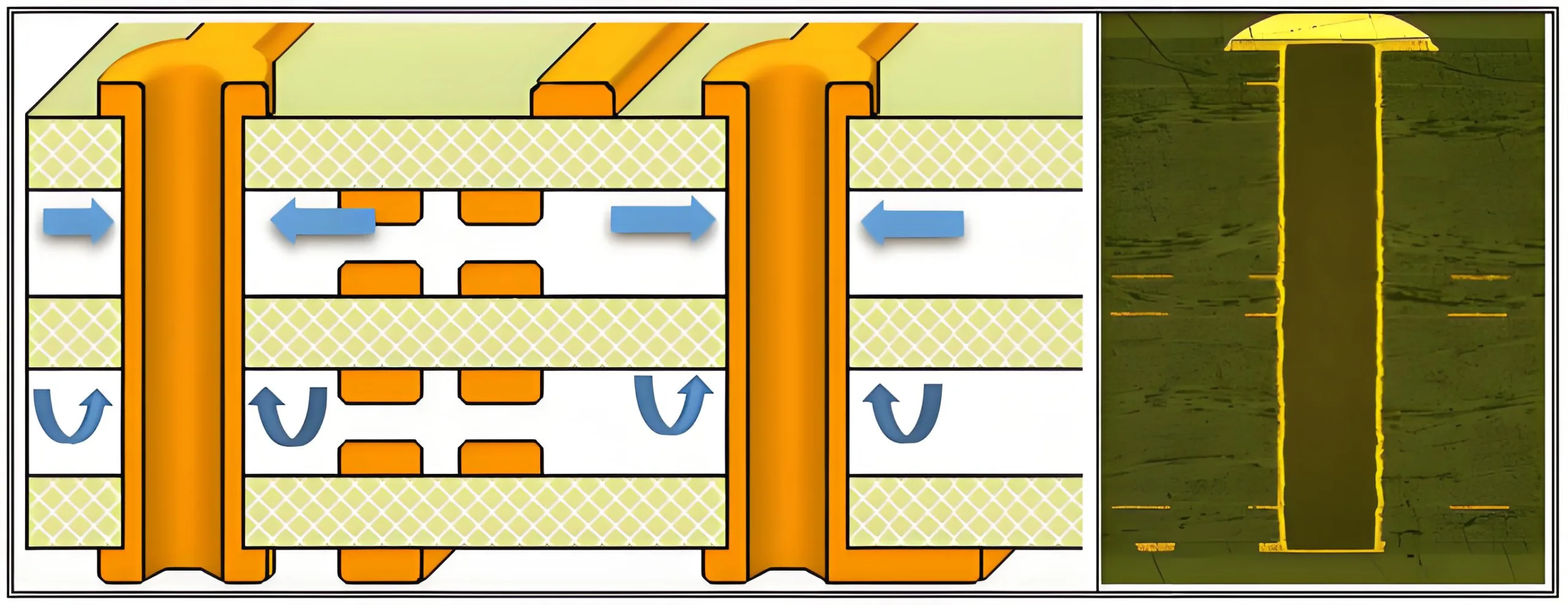

2.1 Enterrado a través del umbral de profundidad

El llenado de resina se vuelve obligatorio para las vías enterradas ≥0.8 mm debido a la dinámica de flujo de laminación:

P = (γ × cosθ)/(R × H)

Dónde:

- PAG: Presión de relleno (MPA)

- do: Tensión superficial previa

- th: Ángulo de contacto

- riñonal: A través de radio

- H: A través de la profundidad

A h≥0.8 mm, presión de laminación estándar (3–5MPA) no puede llenar los vacíos, Requerir el llenado de resina asistida por vacío.

2.2 Resina vs. Llenado de laminación: 6-Comparación dimensional

| Parámetro | Relleno de resina | Llenado de laminación |

|---|---|---|

| Uniformidad de espesor | ±5% | ± 15% |

| Riesgo de delaminación | <0.1% | 0.5–1.2% |

| Costo | $0.35/dm² | $0.12/dm² |

| Ancho mínimo de traza | 50μm | 75μm |

| Ciclos térmicos | 3,000 | 1,500 |

| Pérdida de señal (@10ghz) | 0.15db/pulgada | 0.25db/pulgada |

3. Proceso de llenado de máscara de soldadura

3.1 Modelo de flujo de tinta en imágenes negativas

El relleno de máscara de soldadura sigue una ecuación modificada de Hagen-Poiseuille:

Q = (πr⁴ΔP)/(8μl) × (1 – e^(-T/T))

Con tiempo constante t = mr²/(4do), explicando 50% Tasas de llenado en vías semi llenados cuando el tiempo de exposición t≈τ.

3.2 Estudio de caso de falla de la junta de HASL

VIAS sin llenar en la estación base 5G PCB causó cuentas de hojalata, modelado por la ecuación de Arrhenius:

t_f = a × exp(EA/(kt))

Las pruebas mostraron que MTBF se redujo de 10 a 2.3 años a 85 ° C/85%HR. Implementación de VIA de 0.30 mm con aberturas de máscara de soldadura ≤(Vía diámetro +0.08 mm) Defectos reducidos de cuentas de estaño de 12% a 0.7%.

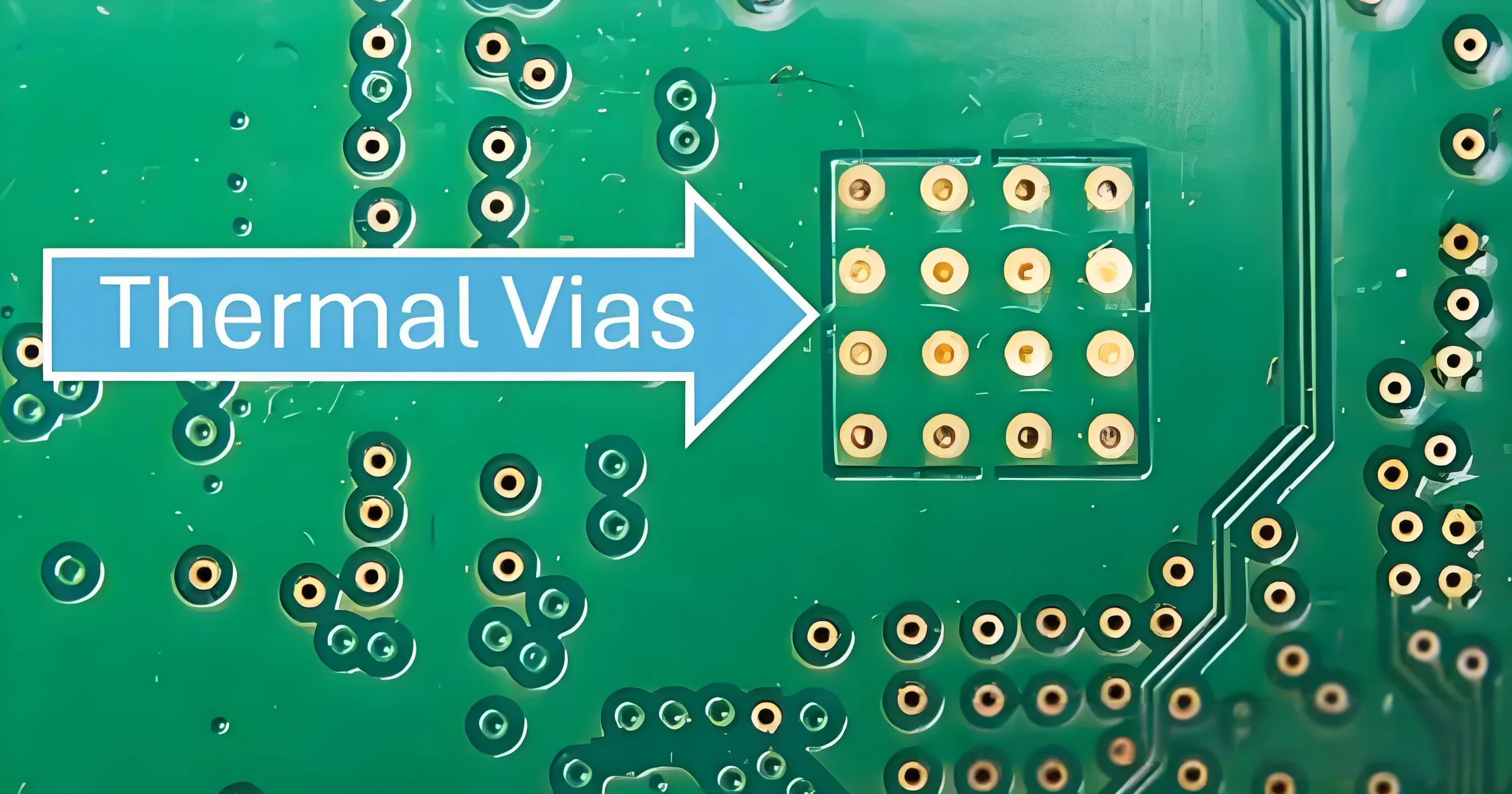

4. Avanzado a través de tecnologías de llenado

4.1 Llenado conductivo para el blindaje de EMI

El relleno de epoxi plateado mejora la efectividad de blindaje (Con):

SE = 20Log(1/(1-riñonal)) + 10registro(norte)

En 80% tarifa de llenado (P = 0.8), SE mejora en 18dB a 1 GHz.

4.2 Llenado de cobre chapado para la integridad de la señal

Via por impedancia llena de cobre:

Z0 = (87/√ε_r)LN(5.98H/(0.8w+t))

Los pilares de cobre reducen la variación de impedancia de ± 15% a ± 5%, Bajando BER de 10⁻⁶ a 10⁻¹² a 28 Gbps.

5. Marco de decisión de proceso

Costo total de propiedad (TCO) Análisis

- Electrónica de Consumo: El llenado de máscara de soldadura ofrece TCO de 5 años más bajo

- Automotor: Resina + El llenado parcial de cobre asegura la confiabilidad

- Militar: Los pilares de cobre optimizan la integridad de la señal

Conclusión

A través del relleno para aplicaciones 6G

A medida que las frecuencias de Terahertz exigen menos de 50 μm a través de la precisión, La sinterización de nano-silver emerge como un avance. Dominar a través de Filling Physics conducirá a la próxima generación PCB de alta frecuencia innovación.

UGPCB LOGO

UGPCB LOGO