No reino do analógico projeto de circuito, amplificadores operacionais, resistores de precisão, e os capacitores costumam ser os holofotes. No entanto, o verdadeiro determinante dos limites de desempenho do sistema é o cérebro oculto que trabalha nos bastidores: o Placa de circuito impresso (PCB). Esta base silenciosa carrega todos os componentes enquanto governa integridade do sinal, supressão de ruído, e confiabilidade do sistema através de cada milímetro de traço, cada camada dielétrica, e cada decisão de aterramento.

Ciência de Materiais PCB: Decodificando o desempenho de alta frequência além das classificações FR

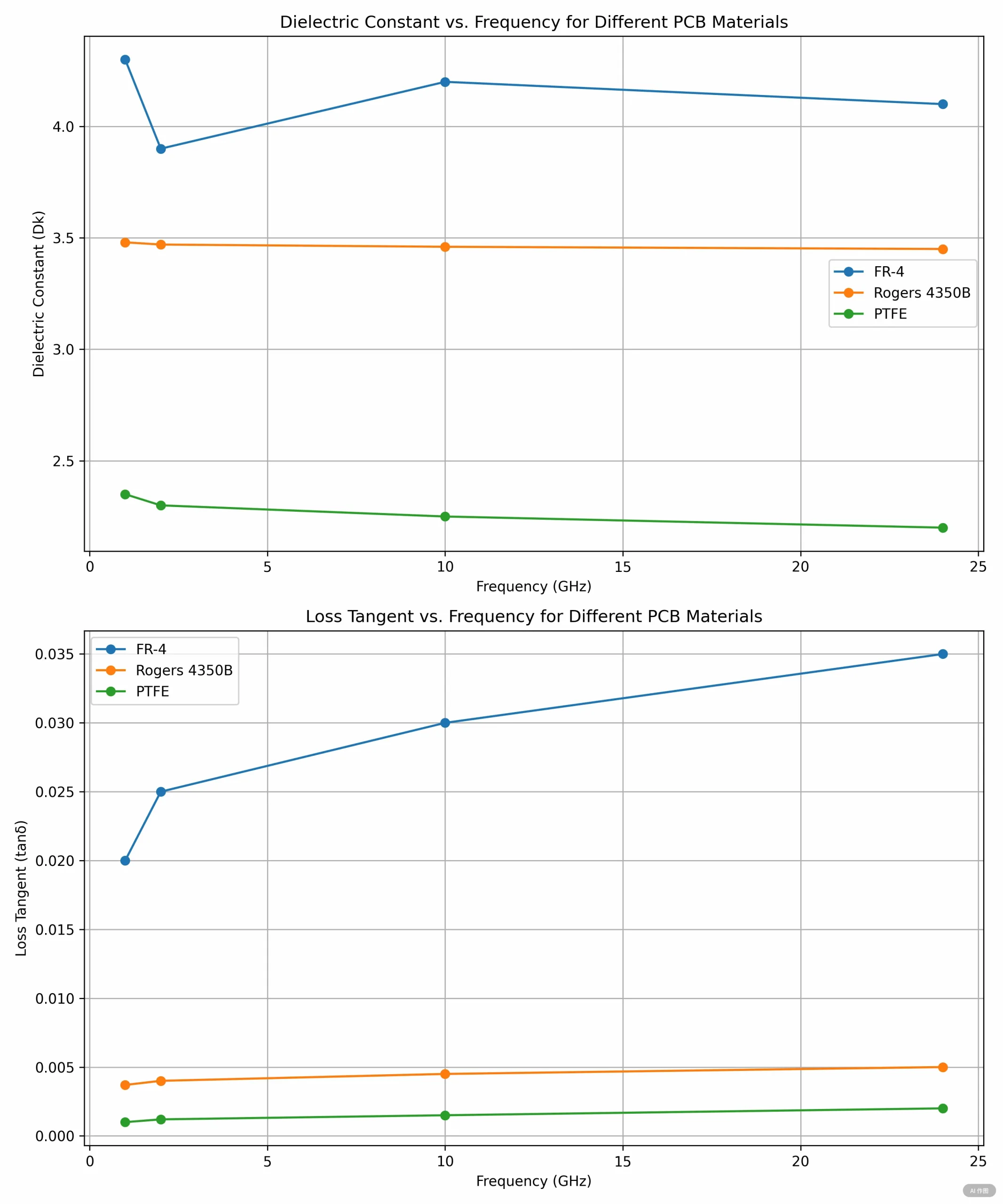

Ao discutir Materiais de PCB, As classificações de inflamabilidade do FR-4 são apenas o prólogo. Para circuitos analógicos de alta velocidade, Constante dielétrica (Dk) e Fator de dissipação (tanδ) são as mãos invisíveis moldando o destino do sinal.

Velocidade de propagação do sinal (v) é determinado por:

v = c / √(ε_r)

Onde *c* = velocidade da luz, e_r = permissividade relativa. O ε_r do FR-4 flutua entre 4.2-4.8, causando até 5% variação de atraso de sinal. Mais criticamente, suas características de perda – em 10 GHz, o padrão FR-4 exibe tanδ = 0,02, igualando a 0.5Perda de sinal em dB por polegada.

Interação umidade-temperatura prova ser particularmente letal em circuitos de precisão:

-

1% a absorção de umidade reduz a resistência da superfície FR-4 em três ordens de grandeza

-

15% A deriva Dk a 85 ° C muda as frequências centrais do filtro catastroficamente

Visão especializada: PCBs médicos usando Rogers 4350B (ε_r=3,48±0,05) manter <2% Variação Dk de -40°C a +150°C – crítica para equipamentos de monitoramento de sustentação da vida.

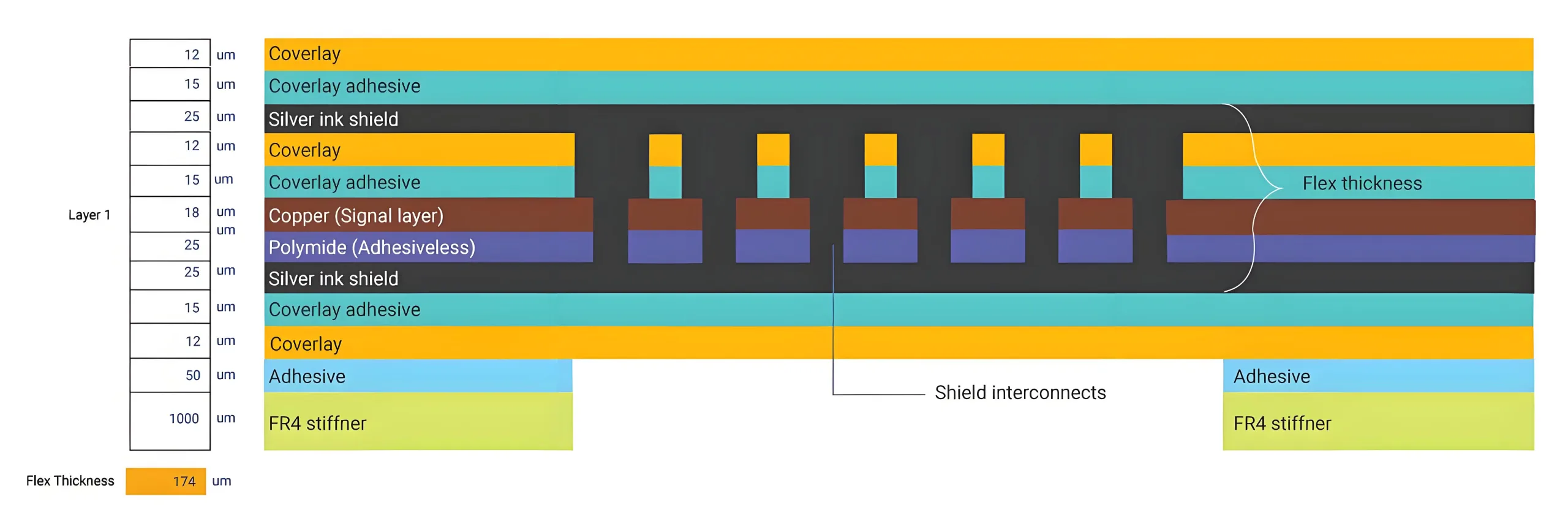

Arquitetura de empilhamento de PCB: Caminhos Atuais de Engenharia & Blindagem EMI

Limitações de camada única/dupla

Além dos sinais de 10 MHz, 1.6placas dupla-face de mm revelam fraquezas da camada de aterramento. Capacitância intercalar:

C = (ε_0 * ε_r * A) / d

Placas padrão de 1,6 mm alcançam apenas 35pF/in² – insuficiente para >100Supressão de ruído em MHz.

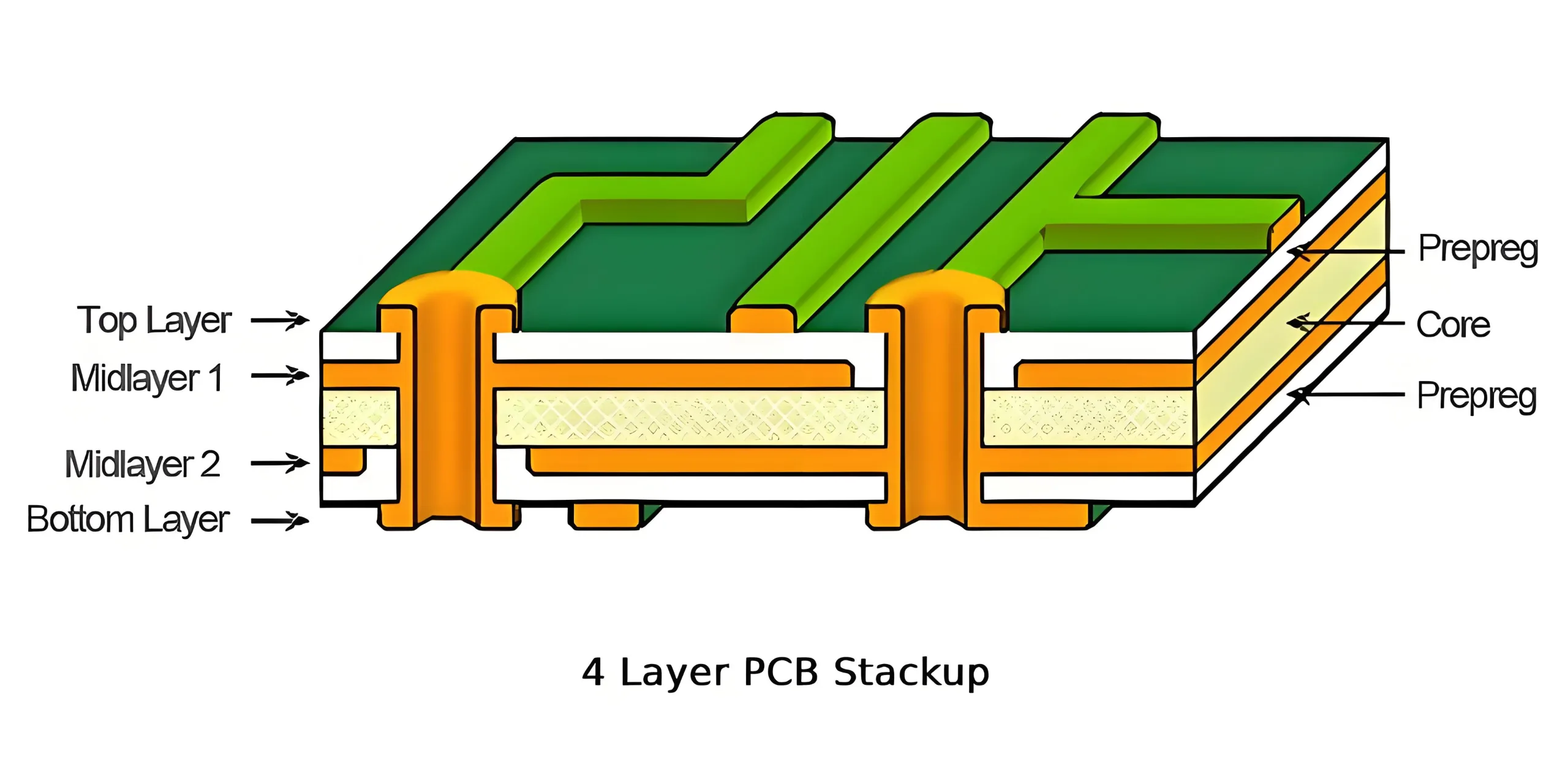

Revolução de empilhamento de quatro camadas

Planos de energia/terra dedicados transformam o controle de impedância:

-

0.2dielétricos de mm aumentam a capacitância para 280pF/in²

-

A resistência do plano terra cai para 1/100 da camada única

-

A atenuação do ruído irradiado melhora em 40dB

Dados de validação: UGPCB testes de laboratório mostram que designs de 4 camadas reduzem o ruído de saída do amplificador operacional de 78μVpp para 12μVpp - 85% melhoria.

Dados de validação: UGPCB testes de laboratório mostram que designs de 4 camadas reduzem o ruído de saída do amplificador operacional de 78μVpp para 12μVpp - 85% melhoria.

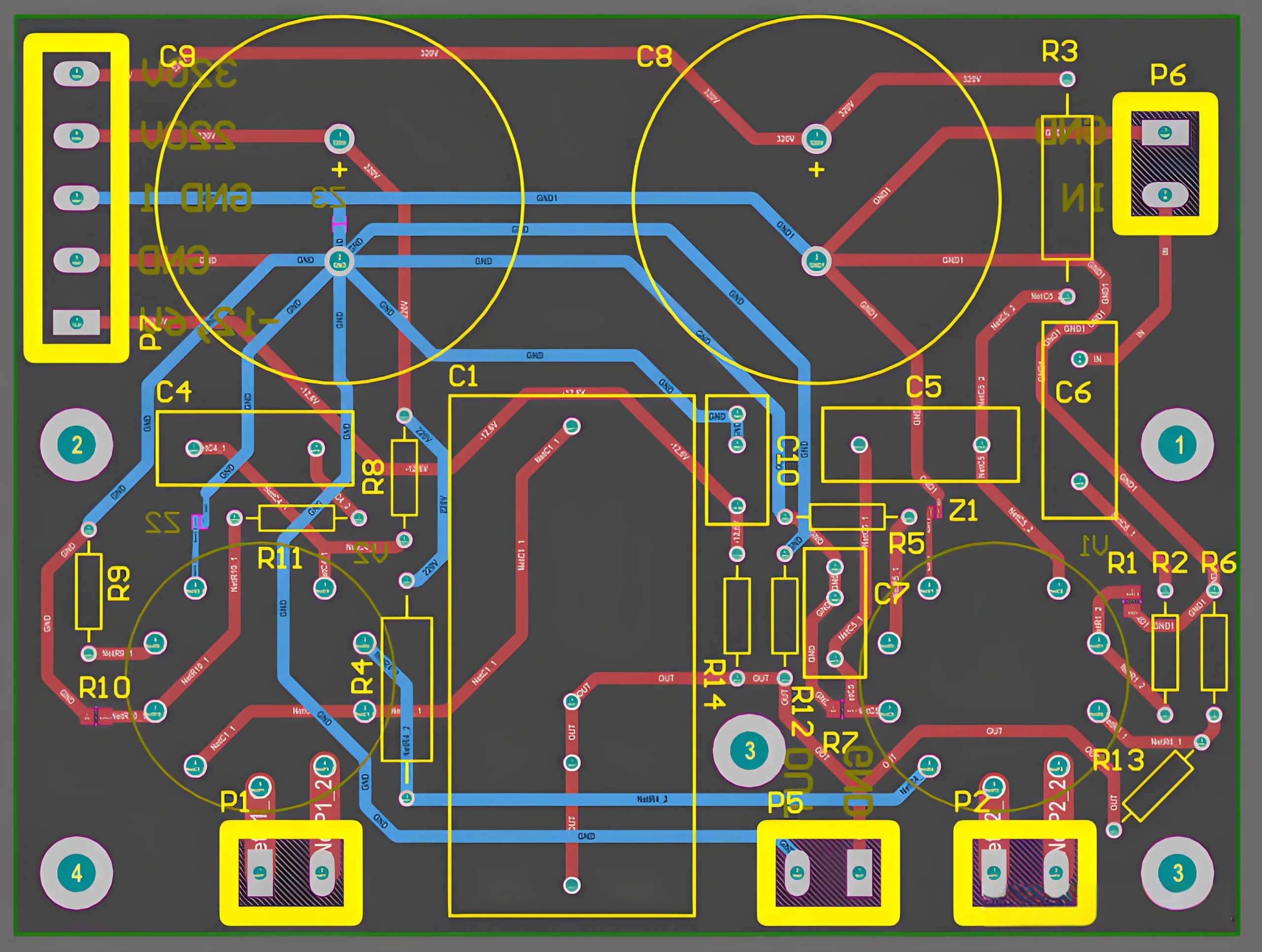

Estratégias de Aterramento: Estabelecendo Demarcação Analógico-Digital

Criticalidade de isolamento de avião

A sobreposição de planos de aterramento digitais/analógicos cria canais de ruído capacitivos:

C_coupling = (ε * A_overlap) / d

Mesmo sobreposição de 0,1 mm² em placas de 1,6 mm gera capacitância de acoplamento de 0,3 pF – o suficiente para injetar ruído de clock de 100 MHz em sinais analógicos de nível μV.

Princípio de aterramento estelar

O aterramento de ponto único elimina matematicamente os loops de aterramento:

V_noise = -dΦ/dt = -2πf * B * A

Onde B = densidade de fluxo magnético, UM = área do laço. A convergência de caminhos em um ponto minimiza a área do loop.

Mascaramento de frequência de componente: Quando os resistores se tornam indutores

Parasitas Resistivos

0805 resistores de filme contêm indutância parasita ≈2nH. A 100 MHz:

X_L = 2πfL = 1.26Ω

Excedendo os valores típicos de resistência, alterando fundamentalmente o comportamento do circuito.

Armadilha de auto-ressonância capacitiva

A impedância do capacitor segue:

|Z| = √[R_ESR² + (X_L - X_C)²]

Capacitores de tântalo padrão de 10μF ressoam automaticamente a 300kHz, superado por cerâmica de 0,1μF a 10MHz:

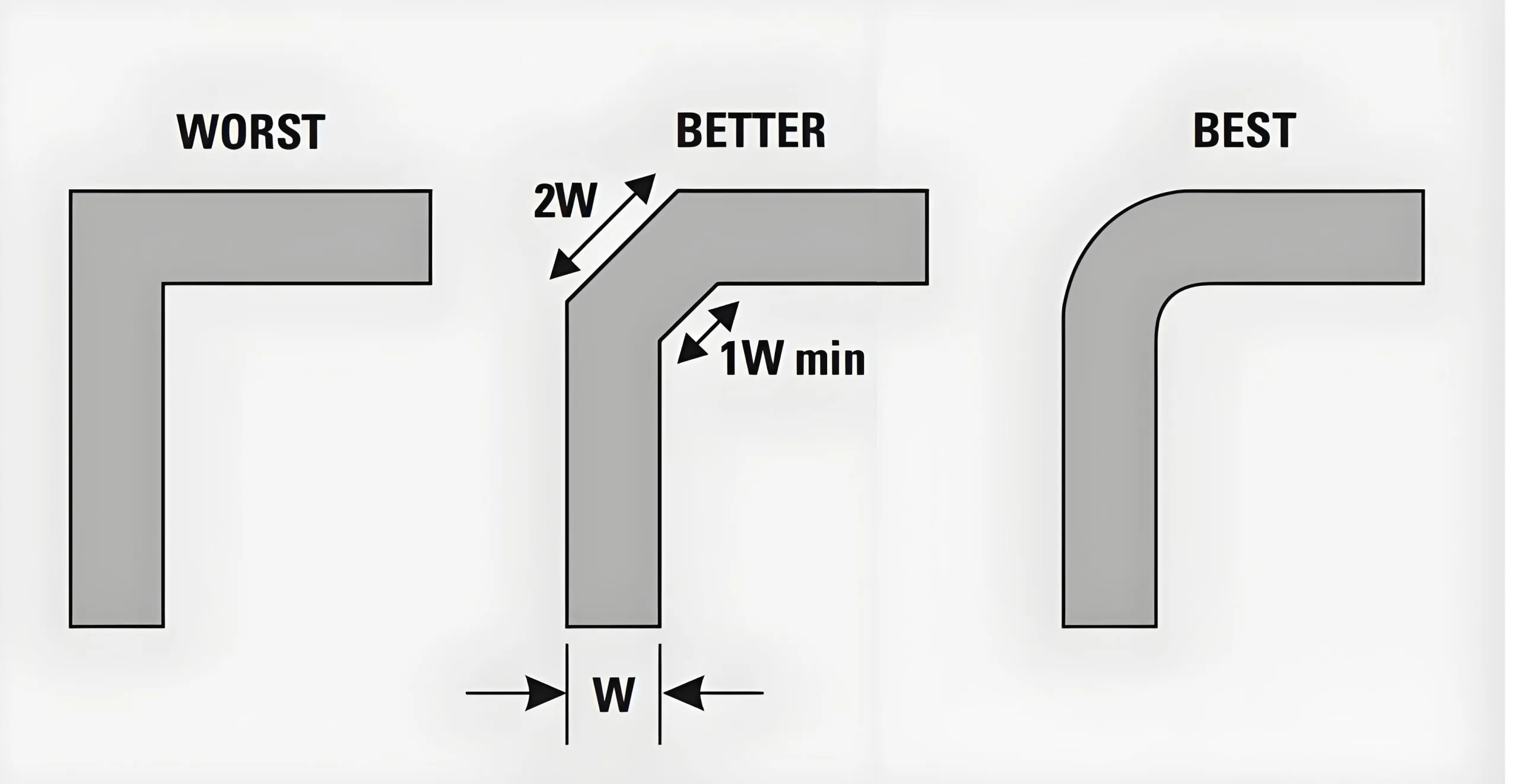

Geometria de roteamento: A catástrofe EM da curva de 90°

Traços em ângulo reto atuam como antenas ocultas em alta velocidade Layouts de PCB:

-

Aumente efetivamente o comprimento do traço 26%

-

A capacitância de canto causa descontinuidades de impedância

-

Irradie 30dB com mais eficiência do que curvas de 45°

Vias apresentam perigos iguais. Uma indutância parasita de via de 0,3 mm:

L ≈ 5.08h [ln(4h/d) + 1] (pH)

Onde *h* = espessura da placa (milímetros), *d* = diâmetro do furo (milímetros). Em 1 GHz, via única na placa de 1,6 mm gera reatância de 1,6Ω.

Defesas Finais: Da nanolimpeza aos gabinetes Faraday

Controle de Contaminação Iônica

Nós de alta impedância requerem resíduo iônico abaixo:

<1.56 μg/cm² (IPC J-STD-001 Class 3)

A limpeza ultrassônica com água DI alcança <0.3μg/cm².

Eficácia da blindagem EMI

O desempenho da gaiola de Faraday segue:

SE(dB) = 20log[(Z_0)/(4Z_s)] + 20log(e^(t/δ))

Onde d = profundidade da pele. 1mm de alumínio fornece atenuação de 120dB a 1GHz, mas lacunas de 0,1 mm degradam isso para 30dB.

A revelação do arquiteto invisível

Os dados revelam uma verdade surpreendente: 68%+ falhas de circuito originam-se de falhas de projeto de PCB. Uma vez vistos como meros portadores de componentes, Os PCBs são na verdade arquitetos de sistemas de missão crítica.

Em circuitos de 10 GHz:

-

A perda dielétrica do FR-4 pode consumir energia de sinal de 15dB

-

0.5mm de saltos no solo induzem um salto no solo de 300mV

-

Resíduos microscópicos de fluxo criam caminhos de vazamento

A revolução do design começa com a mudança de paradigma: Reclassificar PCBs de itens de custo para principais elementos funcionais. Ao preparar seu próximo amplificador operacional:

-

Essa melhoria de ruído de 0,1 dB reside nos valores Dk do laminado

-

Essas margens de temporização de 3ps residem na espessura do plano terrestre

Eleve isso “arquiteto invisível” dos bastidores ao centro do palco, e seus circuitos analógicos quebrarão barreiras de desempenho.

LOGOTIPO UGPCB

LOGOTIPO UGPCB