Os chips semicondutores servem como “cérebros” da era digital, enquanto a embalagem de chips atua como proteção “armadura” e “rede neural.” Além de proteger matrizes de silício frágeis, permite gerenciamento térmico crítico, conectividade elétrica, e transmissão de sinal. Desde pacotes volumosos até soluções ultrafinas em nível de wafer, a evolução das embalagens impulsionou a miniaturização dos eletrônicos e a melhoria do desempenho – uma saga tecnológica monumental.

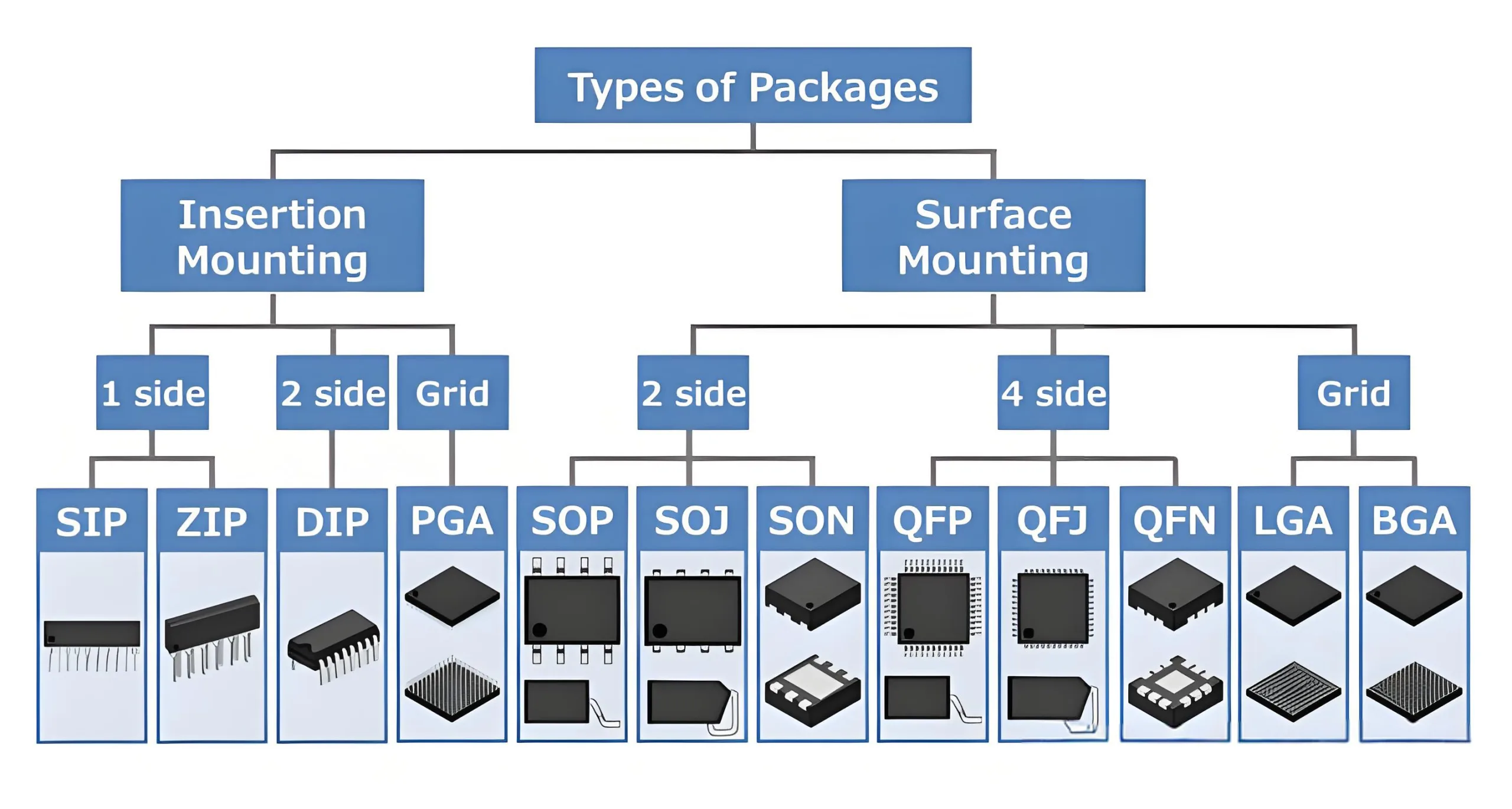

Classificação de tecnologias de embalagem

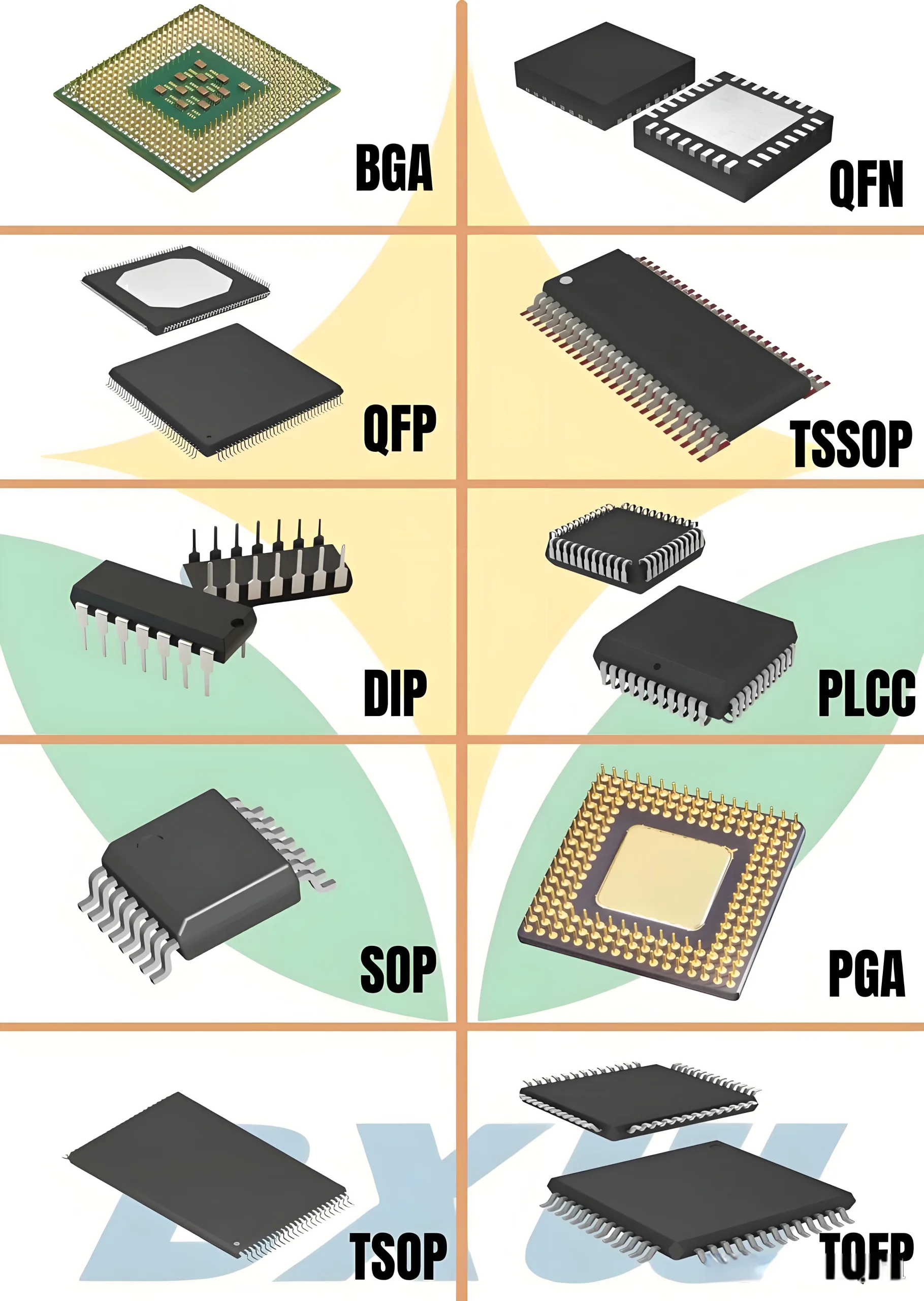

Por método de montagem

-

Embalagem passante (THT):

Pinos inseridos em PCB furos passantes banhados para soldagem. Representa tecnologia de primeira geração. -

Tecnologia de montagem em superfície (SMT):

Componentes soldados diretamente em placas de PCB. Permite maior densidade e montagem automatizada.

Por configuração de pino (Progressão de densidade)

Linha única → Linha dupla → Quad lado → Matriz de área

A era do buraco passante

FAZER/FAZER: Fundações de componentes discretos

-

Diodo DO-41: Ø2,7 mm × 5,2 mm

-

Transistor TO-220: Lida com dissipação de energia ≤50W

-

Resistência Térmica: R<sub>e</sub> = (T<sub>j</sub> – T<sub>um</sub>)/P

Onde R<sub>e</sub> = resistência térmica da junção ao ambiente

SIP/ZIP: Inovações em linha única

-

SIP: 3-16 pinos, econômico para resistores/diodos de baixa potência

-

CEP: 40% maior densidade de pinos do que SIP por meio de arranjo de pinos em zigue-zague

-

Aplicações: Módulos de memória iniciais, reguladores de tensão

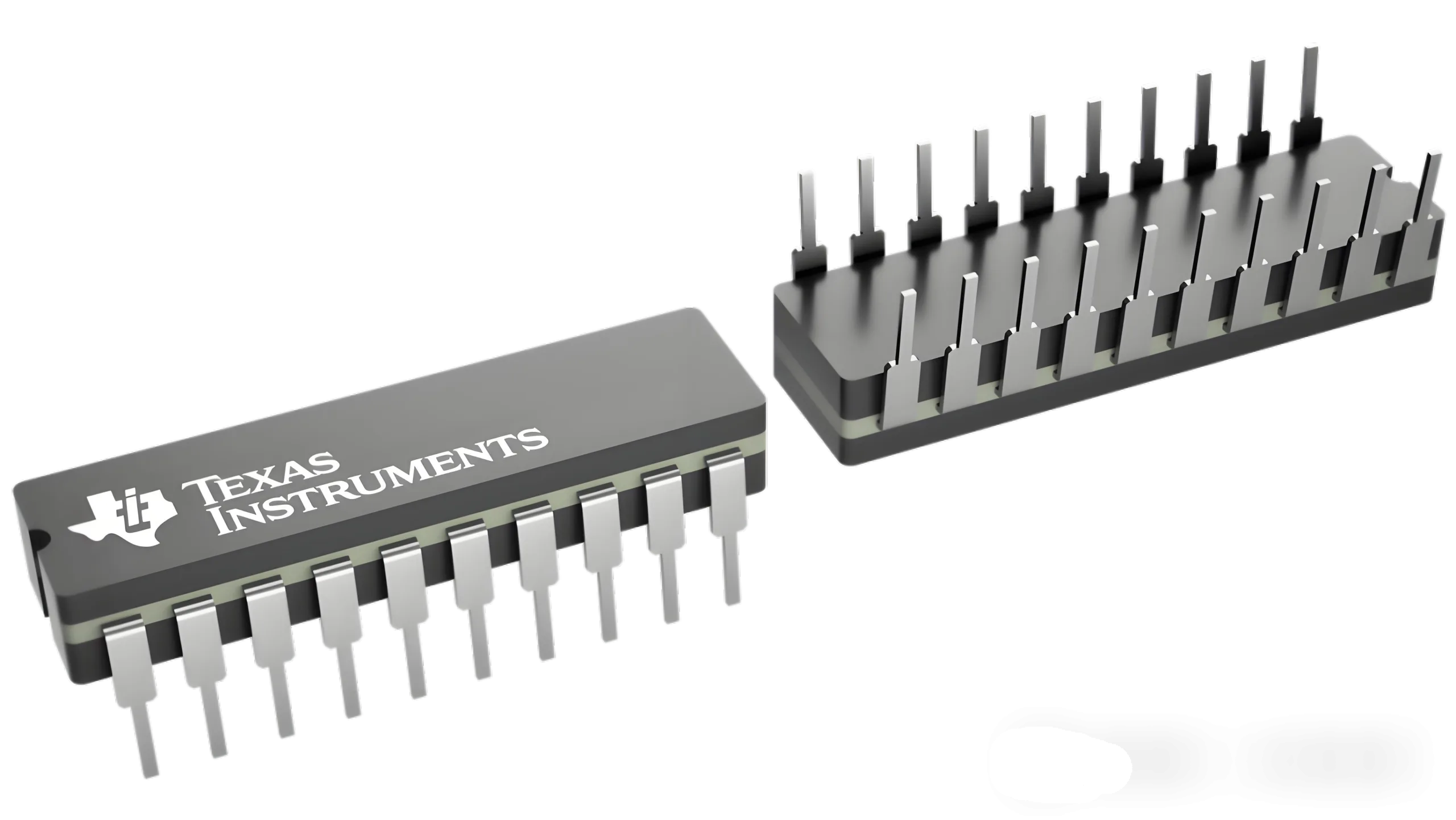

MERGULHAR: A Revolução CI

-

Passo do pino: 2.54milímetros (0.1″) padrão

-

1980s Participação de mercado: >70% de embalagens IC

-

Desempenho térmico:

DIP cerâmico: 20-30 Condutividade W/m·K

DIP de plástico: 0.2-0.3 W/m · k

PGA: Pioneiro em computação de alto desempenho

-

Densidade do pino: 3× maior que DIP

-

Aplicações: Informações 80386/80486 CPUs

-

Força de Inserção: 30-100 Newtons

A Revolução SMT

SOD/SOT: Miniaturização de componentes discretos

-

SOD-323: 1.7mm × 1,25 mm

-

Resistência Térmica SOT-23: ~250°C/W

-

Perfil de refluxo: Temperatura máxima 235-245°C

Guias de asa de gaivota: Família POP

-

Evolução do passo dos pinos:

1.27milímetros (POP) → 0,8 mm (SSOP) → 0,65 mm (TSSOP) -

Pacotes Derivativos:

SOP → SSOP → TSOP → TSSOP → VSSOP -

Aprimoramento Térmico: HSSOP reduz a resistência térmica em 40%

Configuração J-Lead: SOJ

-

Força mecânica: 30% maior resistência ao estresse

-

Limitação Elétrica: 0.8-1.2indutância parasita nH

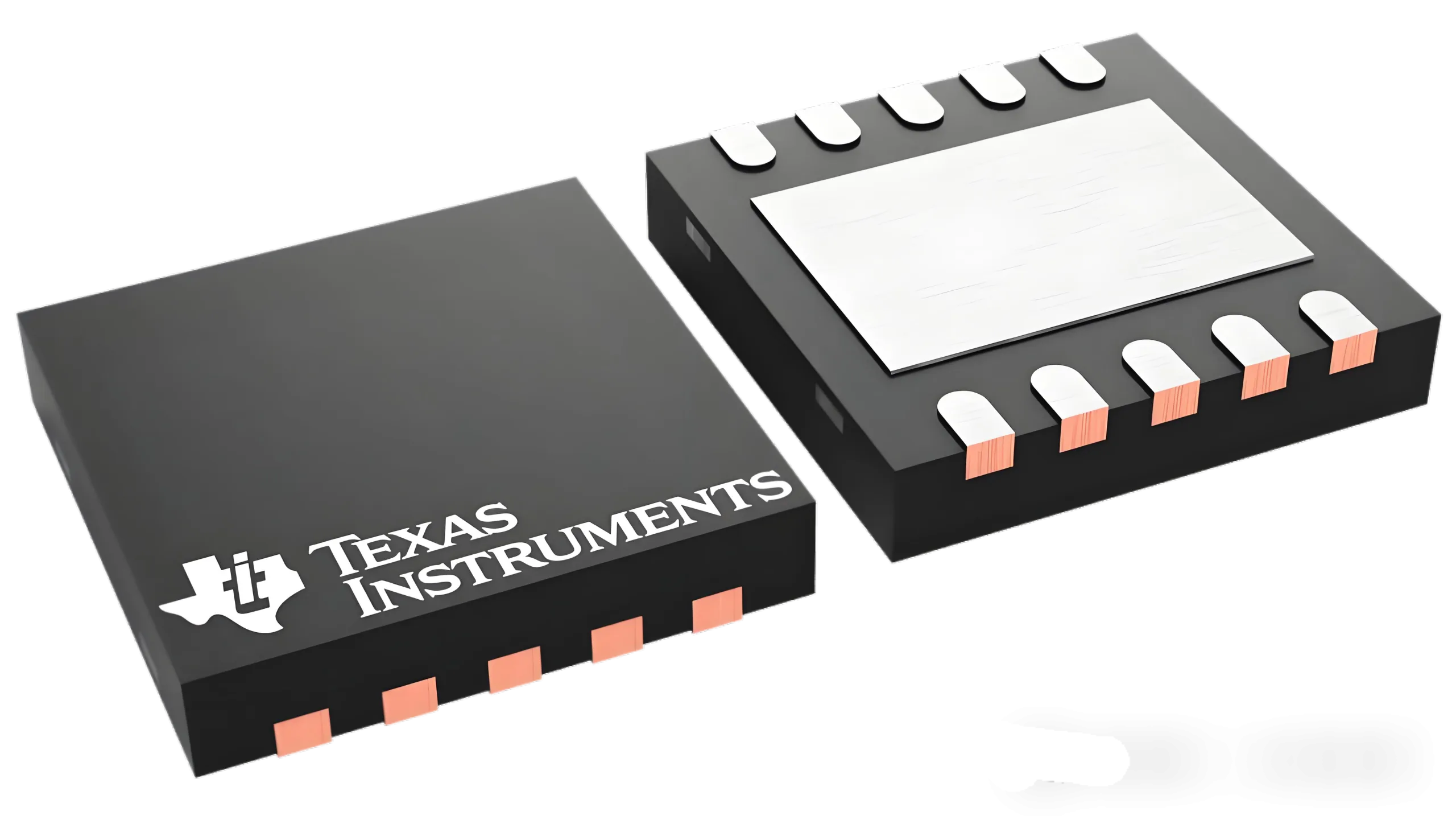

Avanço sem chumbo: FILHO/DFN

-

Eficiência Espacial: >50% melhoria em relação ao SOP

-

Desempenho térmico: 15°C/W com almofadas térmicas

-

Limite de miniaturização:

X2SON: 0.6mm × 0,6 mm × 0,32 mm

Física por trás da miniaturização

Três desafios principais governam o dimensionamento dos pacotes:

-

Gerenciamento térmico:

Q = hAΔT

Tamanho reduzido (↓A) exige maior coeficiente de convecção (↑h) -

Controle de estresse térmico:

σ = EαΔT

Onde CTE (um) incompatibilidade induz estresse -

Integridade do sinal:

Indutância de chumbo *L ≈ 2l(ln(2eu/d)-1) nH*

A miniaturização reduz a indutância em 30%

Próxima Fronteira: Embalagem Avançada

À medida que o X2SON atinge escalas de 0,6 mm, a inovação muda para:

-

3Pacote D.: Integração vertical habilitada para TSV

-

Integração heterogênea: Montagem de matriz de vários nós

-

Fotônica: Co-projeto de fotônica de silício

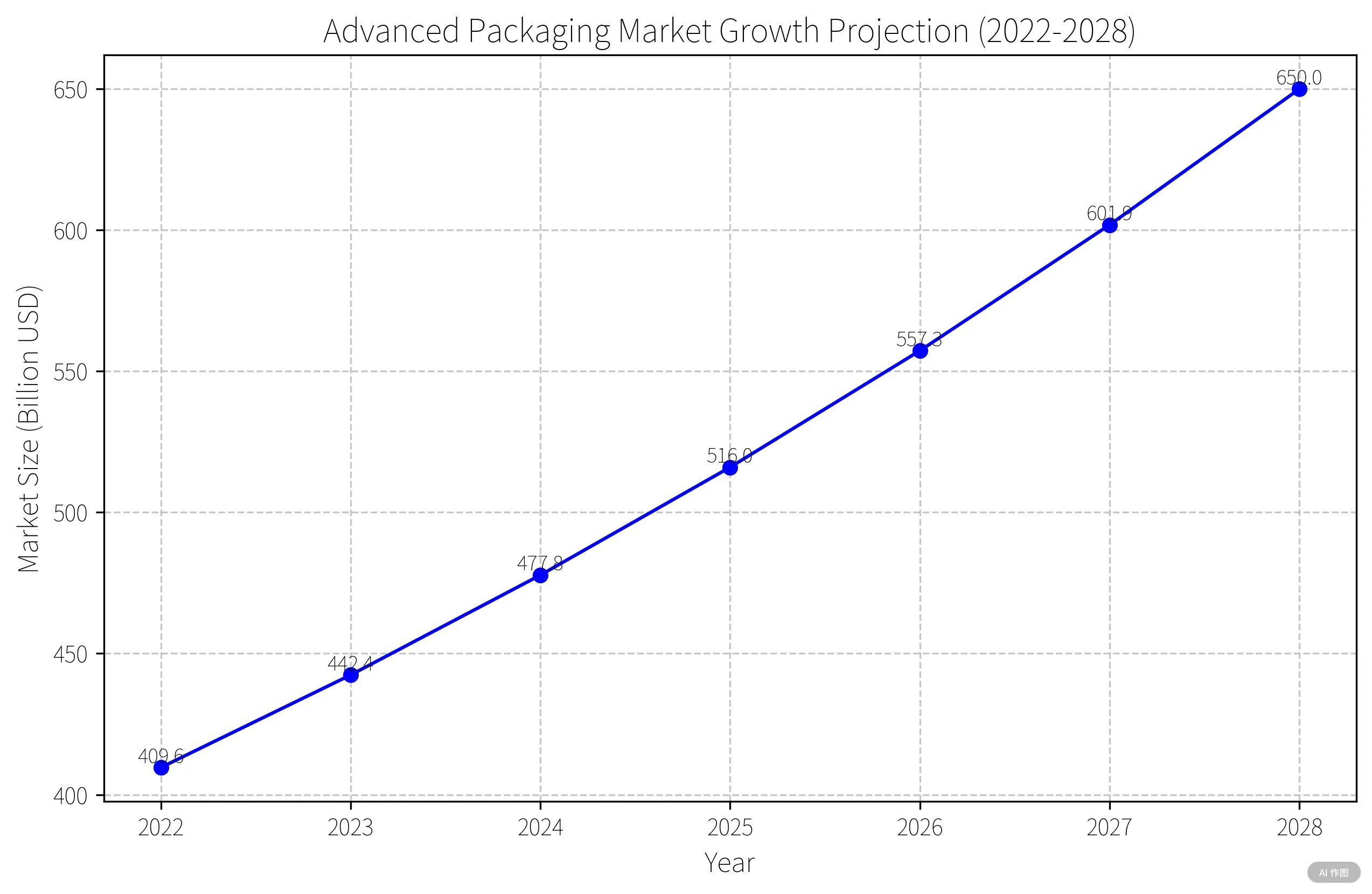

Previsão de mercado (Desenvolvimento Yole):

8% CAGR através 2028 → Mercado de US$ 65 bilhões

A embalagem agora define criticamente o desempenho do sistema – muito além da mera proteção.

Conclusão

Do passo de 2,54 mm do DIP à pegada de 0,6 mm do X2SON, os avanços nas embalagens redefinem continuamente a eletrônica. Cada smartphone fino e dispositivo 5G depende dessas inovações invisíveis. Com o surgimento da IA e da computação quântica, embalagens de chips continuarão ultrapassando os limites da nanoescala.

*Próximo da série:

Tecnologias BGA/CSP/WLCSP

3Pacote D. & Interconexões TSV

Ciência Avançada de Materiais de Embalagem

Fique atento!*

LOGOTIPO UGPCB

LOGOTIPO UGPCB