A técnica de cortar unidades individuais das bolachas e depois embalá -las tem sido a norma para embalar circuitos integrados semicondutores por décadas. No entanto, esta abordagem não está sendo adotada atualmente pelos principais fabricantes de semicondutores devido aos altos custos de fabricação e ao crescente componente de RF dos módulos atuais. Por isso, o surgimento de embalagens em nível de wafer (WLP) levou a uma mudança de paradigma no desenvolvimento de embalagens de baixo custo. WLP é uma tecnologia de embalagem em nível de wafer antes do corte de dispositivos de embalagem de wafer.

Usando ferramentas e processos padrão, WLP atua como uma extensão do processo de fabricação de wafer. Eventualmente, o WLP DIE fabricado terá uma almofada metalizada na superfície do chip e um ponto de solda depositado em cada almofada antes de cortar o wafer. Esse, por sua vez, torna o WLP compatível com processos tradicionais de montagem de PCB e permite testes de dispositivos no próprio wafer. Como resultado, é um processo relativamente barato e eficiente, especialmente à medida que o tamanho do wafer aumenta e o chip DIE encolhe. O tamanho dos wafers tem aumentado nas últimas décadas, de 4, 6, e 8 polegadas de diâmetro para 12 polegadas. Isso resulta em um aumento no número de DIEs por wafer, o que reduz os custos de fabricação. Em termos de desempenho elétrico, WLP é superior a outras tecnologias de embalagem, no sentido de que uma vez que um dispositivo WLP é integrado em um módulo RF denso, resulta em uma redução significativa no acoplamento parasita EM porque a interconexão entre o dispositivo e o PCB é relativamente curta, ao contrário da interconexão wire-bonded usada em alguns tipos de tecnologias CSP.

Tecnologia flip-chip de chip WLP

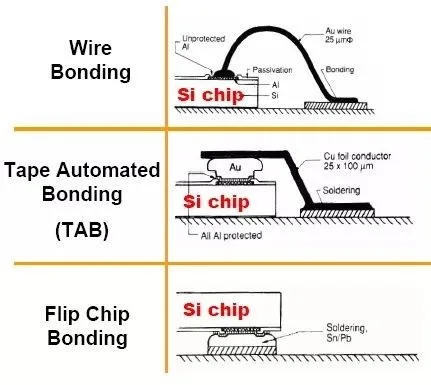

Tecnologia flip-chip, também conhecida como Conexão de Chip de Colapso Controlado (C4), é uma das várias tecnologias de montagem de chips desenvolvidas pela IBM na década de 1960. Embora a tecnologia de embalagem baseada em wire bonding seja mais flexível em termos de capacidade indutiva livre para depuração em laboratório após a construção do hardware, e também fornece boa condutividade térmica, o uso de protuberâncias de solda na tecnologia de embalagem flip-chip faz com que a conexão elétrica entre o substrato da embalagem e o chip proporcione redução relativa de tamanho, latência reduzida, e melhor isolamento em termos de pinos de entrada e saída. Figura 1 ilustra a estrutura básica do chip DIE no substrato, com uma bola de solda no topo da coluna de Cu crescendo na superfície do chip. A junta de solda geralmente é encapsulada com um composto de molde de enchimento para fornecer suporte mecânico para a junta de solda..

Tecnologia flip-chip de chip WLP

Pacote de nível de chip WLP

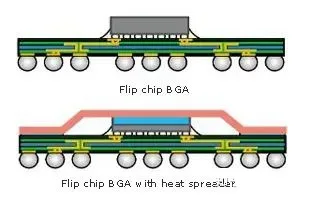

Embalagem em escala de chips (Csp) é um dos métodos de embalagem mais comumente usados na indústria de microeletrônica e semicondutores. Embora vários tipos de tecnologias CSP já estejam disponíveis para fabricantes de microchips, novos tipos continuam a surgir para atender à demanda por produtos que suportem novos recursos e novos produtos específicos para aplicações. Esses requisitos de embalagem podem variar dependendo do nível de confiabilidade exigido, custo, recursos adicionais, e tamanho total. Como o nome indica, o tamanho do pacote do CSP é aproximadamente igual ao tamanho do chip DIE, que é uma de suas principais vantagens. Ao adotar o processo de fabricação WLP, O CSP está sendo constantemente desenvolvido para atingir a menor proporção possível de tamanho de embalagem e matriz. Como mostrado na Figura 2, a matriz de grade de bola (BGA) O estilo de CSP no pacote permite diversas interconexões enquanto simplifica a fiação da PCB, aumentando o rendimento da montagem de PCB e reduzindo os custos de fabricação.

Embalagem de nível de wafer

Outras tecnologias de encapsulamento

Existem várias outras formas de empacotamento IC integrado que permitem integração perfeita em pacotes de módulos personalizados para aplicações. Pacote Quad Flat (Mf) é uma das primeiras tecnologias de pacote IC de montagem em superfície,onde a estrutura do pacote é composta por quatro lados com cabos de interconexão estendidos, como mostrado na Figura 3(um). Os condutores elevados são conectados à estrutura da embalagem para formar um metal-isolante-metal (MIM) tipo capacitor entre os terminais e o chip DIE metal, que pode ser usado como um elemento correspondente. Esta técnica é adequada para CIs de tamanho milimétrico, onde o número de pinos periféricos no pacote pode atingir mais de 100 pinos. Existem vários derivados deste tipo de encapsulamento, dependendo do material usado, como pacote plano quádruplo de cerâmica, pacote plano quádruplo fino, pacote plano quádruplo de plástico, Pacote plano quádruplo de plástico) e pacote plano quádruplo de metal (MQFP). O QFN, Quad Flat sem chumbo, mostrado na Fig.. 3(b) é uma das várias tecnologias de embalagem montadas em superfície formadas a partir de uma estrutura plana de cobre e uma embalagem plástica usada como almofada de transferência de calor para o radiador. A ligação de fios também pode ser usada para interconexões, e como as linhas de ligação não são apenas condutores, mas também indutores, eles geralmente afetam o desempenho dos dispositivos sob esta técnica de encapsulamento, a menos que seja considerado como parte do projeto geral. Embora o QFN seja uma interconexão composta por quatro lados, o biplano não conduzido conduz (DFN) também apareceram e formam ambos os lados dos condutores do plano de interconexão.

LOGOTIPO UGPCB

LOGOTIPO UGPCB