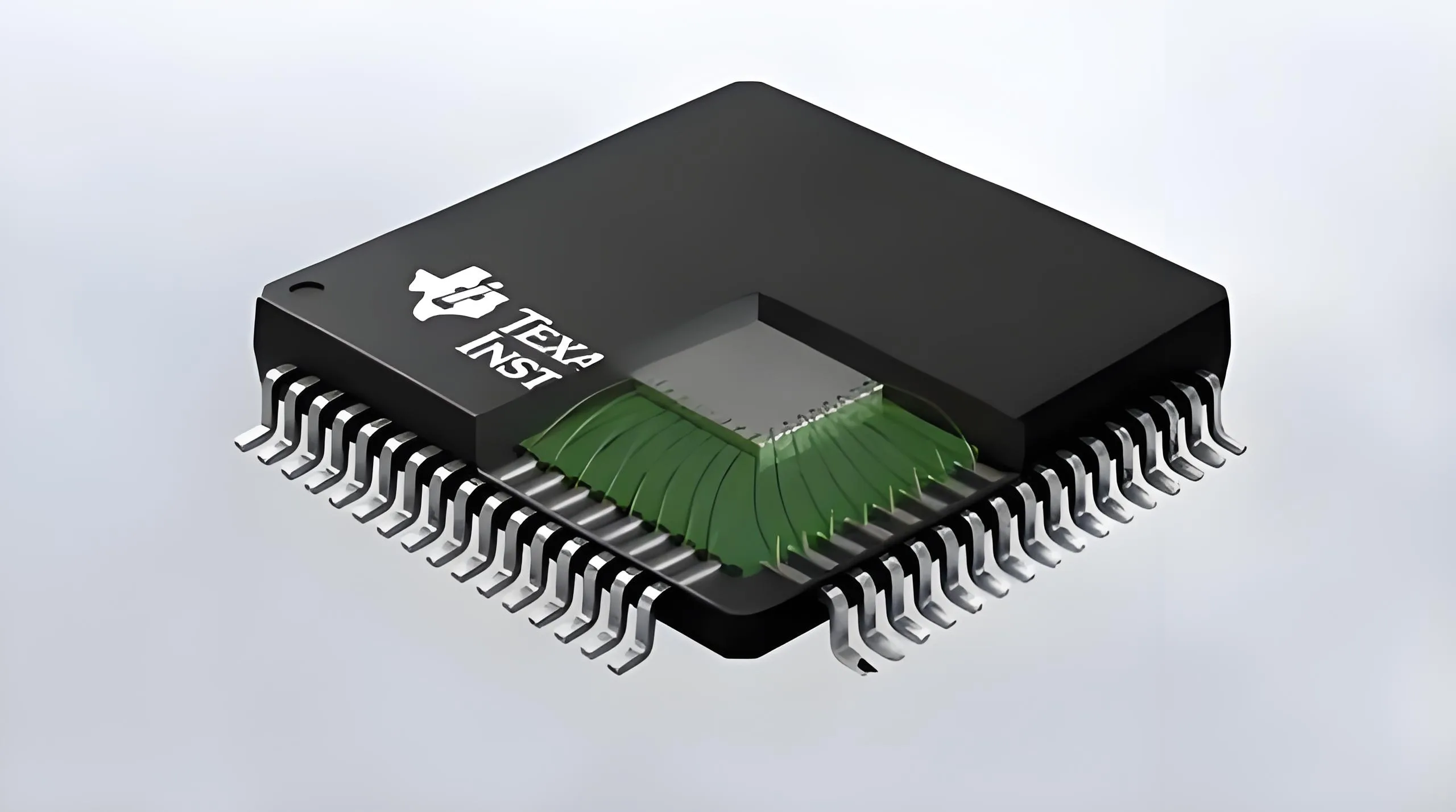

embalaje

IC PCB & Embalaje- Cuando se habla del futuro de la tecnología portátil, El curso futuro de la innovación de tecnología portátil es claro. Es ruidoso y claro que para tener éxito, La electrónica portátil debe ser pequeña y seguir funcionando. Este artículo se centra en los requisitos para la oblea – chip de nivel – Embalaje de nivel en SRAM .

Para reducir la huella, y así el espacio general de la placa, Los microcontroladores migran a nodos de proceso más pequeños cada otra generación. Al mismo tiempo, están evolucionando para realizar operaciones más complejas y poderosas.. A medida que las operaciones se vuelven más complejas, Hay una necesidad urgente de aumentar el almacenamiento en caché. Desafortunadamente, con cada nuevo nodo de proceso, Agregar caché integrado (Sram incrustado) se vuelve desafiante por varias razones, incluyendo más alto ser, menor rendimiento, y mayor consumo de energía. Los clientes también tienen requisitos personalizados de SRAM. Para que los fabricantes de MCU proporcionen todos los tamaños de caché posibles requerirían que tengan una cartera de productos que sea demasiado grande para administrar. Esto ha impulsado la necesidad de limitar el SRAM integrado en el núcleo del controlador y almacenarlo en caché a través de un SRAM externo.

Sin embargo, Dado que SRAM externo ocupa una gran cantidad de espacio de placa PCB, El uso de SRAM externo enfrenta el desafío de la miniaturización. Debido a su arquitectura de seis transistores, Reducir el tamaño del SRAM externo al portar el SRAM externo a un nodo de proceso más pequeño introducirá los mismos problemas que han plagado el SRAM incrustado miniaturizado.

Esto nos lleva a la próxima alternativa a este antiguo problema.: Reducción de la relación de envasado de chip al tamaño del chip en el SRAM externo. Típicamente, Las chips Sram empaquetadas son muchas veces el tamaño del chip desnudo (arriba a 10 veces). Una solución común a este problema es no usar chips SRAM encapsulados en absoluto. Tiene sentido tomar un chip sram (1/10 tamaño) y luego empaquételo con un chip MCU usando envases complejos de múltiples chips (MCP) o tecnología de embalaje 3D (También conocido como empaque de nivel de sistema SIP). Pero este enfoque requiere una inversión significativa y solo es factible para los fabricantes más grandes. Desde una perspectiva de diseño, Esto también reduce la flexibilidad porque los componentes en SIP no se reemplazan fácilmente. Por ejemplo, Si la nueva tecnología SRAM está disponible, No podemos reemplazar fácilmente el chip SRAM en SIP. Para reemplazar cualquiera de las chips desnudas en el paquete, Todo el SIP debe ser reautenticado. Recalificación requiere reinversión y más tiempo.

Entonces, ¿hay alguna manera de ahorrar espacio en la mesa mientras excluye el SRAM del MCU sin poner en problemas al MCP? Volviendo a la relación de tamaño de núcleo a chip, Vemos espacio para una mejora significativa. ¿Por qué no verifica si hay un paquete que se ajusta al molde?? En otras palabras, Si no puedes desempacar, Reduce la escala de tamaño.

Actualmente, el enfoque más avanzado es reducir el tamaño del paquete de chips utilizando WLCSP (Paquete de nivel de chip de nivel de obleas). WLCSP se refiere a la tecnología de cortar unidades individuales de una oblea en piezas pequeñas y luego ensamblarlas en un paquete. El dispositivo es esencialmente un chip desnudo con un punto elevado o un patrón de matriz esférico que no requiere ninguna línea de unión o conexiones de capa intermedia. Dependiendo de las especificaciones, El área de un paquete de nivel de chip está a la altura 20% más grande que el del chip. El proceso ahora ha alcanzado un nivel innovador en el que las plantas de fabricación pueden producir componentes CSP sin aumentar el área de chips (con solo un ligero aumento en el grosor para adaptarse a la protuberancia/esfera).

Números. Oblea – en – embalaje (ULC) proporciona el método más avanzado para reducir el tamaño del envasado desnudo – chip. El WLCSP que se muestra aquí fue desarrollado por Deca Technologies y no aumenta el área de los chips que lo componen. (Crédito: Tecnologías DECA/ Semiconductor Cypress)

CSP tiene algunas ventajas sobre la película sin recubrimiento. Los dispositivos CSP son más fáciles de probar, manejar, armar, y reescribir. También tienen propiedades de conductividad térmica mejoradas. Cuando el núcleo se transfiere a nodos de proceso más nuevos, Es posible reducir el núcleo mientras estandariza el tamaño de CSP. Esto asegura que los componentes CSP puedan ser reemplazados por una nueva generación de componentes CSP sin ninguna complicación asociada con el cambio del molde.

Obviamente, Estos ahorros de espacio son importantes en términos de la demanda de dispositivos portátiles y electrónica portátil.. Por ejemplo, El BGA de 48 bolas utilizado en la memoria IC en muchos dispositivos portátiles hoy tiene un tamaño de 8 mmx6mmx1mm (48mm3). En comparación, La misma parte en un paquete CSP mide 3.7mmx3.8mmx0.5 mm (7mm3). En otras palabras, Puede reducir el volumen por 85%. Este ahorro se puede utilizar para reducir el área de PCB y el grosor de los dispositivos portátiles. Como resultado, la demanda de dispositivos basados en WLCSP de wearables e Internet de las cosas (IoT) Los fabricantes no se limitan a SRAM, Pero hay una nueva demanda.

UGPCB LOGO

UGPCB LOGO