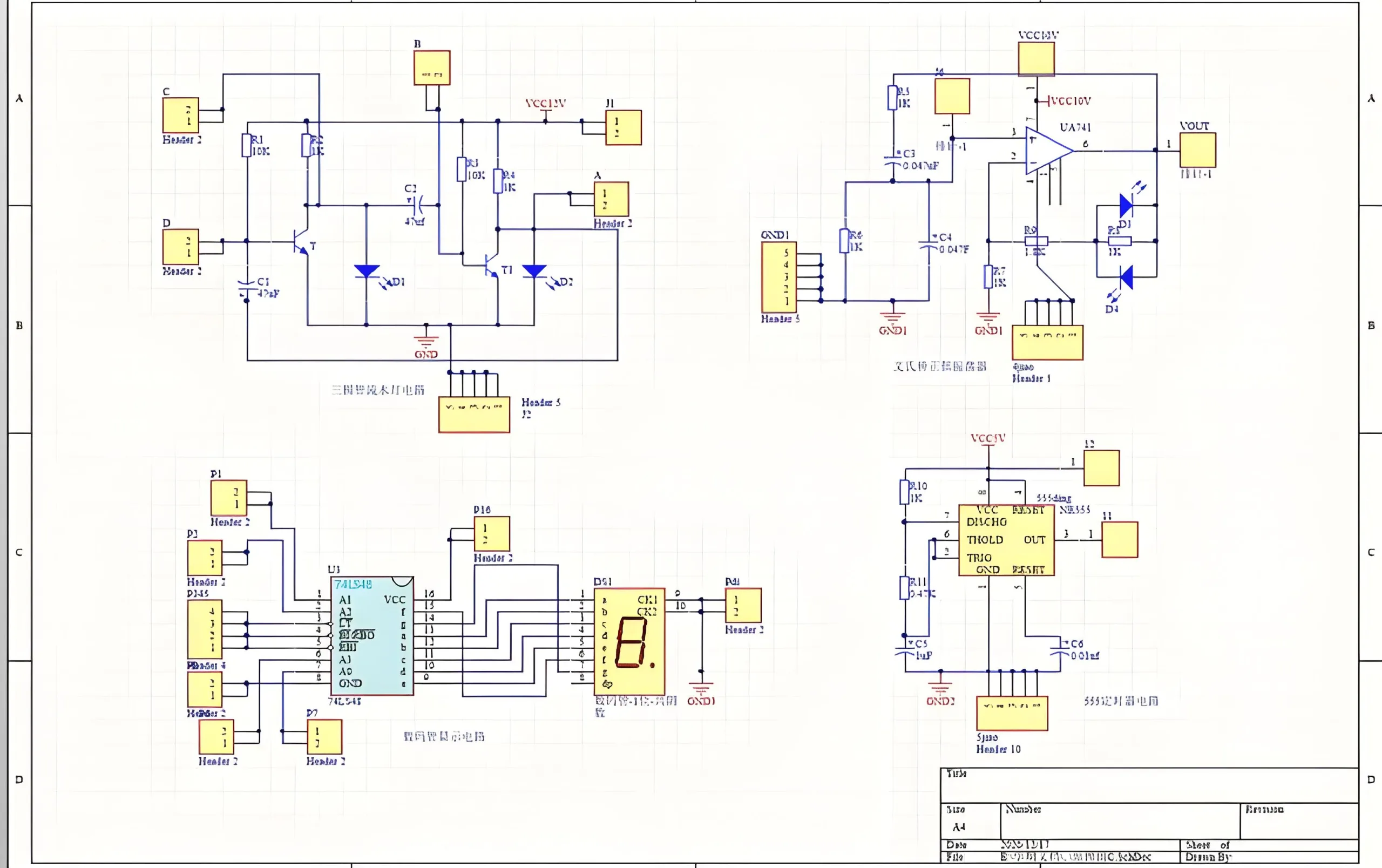

고속 디지털 회로 및 정밀 아날로그 시스템의 수렴에서, 절묘하게 디자인되었습니다 PCB 개략도 제품 생존력을 결정합니다 90% 전력 무결성 붕괴에서 비롯된 설계 실패.

엔지니어가 Altium Designer에서 37 번째 DDR4 길이 매칭 트레이스를 라우팅 할 때, 임피던스 레이어 스택에 숨겨진 불연속성 신호 무결성을 조용히 저하시키는 데 숨겨져 있습니다. UGPCB 시뮬레이션 데이터가 나타납니다: 최적화되지 않은 전원 모듈이있는 PCB가 어려움을 겪습니다 62% 실패율, 분할 평면 기술을 구현하는 디자인은 비트 오류율을 10 ¹²로 줄입니다..

회로의 본질: PCB 회로도의 핵심 원칙 & 진화

배선 다이어그램에서 지능형 시스템에 이르기까지

현대의 회로도가 진화했습니다 지능형 엔지니어링 생태계:

-

전기 신경망: 포함하다 32 설계 규칙 (추적 너비/간격/임피던스/크로스 스토크 임계 값); UGPCB의 제약 관리자가 동기화됩니다 12,000+ 네트워크

-

크로스 도메인 협력: Allegro SI 분석이 보여줍니다 ± 18ps 타이밍 마진 6 층의 중요한 경로 HDI 보드, 회로도 -PCB-Firmware 협력이 필요합니다

혁신적인 디자인 도구 발전

| 도구 생성 | 대표 소프트웨어 | 효율성 이득 | UGPCB 최적화 케이스 |

|---|---|---|---|

| 기초 디자인 | Protel99SE | 1X 기준선 | 프로젝트 마이그레이션에 대한 레거시 라이브러리 호환성 |

| 고속 디자인 | Altius 디자이너 | 3.2엑스 | 동적 길이 매칭 오류 ≤0.01mm |

| 시스템 설계 | 케이던스 앨리 그로 | 5.7엑스 | 40% 16Gbps의 안구 마진 개선 |

UGPCB 사례 연구: Orcad에서 Allegro 로의 마이그레이션은 BGA 탈출 라우팅 성공이 증가했습니다. 74% 에게 98%, 개발주기 감소 21 날.

모듈 식 디자인 방법론: 복잡한 회로 해체

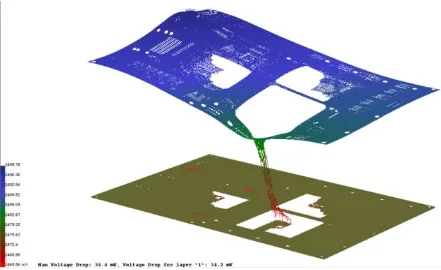

전력 무결성: 중요한 차별화 요소

토폴로지 선택 공식:

H = frac{피_{밖으로}}{피_{밖으로} + 피_{SW} + 피_{조건}} \쿼드 텍스트{(타겟팅>92\%)}

UGPCB 3D 파워 트리 분석:

-

자동차 ECU에서 전압 감소 감소 220MV에서 35MV LDO 배치 최적화

-

하이브리드 파워 평면: 분할/혼합 평면 기술은 잔물결을 감소시켰다 67%

고속 신호 경로의 정밀 제어

임피던스 제어 방정식:

UGPCB 구현:

-

차동 쌍 보상: SKEW 달성<2100G 광학 모듈에서 추신

-

EM 차폐 벽: 18DB SNR 개선 의료 PCB 디지털/아날로그 분리를 통해

산업 급 디자인: UGPCB 9 핵심 기술

3D Stackup 아키텍처 최적화

최적의 8 층 구성:

L1: 신호 (고속) L2: Solid GND L3: 신호 (스트립 라인) L4: Power L5: GND L6: Signal L7: Power L8: 신호 (저속)

확인: 12DBμV/M EMI 감소, FCC 클래스 B 인증

제조 중심 디자인 (DFM) 정도

UGPCB ± 0.025mm 공정 제어:

-

마이크로 비아 기술: 0.1MM 레이저 드릴, 12:1 종횡비

-

구리 두께: 2oz 외 층에 대한 ± 10% 에칭 공차

-

솔더 마스크 교량: 0.075MM 최소 너비는 SMT 브리징을 방지합니다

디자인을 넘어서: UGPCB의 전체 수명주기 서비스

신호 무결성 보증

디자인 단계: Hyperlynx Pre-Layout 시뮬레이션이 제거됩니다 90% 위험

검증 단계: TDR 테스트가 보장됩니다 <5% 임피던스 편차

양산: 주요 매개 변수 제어를위한 Golden Reference 데이터베이스

스마트 제조 통합

결과: 48-시간 프로토 타입 배달, 99.2% 첫 번째 통과 수익률

미래의 실험실: UGPCB의 기술 프론티어

실리콘 기질 이종 통합

2.5D TSV 개입:

-

0.3FPGA-HBM 통합을위한 MM 피치 상호 연결

-

열 저항은 0.15 ° C/W로 감소했습니다

AI 중심 EDA 혁명

Neuroroute 엔진:

-

8X 라우팅 효율 개선

-

최적화 기능:

Min(ΔL, Crosstalk, Via_Count) -

5g mmwave 안테나 어레이에 배포되었습니다 PCB 디자인

UGPCB 로고

UGPCB 로고

위챗

WeChat으로 QR 코드를 스캔하세요