반도체 칩은 “두뇌” 디지털 시대의, 칩 포장은 보호 역할을합니다 “갑옷” 그리고 “신경망.” 깨지기 쉬운 실리콘을 차폐하는 것 외에는 죽습니다, 중요한 열 관리를 가능하게합니다, 전기 연결, 및 신호 전송. 부피가 큰 통로 패키지에서 초박형 웨이퍼 레벨 솔루션에 이르기까지, 포장 진화는 전자 제품 소형화 및 성능 향상을 주도했습니다 - 기념비적 인 기술 사가.

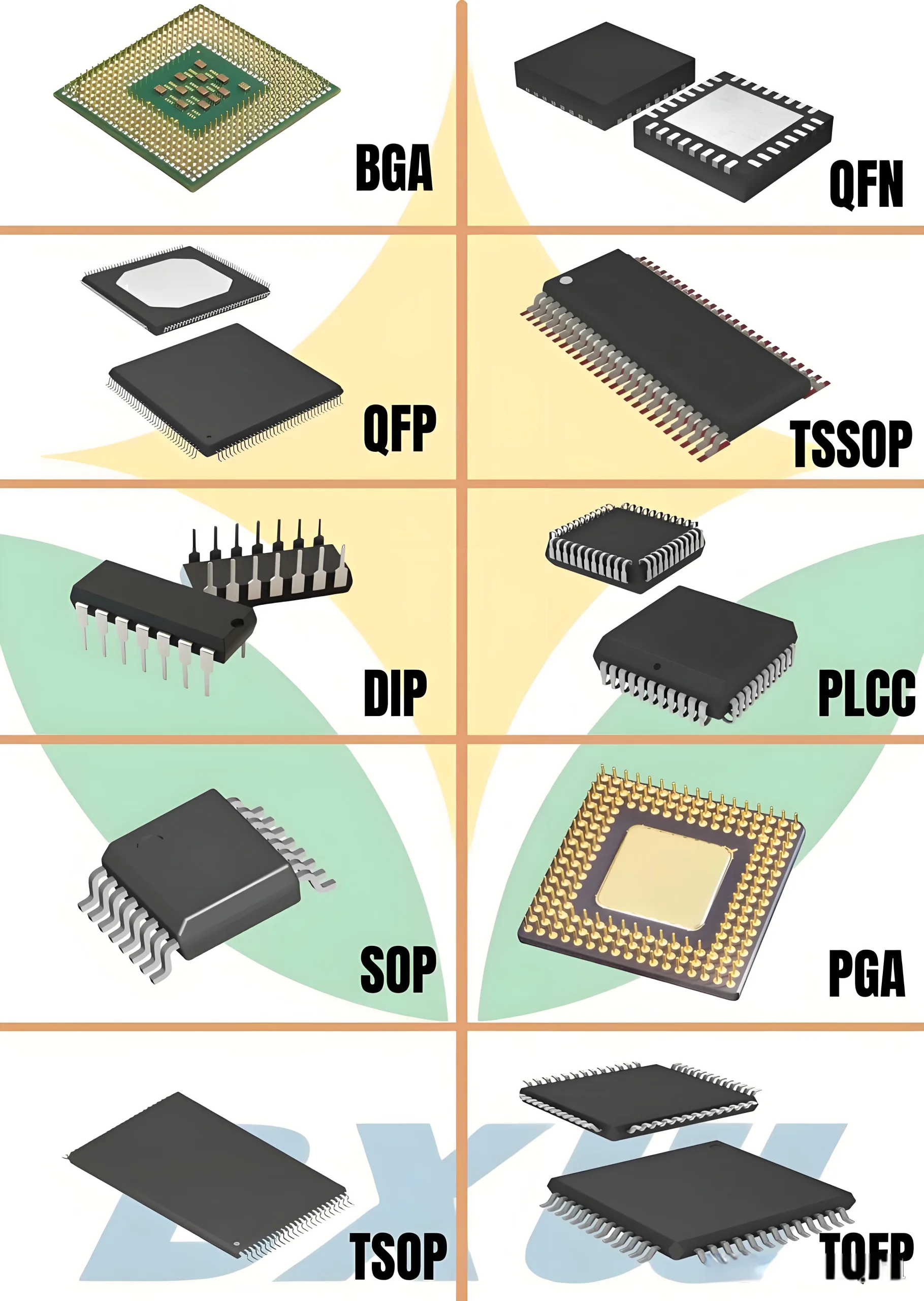

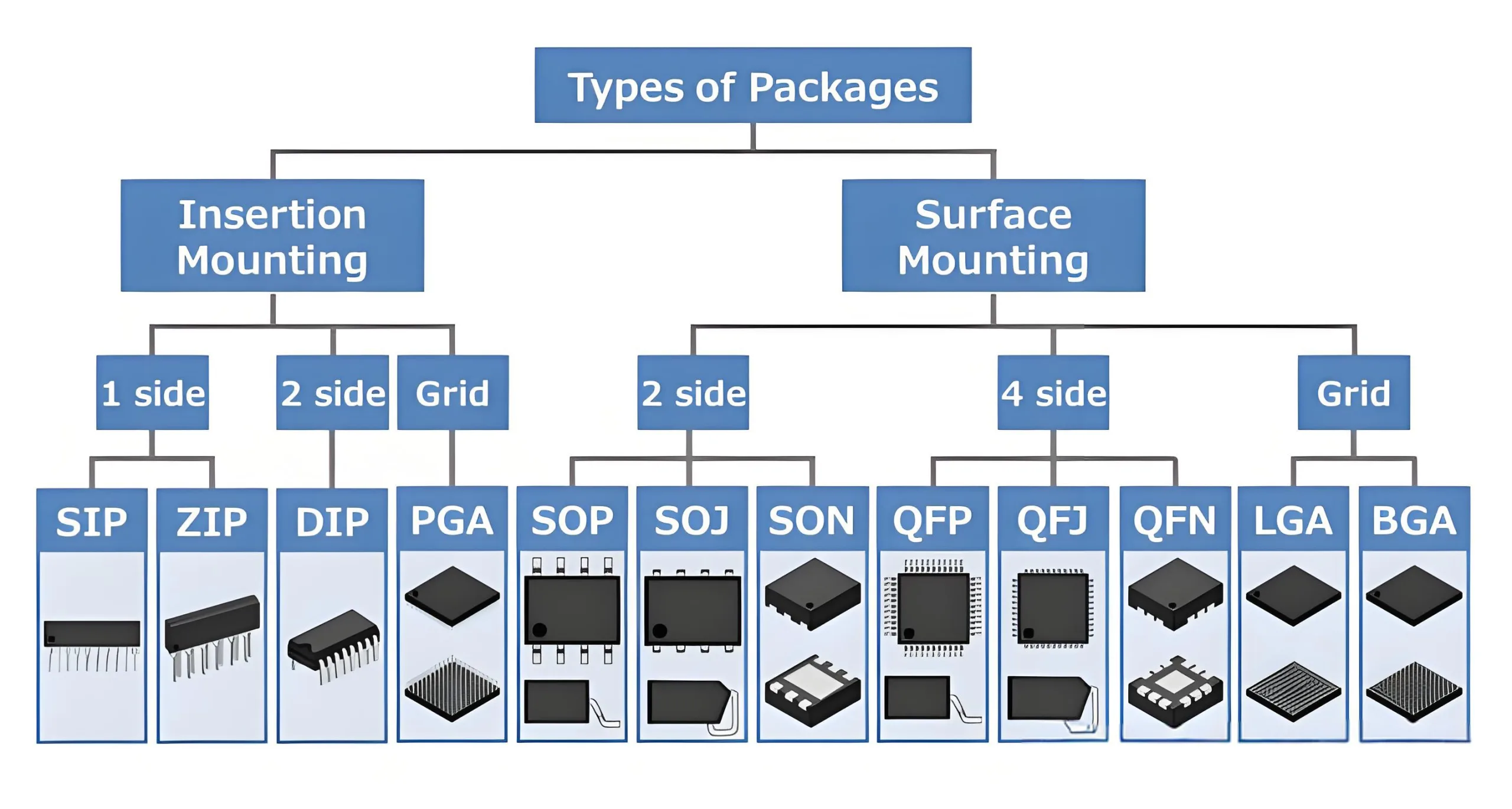

포장 기술 분류

장착 방법으로

-

구멍 포장 (tht):

핀이 삽입되었습니다 PCB 납땜을 위해 구멍을 뚫습니다. 초기 세대 기술을 나타냅니다. -

표면 마운트 기술 (SMT):

구성 요소는 PCB 패드에 직접 납땜되었습니다. 더 높은 밀도 및 자동 조립품을 가능하게합니다.

핀 구성에 의해 (밀도 진행)

싱글 로우 → 듀얼 행 → 쿼드 사이드 → 면적 배열

통과 시대

/to: 개별 구성 요소의 기초

-

DO-41 다이오드: Ø2.7mm × 5.2mm

-

TO-220 트랜지스터: ≤50W 전력 소산을 처리합니다

-

열 저항: 아르 자형<보결>그리고</보결> = (티<보결>J.</보결> – 티<보결>에이</보결>)/피

어디 아르 자형<보결>그리고</보결> = 교차로-아함형 열 저항

SIP/zip: 단일 인간 혁신

-

한모금: 3-16 다리, 저항/저전력 다이오드에 대한 비용 효율적입니다

-

지퍼: 40% 지그재그 핀 배열을 통한 SIP보다 높은 핀 밀도

-

응용: 초기 메모리 모듈, 전압 조정기

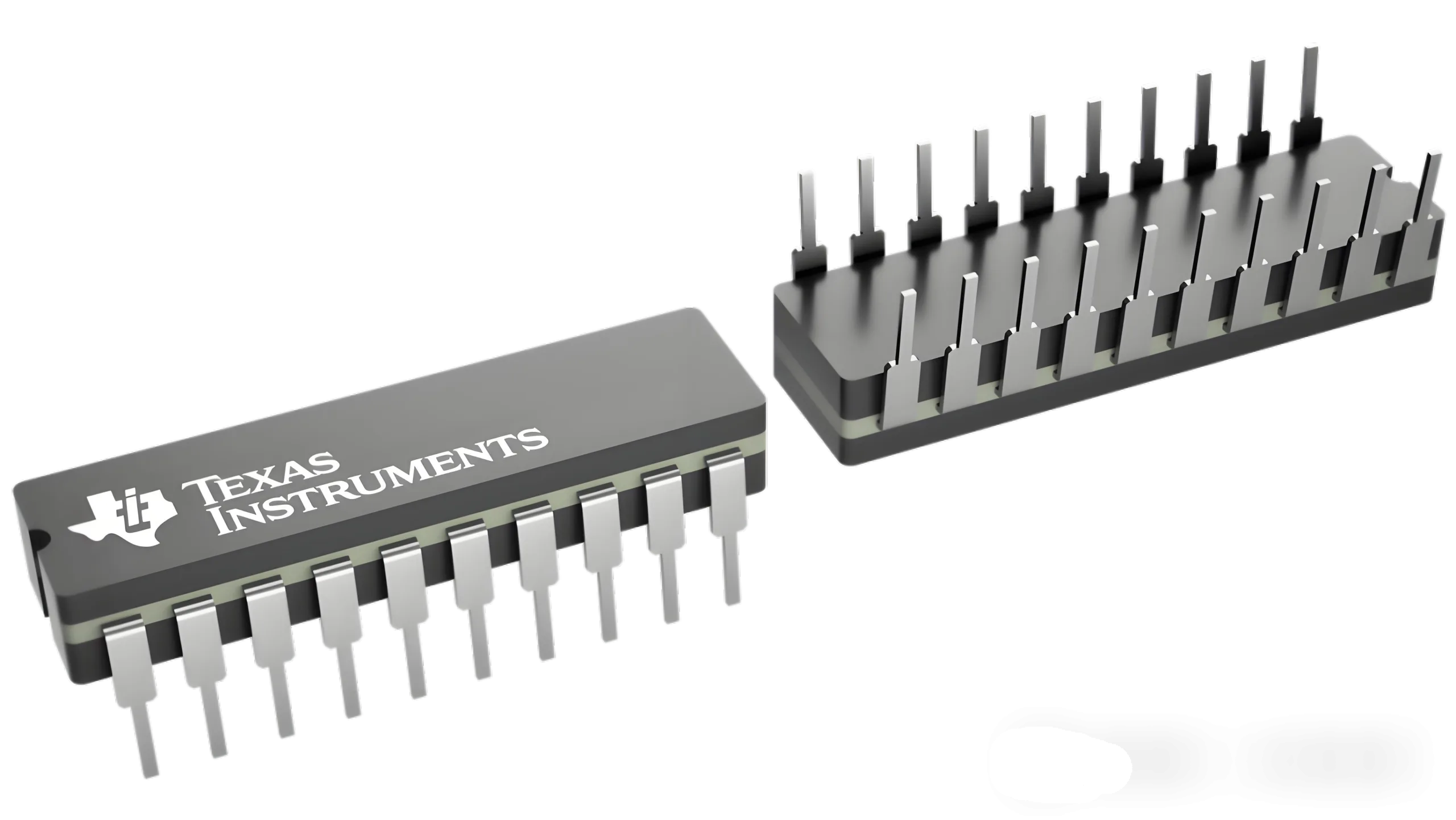

담그다: IC 혁명

-

핀 피치: 2.54mm (0.1″) 기준

-

1980S 시장 점유율: >70% IC 포장

-

열 성능:

세라믹 딥: 20-30 w/m · K 전도도

플라스틱 딥: 0.2-0.3 w/m · k

PGA: 고성능 컴퓨팅 개척자

-

핀 밀도: 3× 딥보다 높습니다

-

응용: 인텔 80386/80486 CPU

-

삽입력: 30-100 뉴턴

SMT 혁명

잔디/소트: 불연속 구성 요소 소형화

-

SOD-323: 1.7mm × 1.25mm

-

SOT-23 열 저항: ~ 250 ° C/W.

-

리플 로우 프로파일: 피크 온도 235-245 ° C

gull-wing 리드: SOP 가족

-

핀 피치 진화:

1.27mm (예규) → 0.8mm (SSOP) → 0.65mm (TSSOP) -

파생 패키지:

SOP → SSOP → TSOP → TSSOP → vssop -

열 향상: HSSOP는 열 저항을 줄입니다 40%

J-LEAD 구성: 관찰

-

기계적 강도: 30% 스트레스 저항이 높아집니다

-

전기 제한: 0.8-1.2NH 기생 인덕턴스

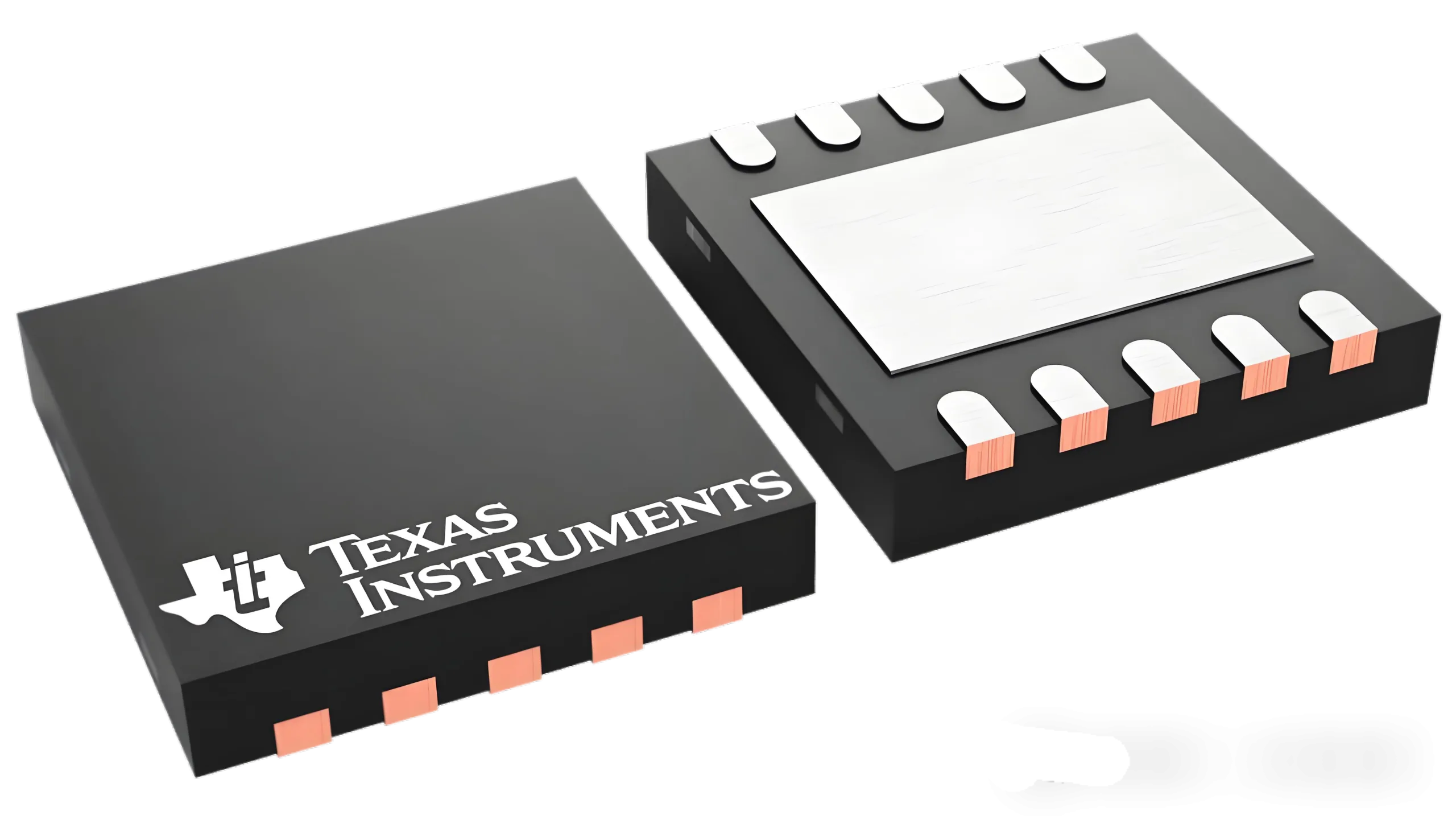

리드 한 획기적인 획기적인: 아들/dfn

-

공간 효율: >50% SOP보다 개선

-

열 성능: 15열 패드가있는 ° C/W

-

소형화 한도:

X2SON: 0.6mm × 0.6mm × 0.32mm

소형화의 물리학

세 가지 핵심 과제는 패키지 스케일링을 관리합니다:

-

열 관리:

q = haΔt

크기 감소 (↓ a) 더 높은 대류 계수가 필요합니다 (↑ h) -

열 응력 제어:

s = ertht

여기서 CTE (에이) 불일치는 스트레스를 유발합니다 -

신호 무결성:

리드 인덕턴스 *l ≈ 2L(ln(2l/d)-1) NH*

소형화는 인덕턴스를 줄입니다 30%

다음 국경: 고급 포장

X2SON이 0.6mm 스케일에 도달 할 때, 혁신이 바뀝니다:

-

3D 포장: TSV 가능 수직 통합

-

이기종 통합: 다중 노드 다이 어셈블리

-

광자: 실리콘 광자의 공동 디자인

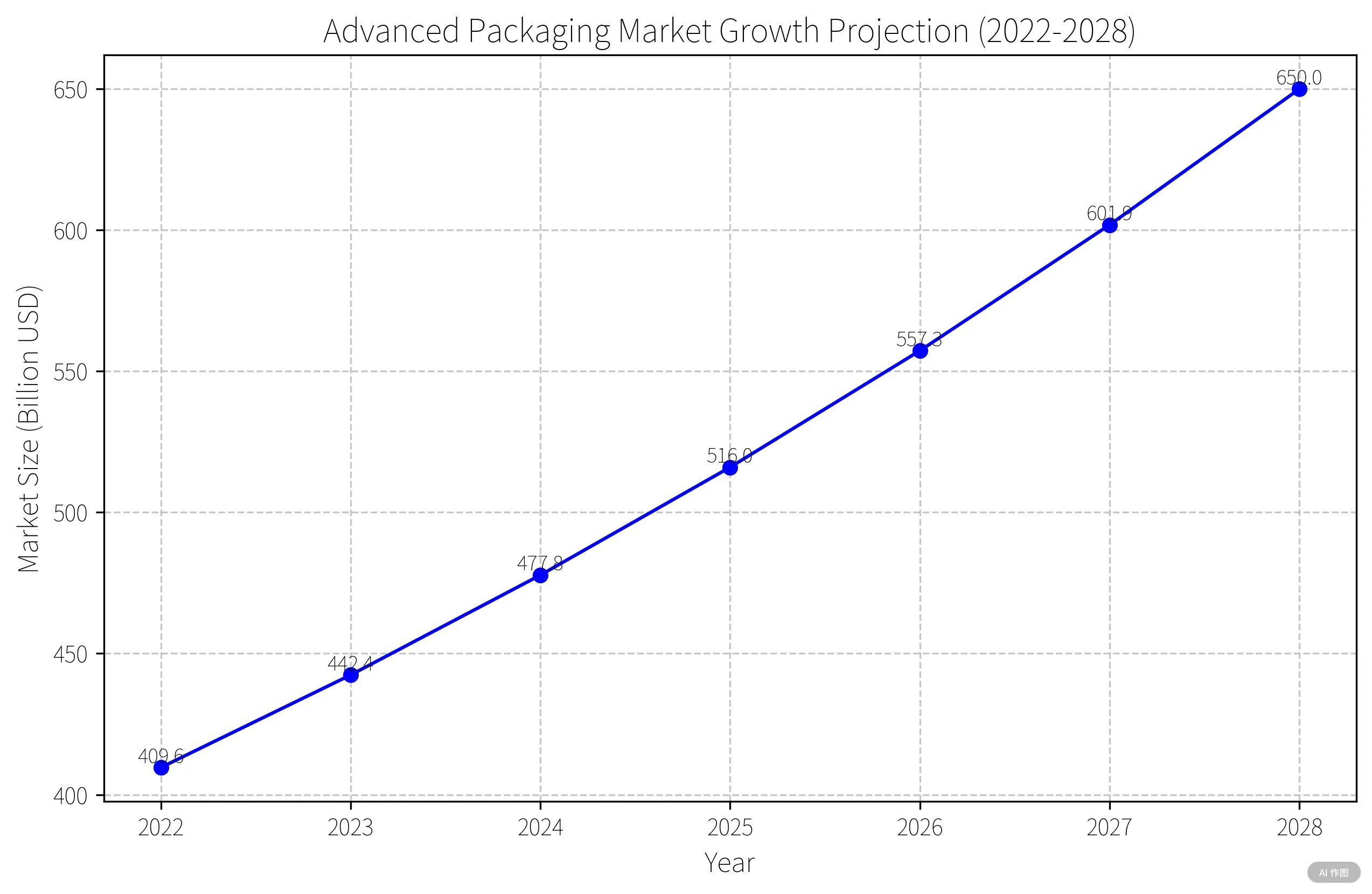

시장 예측 (yole développement):

8% CAGR을 통해 2028 → $ 65B 시장

포장은 이제 시스템 성능을 비판적으로 정의합니다 - 단순한 보호를 넘어서.

결론

DIP의 2.54mm 피치에서 X2SON의 0.6mm 발자국까지, 포장 발전은 지속적으로 전자 제품을 재정의합니다. 모든 슬림 스마트 폰 및 5G 장치는 이러한 보이지 않는 혁신에 의존합니다.. AI 및 Quantum Computing이 떠오르고 있습니다, 칩 포장은 나노 스케일 경계를 계속 밀어 넣을 것입니다.

*다음으로 시리즈:

BGA/CSP/WLCSP 기술

3D 포장 & TSV 상호 연결

고급 포장 재료 과학

계속 지켜봐주십시오!*

UGPCB 로고

UGPCB 로고