포장 기술의 모든 미세한 발전은 전자 제품의 물리적 경계를 재구성합니다..

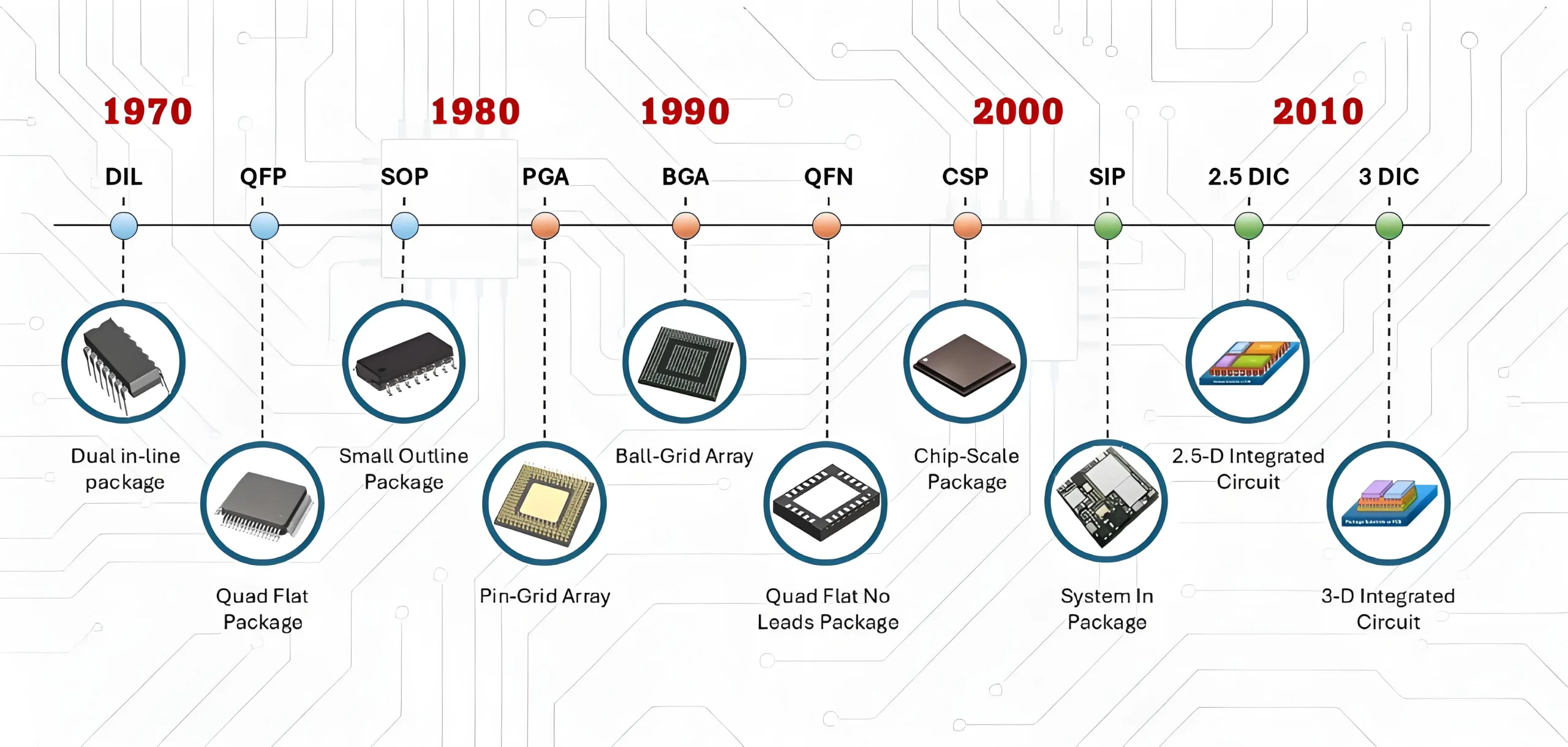

지난주 칩 포장의 진화: DIP에서 X2SON까지 - 소형화가 전자 제품을 재구성하는 방법, 우리는 통로 포장 시대를 탐구했습니다 (담그다) 그리고 표면 장착 장치 (예규, 관찰, 아들) 시작 장치 소형화. 이 기술은 현대 포장 기초를 마련했습니다, 그만큼 소형화 혁명 계속합니다. 오늘, 우리는 쿼드 플랫에서 웨이퍼 레벨 CSP에 이르기까지 고밀도 패키지를 검사하고 PCB 설계 제한.

쿼드 플랫 패키지: 우주 밀도 균형

쿼드 플랫 패키지 (MFF, PLCC/QFJ, QFN) 4 개의 패키지 가장자리를 모두 사용하여 더 높은 I/O 밀도에 대한 비판적 진화를 나타냅니다..

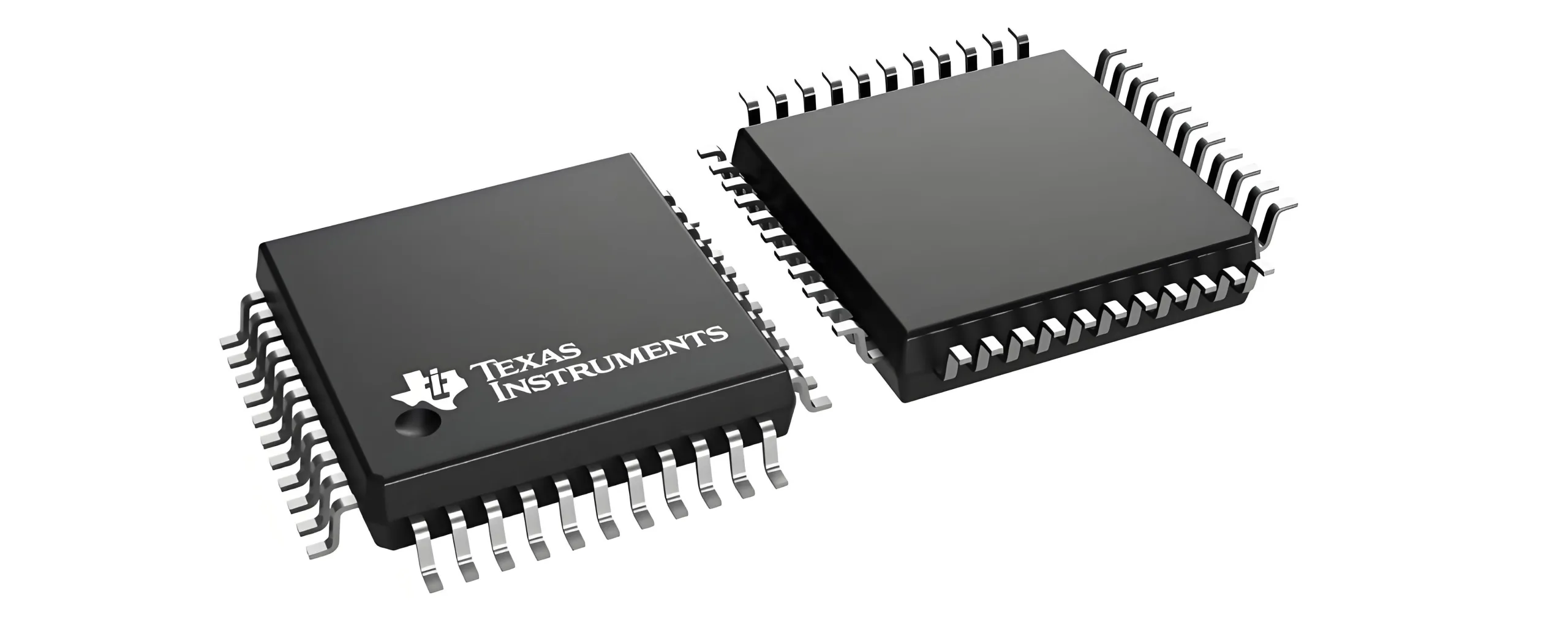

MFF: 갈매기 밀도 선구자

MFF (쿼드 플랫 패키지) 상징적 인 기능 “갈매기” (L 자형) 모든면에서 확장되는 리드. 그것은 핀 피치 (0.4mm/0.5mm/0.65mm) 지시 PCB 라우팅 밀도 및 납땜 정밀도.

QFP 변형:

-

크기/두께: LQFP (저 프로파일), TQFP (얇은), VQFP (매우 얇은)

-

재료: PQFP (플라스틱), MQFP (금속)

-

열 향상: HQFP, HLQFP, htqfp, HVQFP

-

보호: BQFP (범퍼 - 코너 패드는 구부러진 리드를 방지합니다)

열 관리가 중요합니다. 교차점-아함형 열 저항 공식 θja = (TJ -TA)/피 (어디 TJ= 정션 온도, 깃 달기= 주변 온도, 피= 전원) 열 소산 설계를 지배합니다.

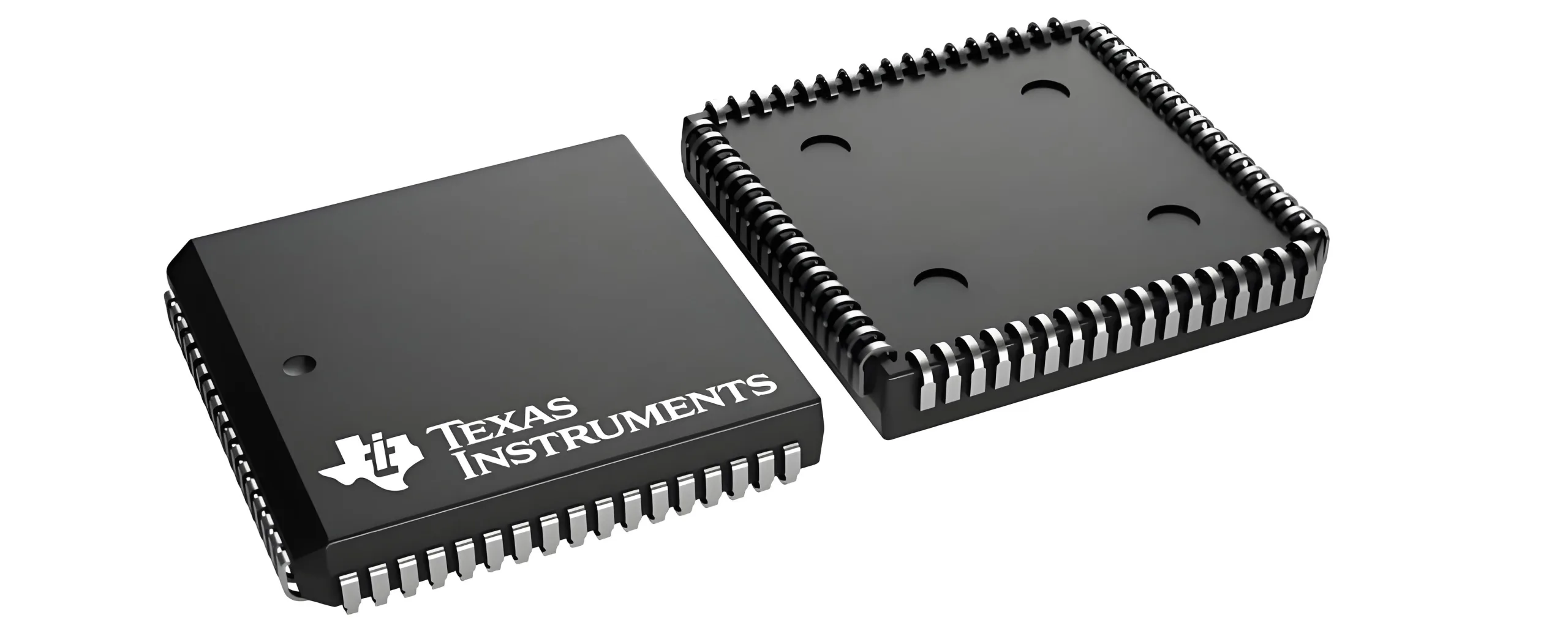

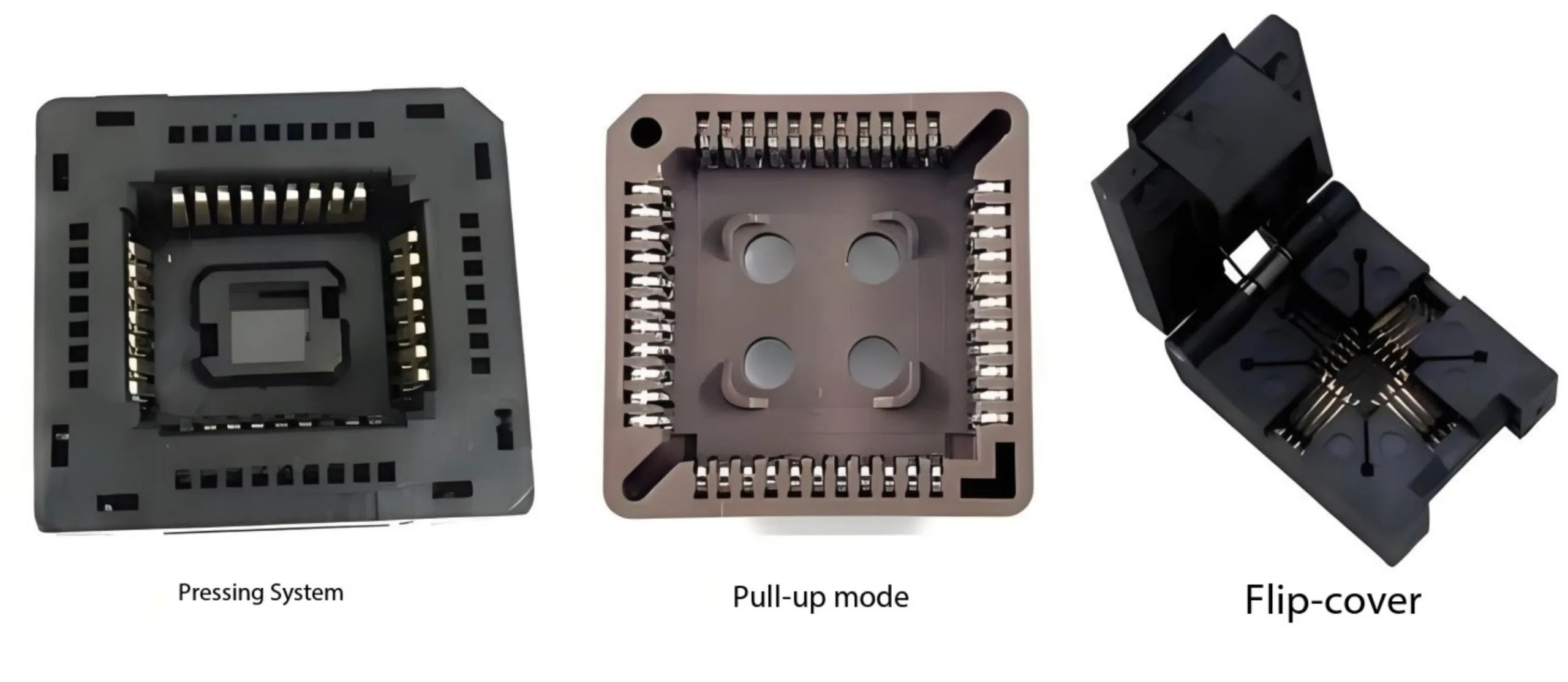

PLCC/QFJ: J- 리드를 통한 안정성

plcc (플라스틱 리드 칩 캐리어) 또는 QFJ (쿼드 플랫 j 리드) 진동/열 응력에 대한 기계적 안정성을 위해 하향 구향 J 자형 리드를 사용합니다..

표준화 이점: PLCC/QFJ의 유니버설 테스트 소켓과의 높은 호환성은 생산 테스트를 간소화합니다.. QFJ는 기술적으로 정확하지만, “plcc” 업계가 선호되는 상태로 남아 있습니다.

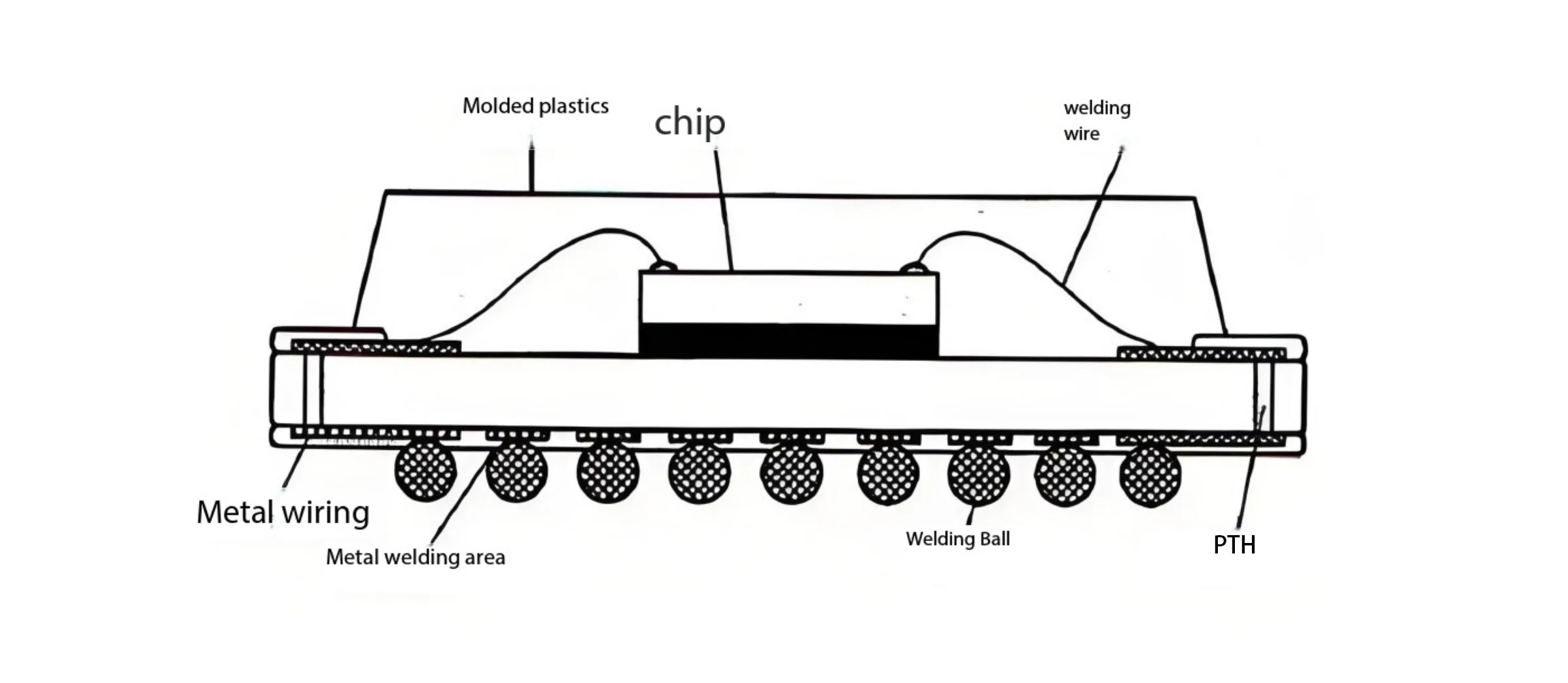

QFN: 리드리스 소형화 혁신

QFN (쿼드 아파트가 없습니다) 외부 리드를 제거합니다, 연결:

-

노출 된 패드 (EP): 직접 열 경로 PCB 구리

-

습한 측면: 측면 벽 솔더 가능한 패드

주요 장점:

-

초소형: 40% QFP보다 작습니다

-

전기 우월성: 짧은 경로는 기생 인덕턴스를 줄입니다 (L ≈ μ · l/w)

-

열 효율: 더 낮은 θja vs. 동일한 크기의 QFP

두께 진화: LQFN → UQFN → VQFN → WQFN → X1QFN → X2QFN. LCC (LPCC/LCCC) 리드리스 세라믹/플라스틱 변형입니다.

배열 패키지: 밀도 한계 혁명

쿼드 플랫이 I/O 제한에 도달하면, 배열 패키지 (LGA, BGA) 2D 상호 연결 밀도를 활성화하십시오.

LGA: 정밀 탄성 연결

LGA (랜드 그리드 어레이) 정확하게 정렬 된 금속 접점을 사용합니다 (예를 들어, LGA775: 775 콘택트 렌즈) 소켓 핀으로 결합.

핵심 가치:

-

소켓 가능성: CPU 업그레이드/유지 보수

-

낮은 인덕턴스: 짧은 신호 경로

-

높은 신뢰성: CPU에 이상적입니다 (인텔/AMD)

한정: 소켓 비용/크기는 소형 장치에서 BGA를 선호합니다. 메모: LGA는 직접 SMT 납땜 될 수 있습니다.

BGA: 솔더 볼 우세

BGA (볼 그리드 어레이) 솔더 볼 매트릭스를 통해 연결합니다. 볼 피치 (0.3–1.0mm; <0.2FBGA의 경우 MM) 중요합니다.

혁신적인 장점:

-

고밀도: >1,000 I/US (대. QFP의 ~ 300)

-

우주 절약: 30%+ 면적 감소 대. MFF

-

전기/열: 낮은 신호 지연; 공은 열을 만듭니다

-

자기 정렬: 표면 장력 에이즈 어셈블리

BGA 가족:

-

재료: PBGA (플라스틱), CBGA/CABGA (세라믹)

-

크기/피치: NFBGA/FBGA (파인 피치), Tinybga, DSBGA/WCSP (다이 크기), LFBGA/VFBGA (얇은)

-

완성:

-

FCBGA (플립 칩): 미생물을 통한 직접 다이 버스트 연결

-

팝 (패키지 온 패키지): 수직 스태킹 (예를 들어, 논리 + 메모리)

-

PG-WF2BGA: 팬 아웃 웨이퍼 수준 포장

-

도전: X- 선 검사 (axi), 복잡한 재 작업, CTE 매칭 PCB 재료.

배열 패키지 비교

| 특징 | PGA (핀 그리드 어레이) | LGA (랜드 그리드 어레이) | BGA (볼 그리드 어레이) |

|---|---|---|---|

| 연결 | 강성 핀 | 평면 접촉 | 솔더 볼 |

| 주요 강점 | 소켓 신뢰성 | 밀도 + 소켓 가능 | 최대 밀도/분 크기 |

| 신호 지연 | 제일 높은 | 중간 | 가장 낮습니다 |

| 응용 | 레거시 CPU/산업 | 데스크탑/서버 CPU | 모바일/GPU/SOC |

| PCB 공간 | 크기가 큰 | 중간 | 콤팩트 |

칩 스케일 & 웨이퍼 수준 패키지: 물리적 한계에 접근합니다

CSP: 크기 경계를 재정의합니다

CSP (칩 스케일 패키지) 주요 메트릭: 패키지 크기 ≤ 1.2 × 다이 크기 (대. 2전통적인 경우 –5 ×). 본질적으로 소형화 된 BGA (FBGA/VFBGA) 더 미세한 피치로 (0.2–0.5mm).

값: 웨어러블/센서를위한 궁극적 인 소형화.

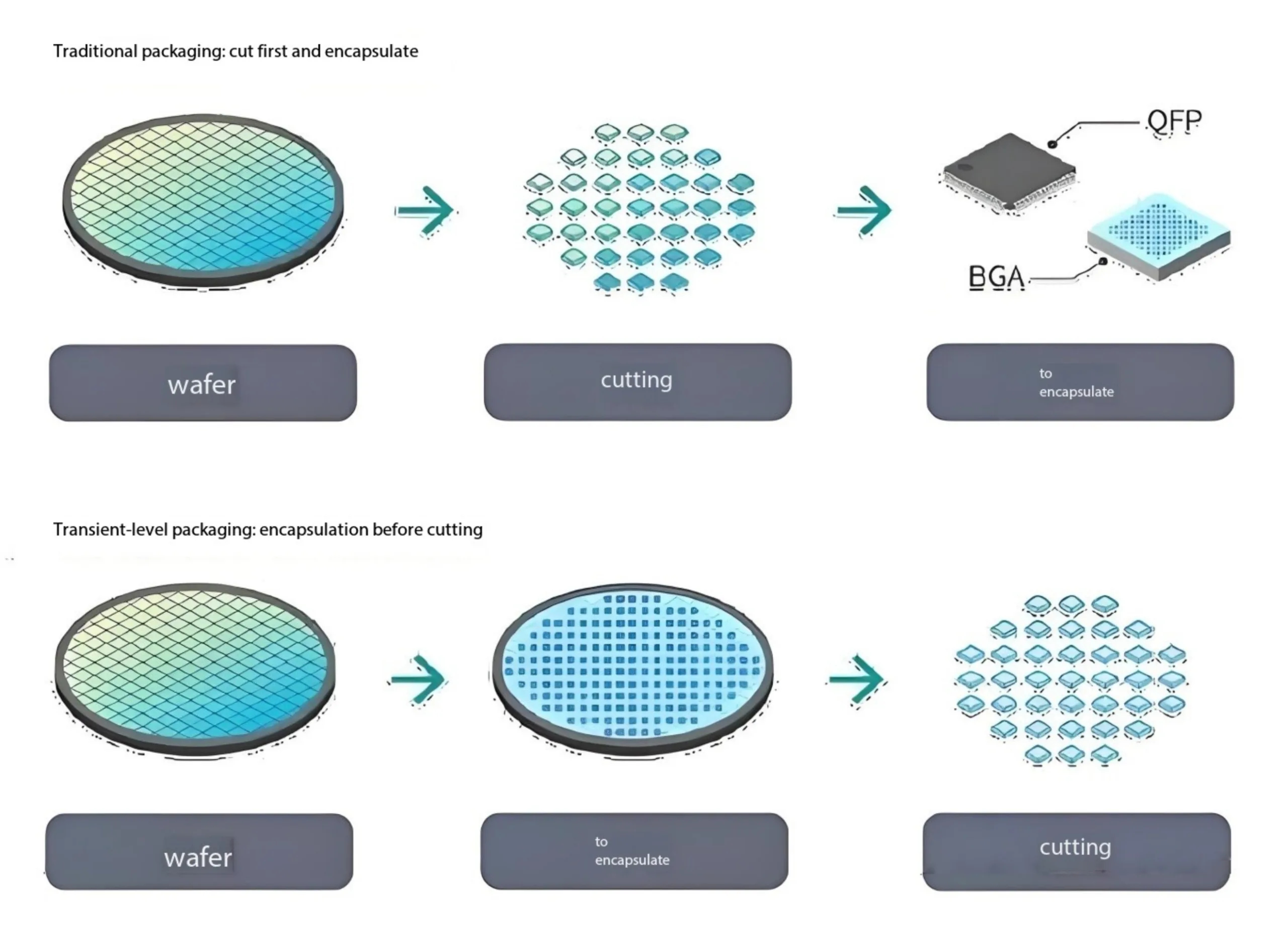

ulc: 웨이퍼 수준의 혁명

WLCSP/WAFER 수준 포장은 모든 단계를 완료합니다 (RDL, 볼링) 다이 싱 전에 웨이퍼에.

파괴적인 장점:

-

최소 크기: ≈ 다이 치수

-

비용 절감: 30-50% 저렴합니다 (기판/성형이 없습니다)

-

피크 성능: 가장 짧은 상호 연결, 가장 낮은 기생충

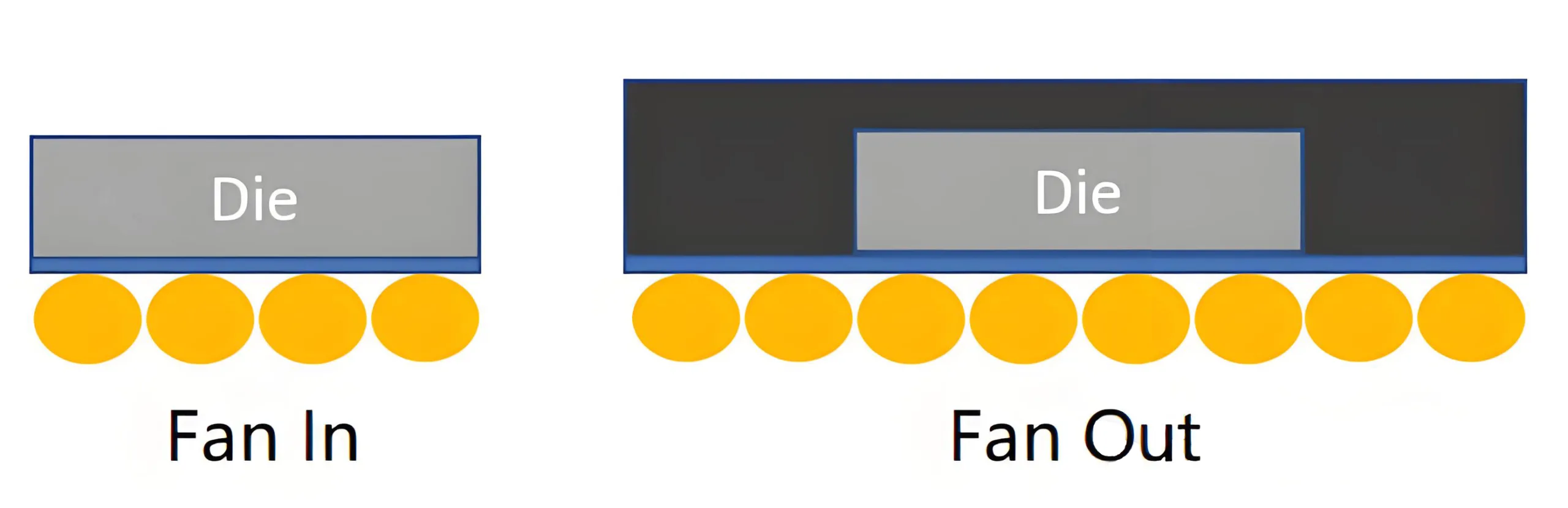

WLCSP 유형:

-

팬인 WLCSP:

-

다이 지역 내의 공

-

패키지 크기 = 다이 크기

-

센서/PMIC의 저비용

-

-

팬 아웃 WLCSP (예를 들어, TSMC 정보, 삼성 FO-PLP):

-

공은 다이를 넘어 확장됩니다

-

패키지 크기 > 다이 크기

-

더 높은 I/O 밀도, 멀티 칩 통합

-

프리미엄 SOCS/RF 모듈 용

-

시각적 ID: 캡슐화되지 않은 실리콘 (대. 수지-보통 DFN).

포장 형태 & 본딩 기술

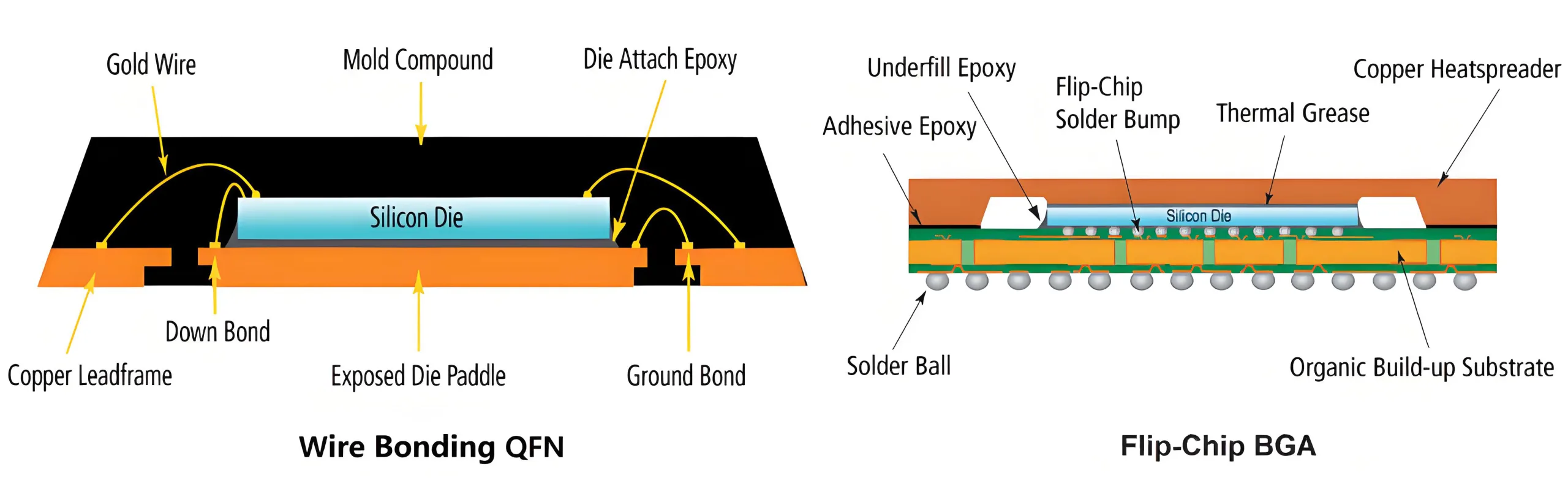

외부 패키지 양식 (QFP/BGA/WLCSP) 내부 결합은 본질적으로 연결되어 있습니다:

-

와이어 본딩:

-

성숙한, 저비용

-

QFP/QFN/미드 레인지 BGA를 지배합니다

-

전선이 있습니다; 보통 I/O

-

-

플립 칩:

-

죽는 것은 미생물을 통해 얼굴을 부착합니다

-

가장 짧은 상호 연결, 가장 낮은 인덕턴스

-

FCBGA/WLCSP/고성능 CSP에 필수적입니다

-

결론 & 미래의 프론티어

QFP에서 LGA/BGA까지 및 마지막으로 CSP/WLCSP, 칩 포장 진화는 a입니다 우주 압축 연대기, 성능 이득, 비용 최적화. 각 소형화 도약은 PCB 설계를 재구성합니다, 다층 HDI, 고급 재료.

다음 국경: TSV와 같은 기술 (경유실을 통해), 한모금 (패키지 시스템), 2.5D/3D IC는 이제 3D 이종 통합을 가능하게합니다, PCB 디자인을 새로운 차원으로 밀기 - 다음 기사에서 탐색 할 수 있습니다..

10 억 트랜지스터가 덩어리 크기의 패키지에 맞는 경우, 분자 규모의 전자 공학 전투.

UGPCB 로고

UGPCB 로고

정보를 공유해 주셔서 감사합니다..

와우 이 블로그 정말 훌륭해요 당신의 기사를 읽는 걸 정말 좋아해요. 앞으로도 좋은 그림 부탁드려요! 당신은 인식, 많은 사람들이 이 정보를 찾고 있습니다., 당신은 그들을 크게 도울 수 있습니다.