전자 제조 산업에서, PCBA의 수율 (인쇄 회로 보드 어셈블리) 처리는 생산 비용과 시장 경쟁력에 직접 영향을 미칩니다. 연구 기반의 연구 IPC 국제 표준은이를 나타냅니다 80% 설계 단계에서 생산 결함을 식별하고 최적화 할 수 있습니다..

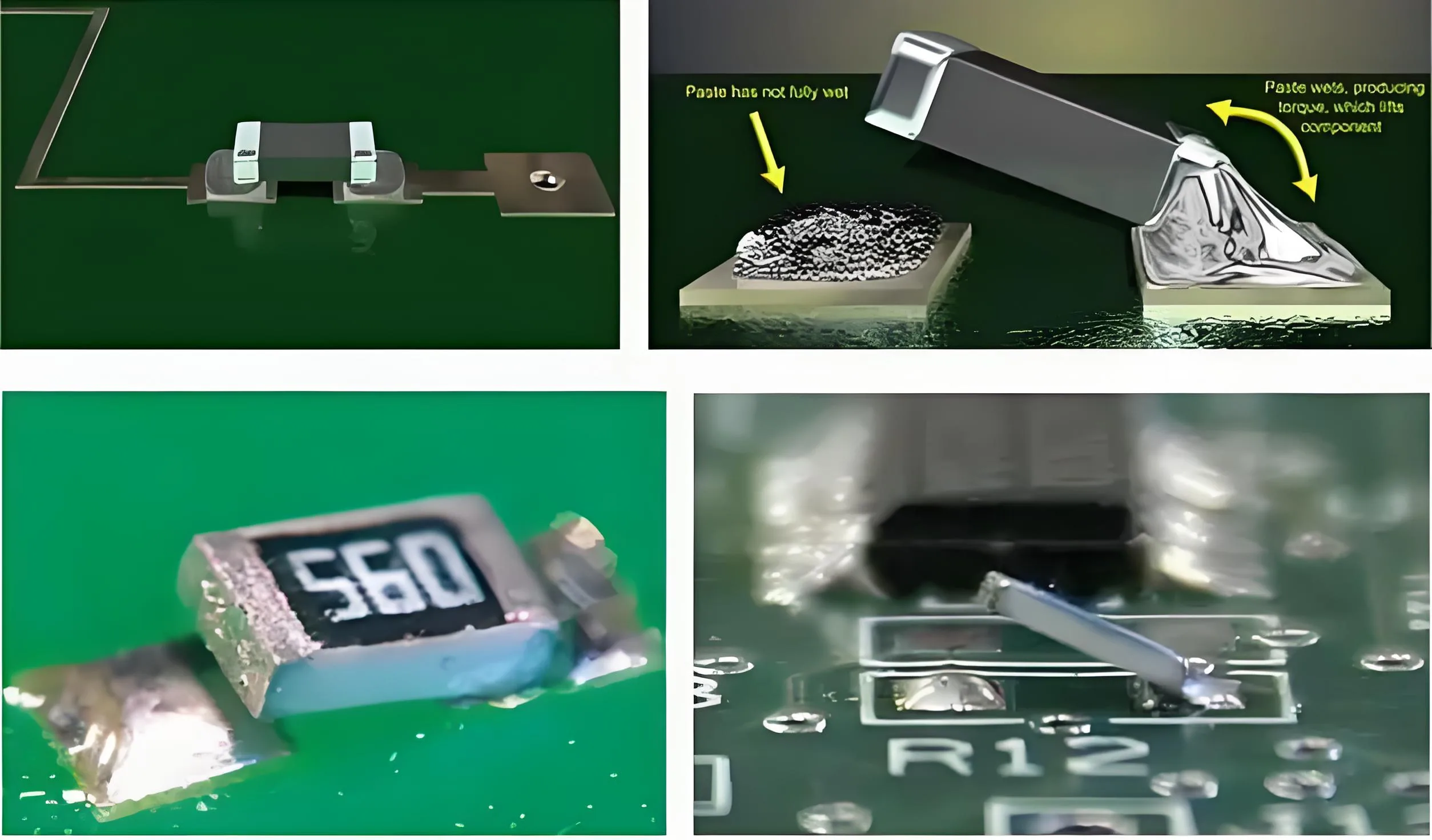

에서 SMT (표면 실장 기술) 조립 프로세스, 묘비 결함 - 칩 구성 요소의 한쪽 끝이 패드에서 멀어지게됩니다. (그림과 같이 1)- 가장 일반적인 문제 중 하나입니다. 소규모 수동 구성 요소에서 자주 발생합니다, 특히 0402 칩 커패시터 및 저항. 이 기사는 심층 분석을 제공합니다, 실험 설계에 기초합니다 (암사슴) 방법론, 스텐실 잘못 등록과 묘비 결함 사이의 관계, 실용적이고 효과적인 솔루션을 제안합니다.

-

묘비 결함의 메커니즘 및 영향

묘비의 기본 원인은 구성 요소의 두 단자에 대한 납땜 장력의 불균형입니다.. 솔더 페이스트가 녹을 때, 표면 장력 또는 비동기 용융 시간의 차이로 인해 솔더 페이스트가 나중에 녹는 끝에서 성분을 위로 당길 수 있습니다..

1.1 묘비 결함의 형성 메커니즘

리플 로우 납땜 중, 칩 구성 요소의 상단과 하단 표면이 가열됩니다.. 일반적으로, 가장 큰 노출 구역이있는 패드가 먼저 가열됩니다., 솔더 페이스트의 융점 이상의 온도에 도달. 결과적으로, 나중에 젖은 구성 요소의 끝은 종종 반대쪽 끝에 이미 고정 된 솔더의 표면 장력에 의해 당겨집니다..

납땜 인장 균형 균형 공식:

f_net = f1 – F2 = γ_LV (cosθ₂ – cosθ₁) · l

어디:

F_net은 순 긴장력입니다,

γ_LV는 액체 증기 표면 장력입니다,

θ는 접촉각입니다,

L은 패드 길이입니다.

1.2 묘비 결함에 기여하는 요인

현장 데이터 분석을 기반으로합니다, 묘비 결함은 주로 다음 요인에 의해 영향을받습니다:

-

PCB 설계 요인 (30%): 불규칙한 패드 크기 설계 및 차선책 레이아웃

-

재료 요인 (25%): 구성 요소의 솔더 가능성이 좋지 않습니다, 산화 된 종단

-

프로세스 요소 (45%): 납땜 페이스트 잘못 등록, 배치 정확도가 충분하지 않습니다, 부적절한 리플 로우 납땜 온도 프로파일

-

DOE 실험 설계 및 방법론

DEK 스텐실 프린터의 잘못 등록으로 인한 묘비 문제를 해결하려면, 기술 팀 UGPCB 프로세스 매개 변수의 최적 조합을 식별하기 위해 엄격한 DOE를 설계했습니다..

2.1 실험적인 목표와 특성 가치 정의

특징적인 가치: 납땜 페이스트 잘못 등록 (단위: mm)

특징적인 유형: 더 작은 베터

-

측정 장비: AOI (자동 광학 검사)

-

측정 방법: 각 조합에 대해, 측정하다 10 무대. 각 보드에서, 솔더 페이스트의 오해를 5 개로 측정하십시오 0402 구성 요소 패드, 그리고 해당 이사회의 잘못 등록으로 최대 가치를 취하십시오..

-

계산 방법: 평균 오도 값 10 보드는 해당 매개 변수 조합의 잘못된 등록 값으로 간주됩니다..

2.2 고정 및 실험 요소의 선택

고정 요인:

-

보드 유형: 록 레이크 (인텔)

-

생산 라인: 선 14

-

원판: 전체적으로 사용 된 것과 동일한 스텐실

-

스퀴지: 전체적으로 사용 된 것과 동일한 스퀴지 세트

-

기계적 상태: 장비는 유지 보수를 거쳤습니다

실험적 요인:

-

요인 a: 진공 보류 시간 (유지 시간 지속 시간을 조정하여 진공력 수준을 제어합니다)

-

요인 b: 컨베이어 레일 폭 (고정하기 위해 폭을 조정합니다 PCB 그리고 움직임을 방지하십시오)

-

요인 c: 압박 압력

-

요인 d: 인쇄 속도

-

요인 e: 신세 마크 사이의 거리

-

실험 결과 및 분석

실험은 두 단계로 수행되었습니다: 첫 번째 단계는 중요한 요소를 상영했습니다, 두 번째 단계는 파라미터 조합을 최적화했습니다.

3.1 1 단계 결론

중요한 요인 효과: 에이, 광고 (상호 작용), CD (상호 작용), 이자형

2 단계에 대해 선택된 요인: 에이, 기음, 디, 이자형

매우 중요한 요소: 에이, 광고, CD

예상치 못한 발견: 요인 b (컨베이어 레일 폭), 처음에는 매우 영향력이 있다고 생각했습니다, 큰 영향을 미치지 않았습니다. 가장 중요한 효과는 상호 작용 효과였습니다.

3.2 2 단계 실험 및 ANOVA 분석

ANOVA 결과는 요인 a, 기음, 그리고 D는 두 번째 단계에서 중요하지 않았다. 이것은 관찰 된 주요 변동이 임의의 오류로 인한 것임을 시사합니다., 매개 변수 최적화가 거의 최적 수준에 도달했음을 나타냅니다.

-

최적의 프로세스 매개 변수 및 표준화

실험 결과를 기반으로합니다, 최적의 생산 공정 매개 변수를 결정했습니다:

테이블 1: 개선 전후의 프로세스 매개 변수 비교

| 매개 변수 | 사전 개선 | 개선 후 | 변화 |

|---|---|---|---|

| 압박 압력 | 6.0 kg | 5.4 kg | 감소하다 10% |

| 인쇄 속도 | 40 mm/sec | 50 mm/sec | 증가하다 25% |

| 진공 보류 시간 | 0.4 비서 | 0.4 비서 | 변화가 없습니다 |

| 신속한 마크 거리 | 361.9 | 361.9 | 변화가 없습니다 |

| 컨베이어 레일 폭 | 244.3 | 244.3 | 변화가 없습니다 |

선택된 매개 변수 조합에 대한 이론적 근거:

-

요인 a (진공 보류 시간): 선택된 0.4 프린터 시간 손실을 최소화하기 위해 0.4 ~ 0.8 초 범위 내에서.

-

요인 c (압박 압력): 하위 레벨을 선택했습니다 5.4 kg, 과도한 압력으로 인해 스텐실 변형과 더 두꺼운 솔더 페이스트 증착을 유발할 수 있습니다..

-

요인 d (인쇄 속도): 선택된 50 mm/sec, 빠른 속도로 인해 솔더 페이스트 방출이 좋지 않아.

-

혜택 평가 및 비용 분석

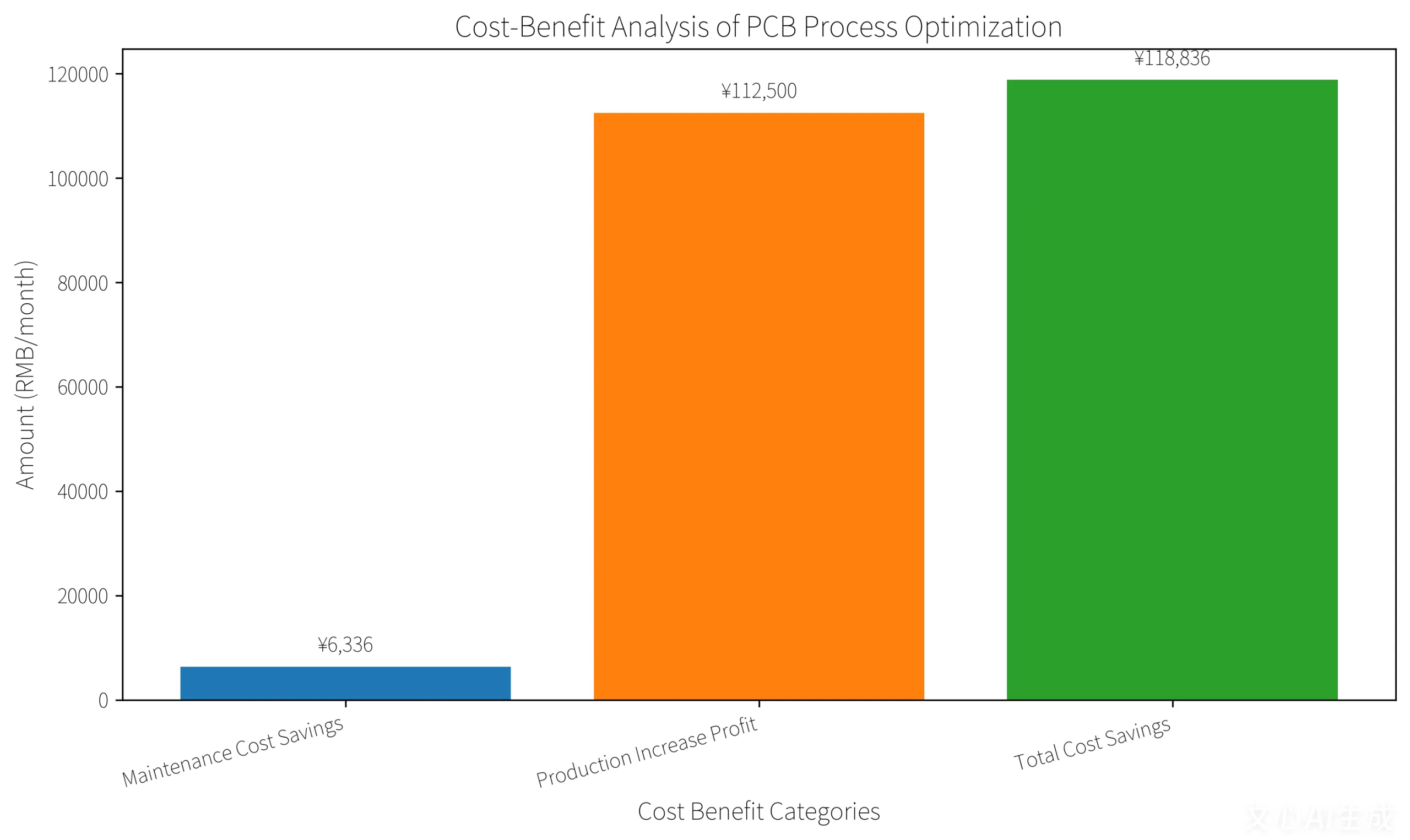

프로세스 매개 변수 최적화 후, 상당한 경제적 이점과 품질 개선이 이루어졌습니다:

5.1 품질 향상 결과

묘비 결함 속도는 감소했습니다 29% 에게 18%, an 11 백분율 포인트 감소. IPC-7912 표준에 따라 계산됩니다, 프로세스 기능 지수 CP가 개선되었습니다 0.89 에게 1.32, 그리고 CPK는 개선되었습니다 0.72 에게 1.08.

5.2 경제 이익 계산

-

비용 절감을 재 작업하십시오: 66 주당 SMT 라인 당 결함이있는 보드가 적습니다. ~에 2 보드 당 다시 재 작업:

노동 저축 = 66 보드 × 2 최소/보드 × 8 선 × 4 주 = 4224 최소/월

비용 절감 = 90 RMB/Hour × (4224 / 60) = 6,336 RMB/월 -

생산량 증가 이익: 사전 개선, 잘못 등록을위한 프린터 조정은 약. 5 최소/라인/데이:

노동 저축 = 5 최소/일 × 30 날 × 8 라인 = 1200 최소/월

출력 증가 이익 = (1200 / 60 / 24) × 1500 보드/일 × 90 RMB/보드 = 112,500 RMB -

총 월간 비용 절감 = 6,336 + 112,500 = 118,836 RMB

-

풀 프로세스 품질 관리 시스템 구축

묘비 문제를 철저히 해결합니다, 모든 단계를 다루는 포괄적 인 품질 보증 시스템을 구축하는 것이 필수적입니다.: 들어오는 재료 → 프로세스 내 생산 → 완제품 검사 → 판매 후 고장 분석.

6.1 들어오는 품질 관리 (IQC)

IQC는 첫 번째 체크 포인트입니다. PCB 구리 호일과 같은 주요 원료 기판 외관 및 치수 샘플링 검사가 필요합니다: 구리 호일 표면에는 산화가 없어야합니다, 핀홀, 그리고 흠집; 기판 두께 공차는 ± 0.05mm 표준을 충족해야합니다.

6.2 프로세스 품질 관리 (IPQC)

IPQC는 전체 PCB 제조 공정에 걸쳐 있습니다, ~와 함께 “품질 체크 포인트” 각 키 작동 후. 내부 층 이미징 후, 추적 폭/간격 및 에칭 균일 성을 검사하십시오; 라미네이션 후, X- 레이 검사를 사용하여 인터레이어 공극 및 오해를 확인하십시오.; 도금 후, 구리 두께 테스터를 사용하여 구멍과 표면 구리 두께를 측정하십시오..

6.3 최종 품질 관리 (FQC)

FQC는 배송 전 최종 테스트입니다, 세 가지 주요 차원을 포함합니다: 모습, 전기 성능, 신뢰성. 외관을 위해, 매뉴얼과 AOI 검사의 조합을 사용하십시오; 전기, 공연하다 100% 열리지 않거나 반바지를 보장하기 위해 플라잉 프로브 또는 손 초과 테스트; 신뢰성을 위해, 고객 요구 사항에 따라 환경 테스트를 수행합니다.

-

PCB 설계 최적화 권장 사항

프로세스 최적화를 넘어서, PCB 설계 최적화는 묘비 결함을 방지하는 데 중요합니다.

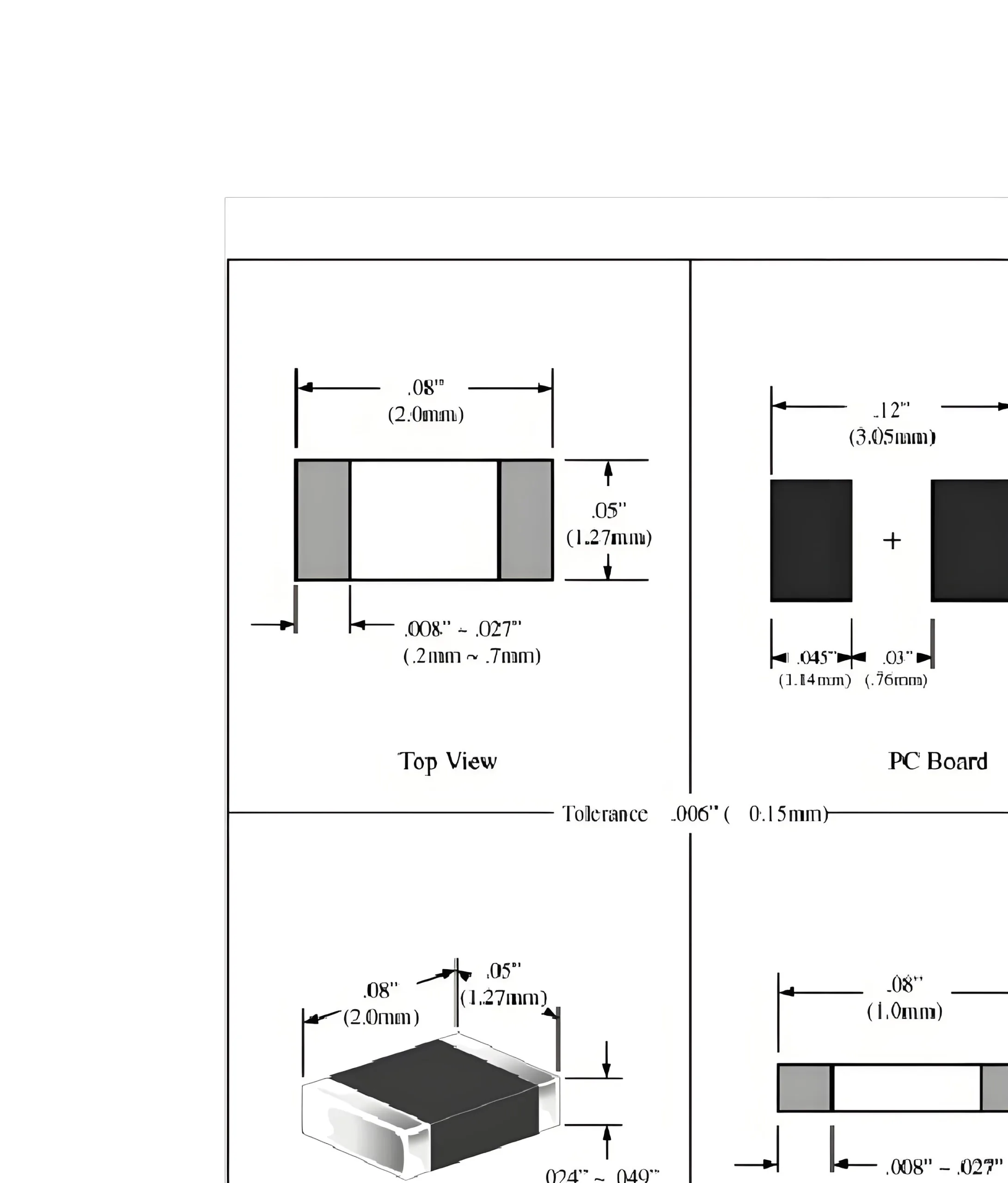

7.1 패드 디자인 표준

랜드 패턴 설계 최적화 - 적절한 패드 확장 치수 확인. 패드의 가장자리가있는 시나리오를 피하십시오 (일직선) 45 °를 초과하는 습식 각도를 형성합니다. IPC-7351 표준에 따르면, ~을 위한 0402 구성 요소, 패드 간격은 0.35 ± 0.05mm 이내에 제어해야합니다, 패드 너비는 0.5 ± 0.05mm이어야합니다.

7.2 레이아웃 최적화 전략

부족한 구성 요소 레이아웃은 크기 크기 변화로 이어질 수 있습니다. 구성 요소 PCB에서. 리플 로우 납땜 중, 이것은 과도한 온도 차이를 유발합니다, 구성 요소의 양쪽에서 고르지 않은 가열, 그리고 묘비. 균일 한 열 분포를 보장하기 위해 설계 중에 고출력 장치 옆에 작은 구성 요소를 배치하지 마십시오..

-

후속 조치 및 지속적인 개선

개선의 지속 가능성을 보장하기 위해 다음 조치가 구현되었습니다.:

8.1 지속적인 모니터링 및 통계 분석

묘비 수율 데이터를 지속적으로 수집하십시오 30 날, 모니터링을 위해 제어 차트를 활용하십시오, 지속적인 개선 효과를 확인합니다. 10 월의 데이터는 지속적인 개선이 심각한 것으로 나타났습니다, 잘못 등록에 지속적으로 긍정적 인 영향을 미칩니다.

8.2 인과 관계 분석 및 제어 표준

개선 결과를 기반으로합니다, 잘못 등록과 묘비 사이의 인과 관계를 연구하십시오, 제어 표준을 설정하십시오, 이를 매일 관리에 통합합니다. 구현 a “품질 추적 성 코드” 각 PCB에 대해, 원료 배치와 같은 기록 정보, 생산 장비, 검사 데이터, 그리고 운영자.

8.3 확장 및 기술 이전

이 DOE의 결과를 다른 생산 라인 및 제품 모델로 확장. 프로세스 매개 변수 데이터베이스를 설정하십시오, 입증 된 솔루션의 매개 변수를 표준화하십시오, 새로운 프로그램 디버그 시간을 줄입니다 24 몇 시간 3 시간.

-

결론과 전망

DOE 방법론 사용, 우리는 솔더 페이스트 잘못 등록에 영향을 미치는 주요 프로세스 매개 변수를 성공적으로 식별하고 묘비 결함 속도를 줄였습니다. 29% 에게 18% 매개 변수 최적화를 통해. 이는 약 118,836 엔의 월별 비용 절감을 달성합니다, 연간 약 1426 백만 엔의 연간 절약으로 번역.

앞을 내다보며, 우리는 프로세스 연구를 더욱 심화시킬 것입니다, 프로세스 매개 변수 최적화에서 AI 기술의 적용을 탐색하십시오., 지능형 프로세스 최적화 시스템을 구축하십시오, 제품 품질 및 생산 효율성의 지속적인 개선을 달성합니다..

신제품 소개 요구가있는 전자 제조업체의 경우, UGPCB와 같은 원 스톱 솔루션 제공 업체를 선택하는 것이 좋습니다., PCB 디자인을 통합합니다, 조작, PCB, 그리고 PECVD 서비스. 설계 단계에서 PCB 및 PCBA 프로세스 중 잠재적 인 문제를 고려합니다., 다양한 시뮬레이션 테스트를 수행합니다, 들어오는 재료에서 테스트 및 포장에 이르기까지 풀 프로세스 품질 관리 시스템을 구현하십시오., 제품 품질 안정성 및 일관성 보장.

UGPCB 로고

UGPCB 로고