ITEQ IT-158 PCB 보드 재질

핵심 성능 매개 변수 & 기술적 이점

ITEQ IT-158 라미네이트는 최고의 선택으로 나타납니다 고급 PCB 뛰어난 기술 사양을 통한 제조:

열 신뢰성

-

Tg: 155℃ (무연 납땜 중 구조적 안정성을 보장합니다)

-

T-288: >30 288 ° C에서 초 (우수한 열 충격 저항)

-

TD-5%: 345℃ (극한 조건에서 박리를 방지합니다)

기계적 안정성

-

z 축 Cte: 40ppm/°C (3.3% 50-260 ° C에서의 확장)

-

껍질 힘: ≥8lb/인치 (구리 입은 본드 무결성)

-

수분 흡수: 0.08% (전기 안정성을 유지합니다 85% RH 환경)

고주파 신호 전송 특성

10GHz에서 유전체 성능

-

DK: 4.0 ± 0.05

-

Df: 0.018

*(0.15dB/인치 삽입 손실 감소가있는 5G/mmwave 응용 프로그램에 이상적입니다)*

일반적인 응용 프로그램 시나리오

5G 커뮤니케이션 인프라

-

기지국 안테나

-

광학 트랜시버

자동차 전자

-

ADAS 레이더 시스템 (AEC-Q200 호환)

-

ECU 제어 모듈

산업 자동화

-

서보 드라이브 (10,000105 ℃에서 HR MTBF)

-

파워 인버터

가전제품

-

스마트 폰 RF 모듈

-

노트북 마더 보드 HDI 디자인

PCB 재료 선택 워크 플로

단계 1: 요구 사항 분석

-

작동 온도 범위: Tmax +20 ° C 마진

-

신호 주파수 임계 값: ≥1GHz 중요합니다

-

환경 등급: IP67 준수

단계 2: 비교 평가

| 매개 변수 | ITEQ IT-158 | 경쟁자 a | 경쟁자 b |

|---|---|---|---|

| Tg (℃) | 155 | 140 | 130 |

| DF @10GHz | 0.018 | 0.025 | 0.032 |

| UL 인증 | 94다섯-0 | 94HB | 94V-1 |

단계 3: 신뢰성 검증

-

PCT 테스트: 121° C/100%RH/2ATM × 96HR

-

열 응력: 3× 솔더 딥 @288 ° C

-

CAF 저항: IPC-TM-650 2.6.25 준수

설계 최적화 전략

스택 up 구성

-

하이브리드 유전체 구성 (≤5% 두께 내성)

-

열 관리를위한 묻힌 vias

임피던스 제어

-

마이크로 스트립 라인 공차: ± 10%

-

차동 쌍 간격: 3× 유전체 높이

제조공정

-

교련: ≤0.15mm 스터브를 사용한 백 드릴링

-

표면 마감: Enepig가 선호했습니다 (~ 안에:3-5μm, au:0.05-0.1μm)

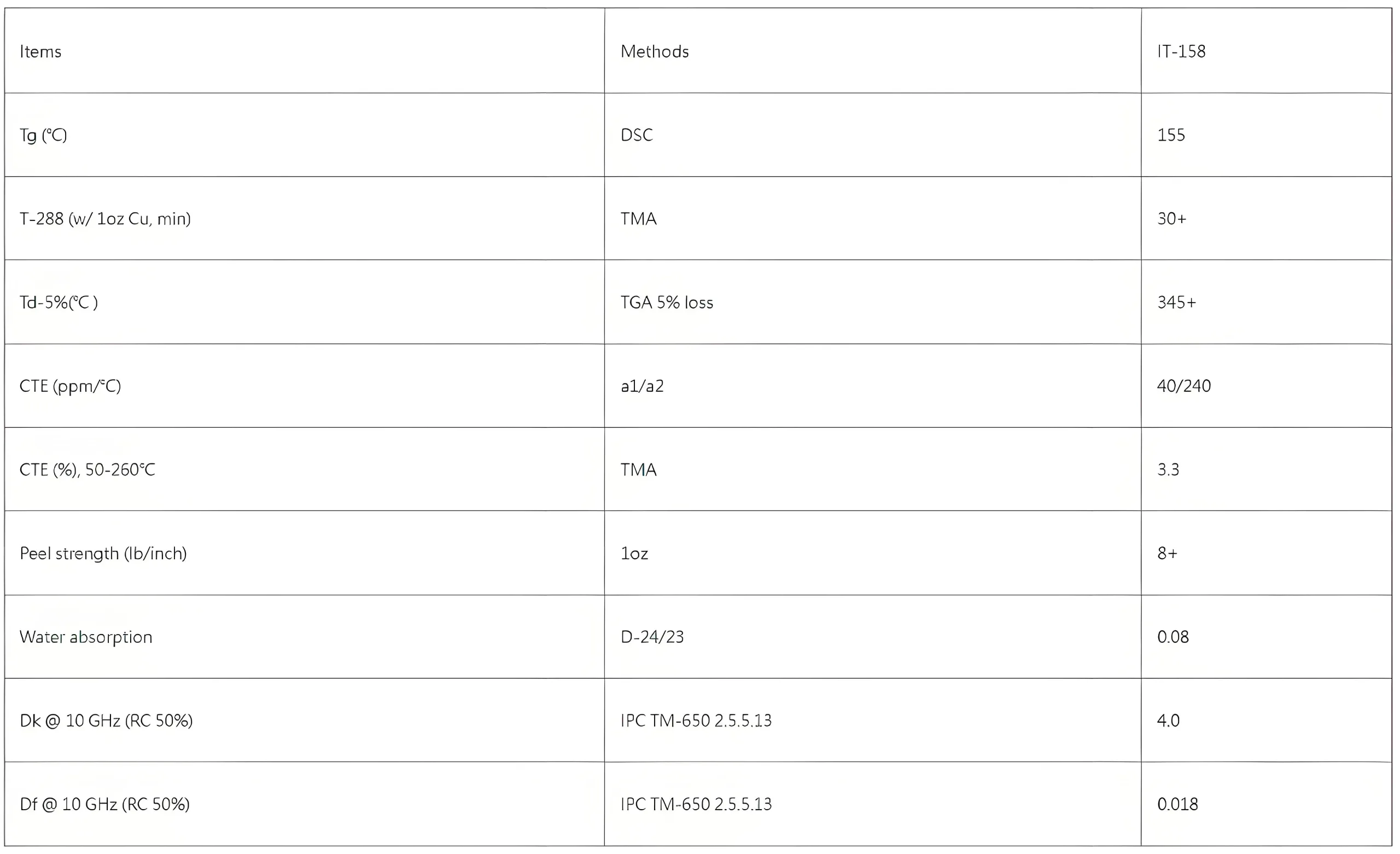

ITEQ IT-158 PCB 기판 매개변수 표

UGPCB 로고

UGPCB 로고

주제에 대한 실제적인 유익하고 환상적인 해부학적 구조, 이제는 사용자 친화적입니다 (:.