Introdução: Desafios e oportunidades em design de PCB de alta densidade

À medida que os produtos eletrônicos evoluem em direção a velocidades mais altas e maior integração, Projeto de PCB transformou tarefas simples de conexão em engenharia de sistemas complexos. Uma placa com 8000 Os PINs geralmente envolvem múltiplas interfaces de alta velocidade e unidades de gerenciamento de energia, onde o design inadequado pode levar a integridade do sinal problemas e falhas térmicas. De acordo com relatórios de mercado do IPC, o global interconexão de alta densidade (IDH) PCB mercado cresceu mais de 15% em 2022, destacando a demanda da indústria por conhecimento especializado em design.

Durante os estágios iniciais do projeto, os engenheiros devem analisar de forma abrangente os diagramas esquemáticos e a documentação de orientação de hardware para garantir a otimização de sinais de alta velocidade e caminhos de energia. Esta abordagem não só melhora PCBA confiabilidade mas também ajuda a identificar rapidamente Fornecedores de PCB e obter cotações precisas em um mercado competitivo.

Preparação de projeto de PCB: Análise de Sinais e Planejamento de Energia

Ao receber o esquema, o primeiro passo é uma revisão rápida para identificar PCB circuitos e sinais de alta velocidade, como LPDDR4, Pcie 3.0, e HDMI. As diretrizes de projeto fornecidas pelos engenheiros de hardware são cruciais; se estiver faltando, solicitar e documentar proativamente esses pontos-chave. Por exemplo, sinais de alta velocidade são particularmente sensíveis à impedância e aos planos de referência, e negligenciar esses detalhes pode levar à atenuação do sinal de até 20% (baseado no padrão IPC-2141).

Criar uma árvore de poder é o próximo passo essencial. Esta árvore ilustra claramente as condições atuais de cada ramo, facilitando a otimização do rede de distribuição de energia. Supondo que uma placa contenha vários conversores LDO e DC-DC, os cálculos da capacidade de carga atual devem considerar fatores de aumento de temperatura de acordo com o padrão IPC-2152. Por exemplo, uma entrada típica de 12 V, 3.3A capacidade de carga de corrente do módulo V de saída DC-DC a 25°C de temperatura ambiente pode ser estimada usando a fórmula I = k·A^0,7, onde k é uma constante material (tipicamente 0.024 para folha de cobre) e A é a área da seção transversal (em milímetros quadrados). Isso garante confiabilidade do caminho de energia e evita riscos de sobrecarga.

Durante a análise do sinal, placas podem incluir interfaces de alta velocidade como LPDDR4, Pcie 3.0, e USB 3.0, junto com sinais de áudio analógico e LVDS. Sinais de alta velocidade normalmente exigem controle de impedância, enquanto as seções analógicas precisam de isolamento para reduzir o ruído. Esta análise modular permite que os projetistas planejem previamente os recursos, melhorando subsequentemente Layout da placa de circuito impresso eficiência.

Planejamento de empilhamento e controle de impedância: Construindo uma base robusta de PCB

Planejamento de empilhamento é fundamental para o design de PCB de alta densidade, impactando diretamente integridade do sinal e desempenho EMC. Por um 8000 Placa PIN, uma estrutura de 10 camadas (como TOP/G1/S1/V1/G2/S2/V2/S3/G3/BOT) equilibra efetivamente custo e desempenho. O princípio é garantir que cada camada de sinal tenha um plano de terra correspondente como referência, reduzindo diafonia e descontinuidades de impedância. De acordo com o padrão IPC-2221, o material FR-4 típico tem uma constante dielétrica de aproximadamente 4.5. Ao calcular a impedância microstrip, a fórmula comumente usada é:

Z₀ = 87/√(εr + 1.41) × ln(5.98h/(0.8c + t))

Onde Z₀ é a impedância característica (em Ω), εr é a constante dielétrica, h é a espessura dielétrica (em mils), w é a largura do traço (em mils), e t é a espessura do cobre (em mils). Em design prático, colaborar com o seu Fabricante de placas de circuito impresso, fornecendo requisitos de impedância (como 50Ω single-ended ou 100Ω diferencial) para eles calcularem largura e espaçamento específicos do traço. Por exemplo, Os sinais LPDDR4 podem exigir uma configuração de largura de traço de 4mil e espaçamento de 4mil para corresponder à impedância alvo.

Esta abordagem de planejamento não apenas melhora a qualidade do sinal, mas também reduz as modificações em estágio final, acelerando o Produção de PCBA ciclo. As estatísticas mostram que os projetos que seguem as diretrizes de empilhamento IPC podem reduzir a perda de sinal em mais de 30% (fonte de dados: Padrão IPC-6012).

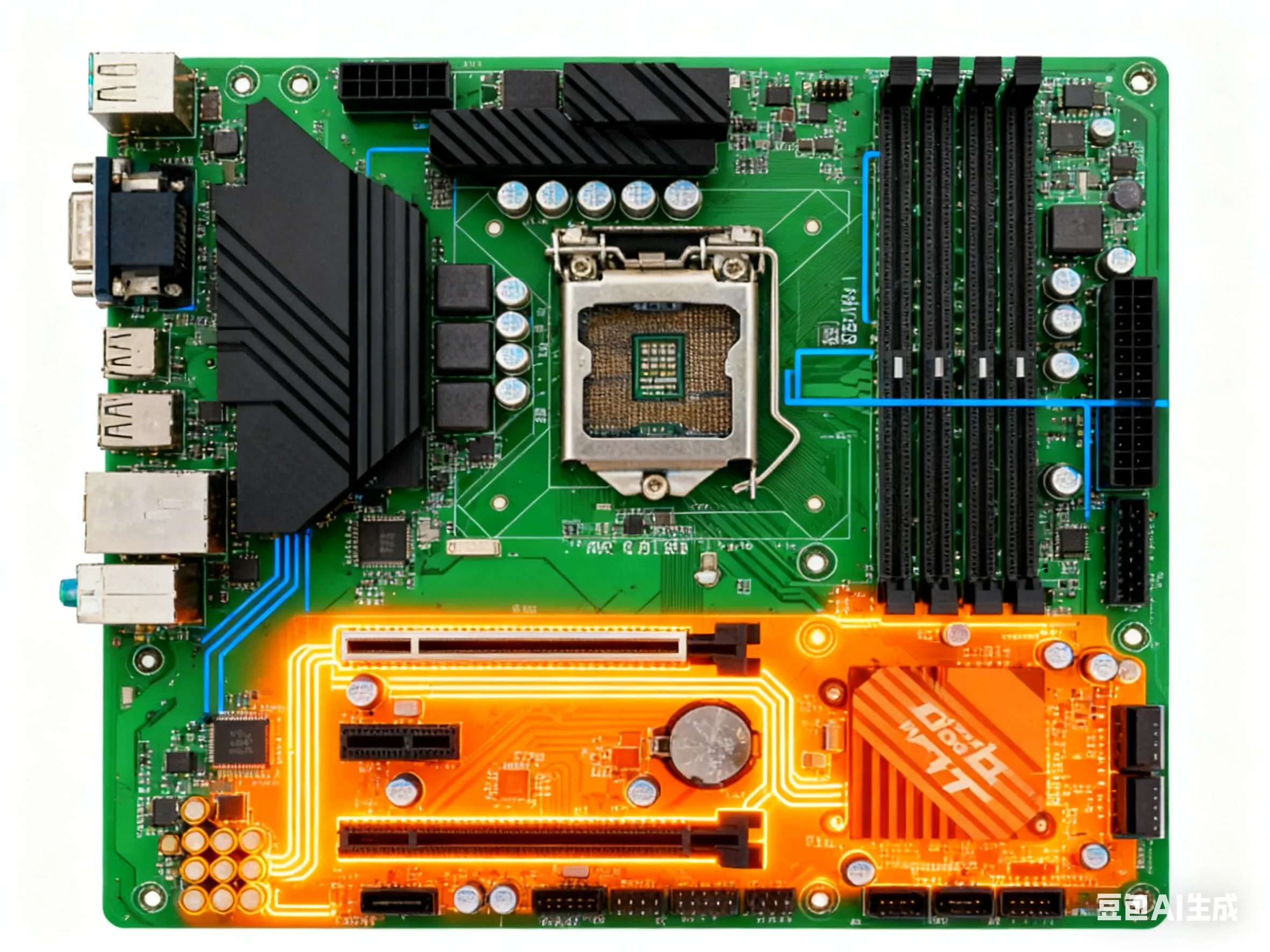

Estratégias de layout de PCB: Combinando modularização e revisão de design

Layout da placa de circuito impresso representa o aspecto artístico do design de PCB, exigindo adesão a princípios como separar tensões altas e baixas e isolar circuitos digitais e analógicos. Primeiro, confirme as posições dos conectores externos, pois eles influenciam o fluxo geral de roteamento. Então, implementar disposição modular: processar cada subunidade (como chips FPGA ou módulos de potência) individualmente antes da colocação de acordo com a direção do fluxo do sinal. Por exemplo, sinais de alta velocidade como PCIe 3.0 deve ser posicionado próximo aos conectores, enquanto as seções de áudio analógico precisam de distanciamento das áreas digitais para reduzir o ruído de acoplamento.

A colocação de componentes geradores de calor também exige atenção. De acordo com a lei do resfriamento de Newton, a eficiência de dissipação de calor está relacionada à área de superfície e ao fluxo de ar, então reserve canais de dissipação térmica durante o layout. Em designs típicos, use a fórmula de resistência térmica do IPC-2221, Rθ = ΔT/P, onde Rθ é a resistência térmica (em °C/W), ΔT é aumento de temperatura, e P é a dissipação de energia. Por exemplo, um chip dissipando 2W com uma resistência térmica de 50°C/W pode sofrer um aumento de temperatura de 100°C, necessitando de vias térmicas ou expansão de folha de cobre.

Após a conclusão do layout, conduzindo um revisão de projeto com engenheiros de hardware para confirmar aspectos críticos é obrigatório. Esta etapa evita retrabalho e melhora as taxas de sucesso na primeira passagem. A prática da indústria provou que o layout modular pode reduzir o tempo de layout da placa, 20% (baseado em IPC dados de referência de design).

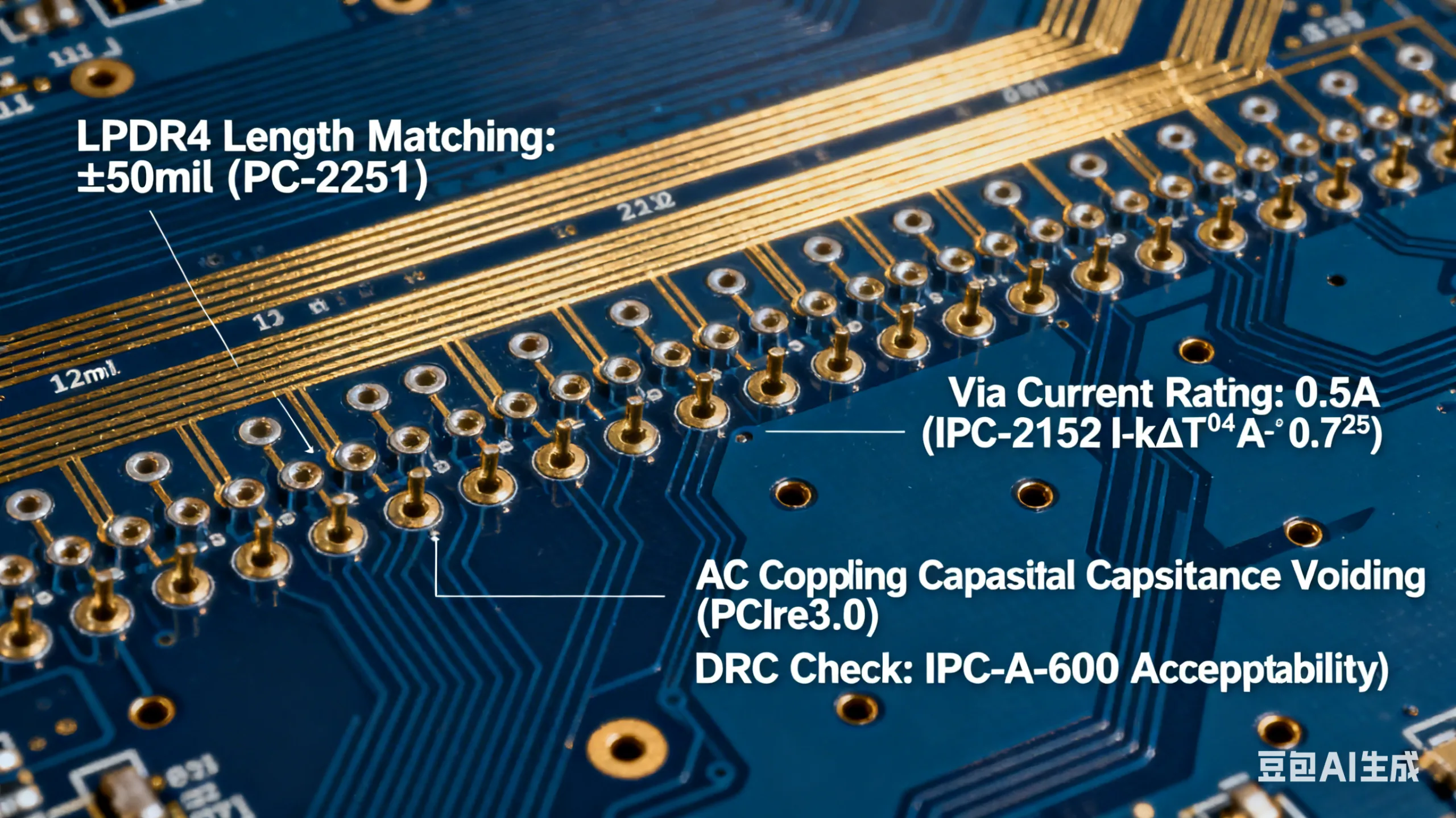

Implementação de roteamento PCB: Da configuração de regras à verificação da RDC

Antes Roteamento de PCB, configurar regras de design é fundamental, abrangendo folgas mínimas, através de tamanhos, e restrições de alta velocidade. Por exemplo, para sinais LPDDR4, definir regras de correspondência de comprimento com desvios controlados dentro de ±50mils (referenciando o padrão IPC-2251). Então, coloque vias antes de rotear: garantir que as vias de todos os módulos estejam organizadas em ordem, considerando a liberação de roteamento e a integridade do cobre. Tipicamente, usar vias 12mil, com cada via transportando aproximadamente 0,5A, baseado na fórmula de transporte de corrente IPC-2152 I = k·ΔT^0,44·A^0,725, onde ΔT é o aumento de temperatura permitido (em °C) e A é a área da seção transversal (em mils circulares). Isso garante que os caminhos de energia não tenham gargalos devido a vias insuficientes.

O princípio de roteamento é “curto, direto, e vias mínimas.” Traços de alta velocidade exigem atenção à integridade do plano de referência e devem incorporar vias de aterramento para reduzir a impedância do caminho de retorno. O manuseio adequado da folga sob os capacitores de acoplamento CA também é crítico; por exemplo, em PCIe 3.0 projetos, a área livre deve se estender abaixo do capacitor para reduzir a capacitância parasita. Depois de concluir o roteamento, RDC (Verificação de regras de design) serve como ponto de verificação final. Use uma lista de verificação abrangente que cubra os critérios de aceitabilidade da norma IPC-A-600, como tamanho mínimo da almofada e cobertura de cobre.

Conclusão: Otimizando o Design para Aumentar o Valor do PCBA

Através desta abordagem sistemática, design de PCB de alta densidade para 8000 As placas PIN podem não apenas atender aos requisitos de desempenho, mas também reduzir os custos de produção. Como um Projeto de PCB especialista, Eu recomendo colaborar com confiáveis Fornecedores de PCB durante os estágios iniciais do projeto para obter cotações personalizadas e otimizar a seleção de materiais e prazos de entrega. Em última análise, o design profissional não apenas acelera o tempo de lançamento no mercado, mas também oferece vantagens competitivas para seus produtos.

Se você precisar de mais Projeto PCB ou PCBA apoiar, por favor entre em contato com fornecedores profissionais de PCB para cotações detalhadas e serviços de consultoria. Compartilhe conhecimento e avance juntos – vamos continuar abrindo novos caminhos no design eletrônico!

LOGOTIPO UGPCB

LOGOTIPO UGPCB