Cada avanço microscópico na tecnologia de embalagens remodela os limites físicos da eletrônica.

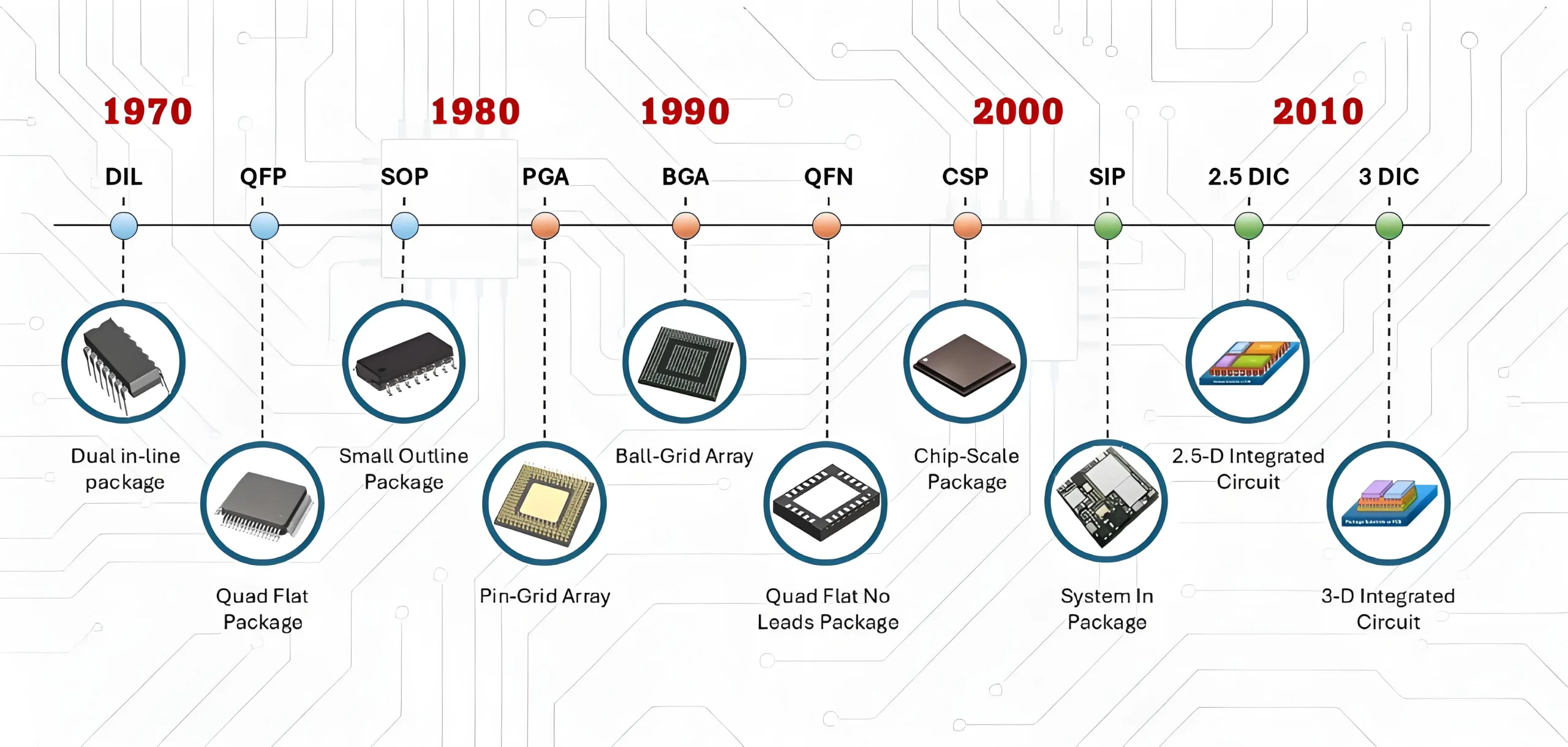

Na semana passada Evolução da embalagem de chips: Do DIP ao X2SON – Como a miniaturização remodelou a eletrônica, exploramos a era das embalagens transparentes (MERGULHAR) e como os dispositivos de montagem em superfície (POP, SOJ, FILHO) iniciou a miniaturização do dispositivo. Embora essas tecnologias tenham estabelecido bases modernas para embalagens, o revolução da miniaturização continua. Hoje, examinamos pacotes de maior densidade – desde quad-flat até CSP de nível wafer – e seu impacto sobre Projeto de PCB limites.

Pacotes Quad-Flat: O equilíbrio espaço-densidade

Pacotes quádruplos (Mf, PLCC/QFJ, QFN) representam uma evolução crítica em direção a maior densidade de E/S, utilizando todas as quatro bordas do pacote.

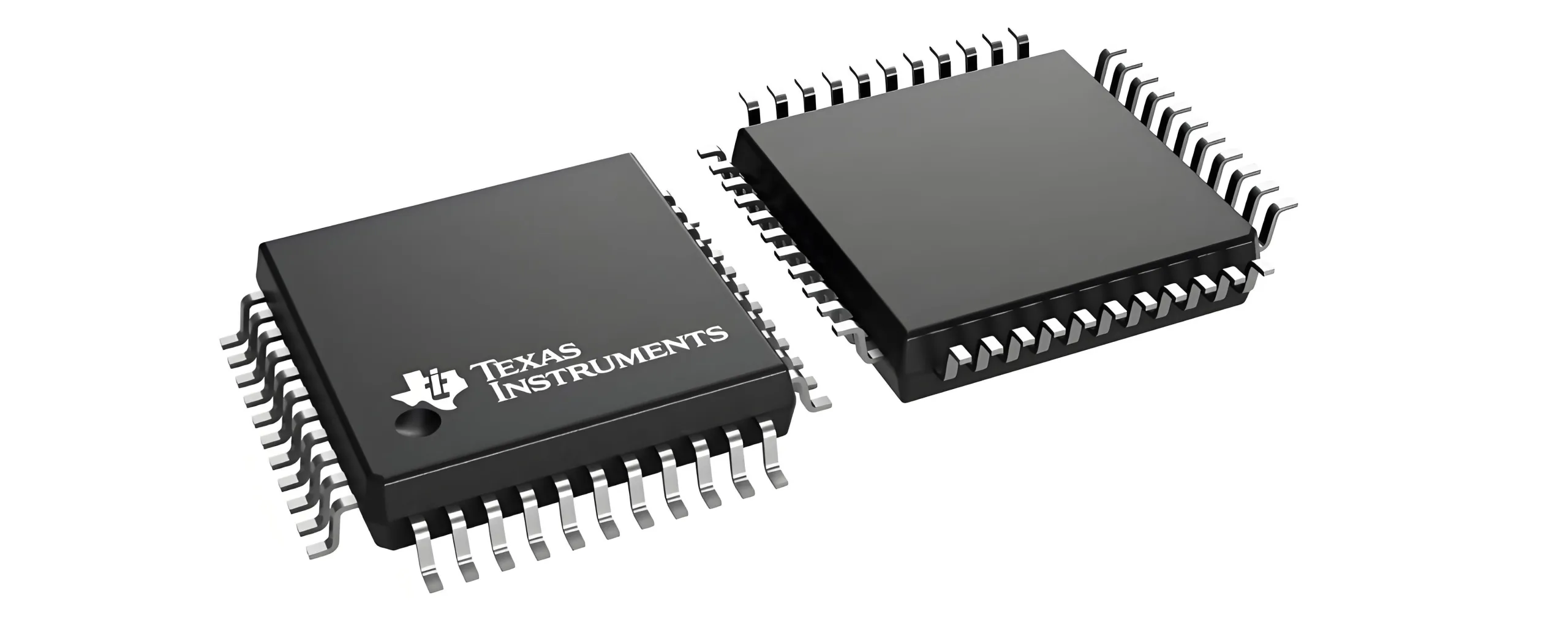

Mf: O pioneiro da densidade de asa de gaivota

Mf (Pacote Quad Flat) características icônicas “asa de gaivota” (Em forma de L) cabos que se estendem de todos os lados. Isso é passo do pino (0.4mm/0,5 mm/0,65 mm) dita Roteamento de PCB densidade e precisão de soldagem.

Variantes QFP:

-

Tamanho/Espessura: LQFP (Discreto), TQFP (Afinar), VQFP (Muito fino)

-

Material: PQFP (Plástico), MQFP (Metal)

-

Térmico aprimorado: HQFP, HLQFP, HTQFP, HVQFP

-

Proteção: BQFP (Amortecedores – as almofadas de canto evitam cabos tortos)

O gerenciamento térmico é crítico. A fórmula de resistência térmica da junção ao ambiente θja = (Tj - Ta)/P (onde Tj=temperatura da junção, Enfrentando=temperatura ambiente, P=poder) rege o projeto de dissipação de calor.

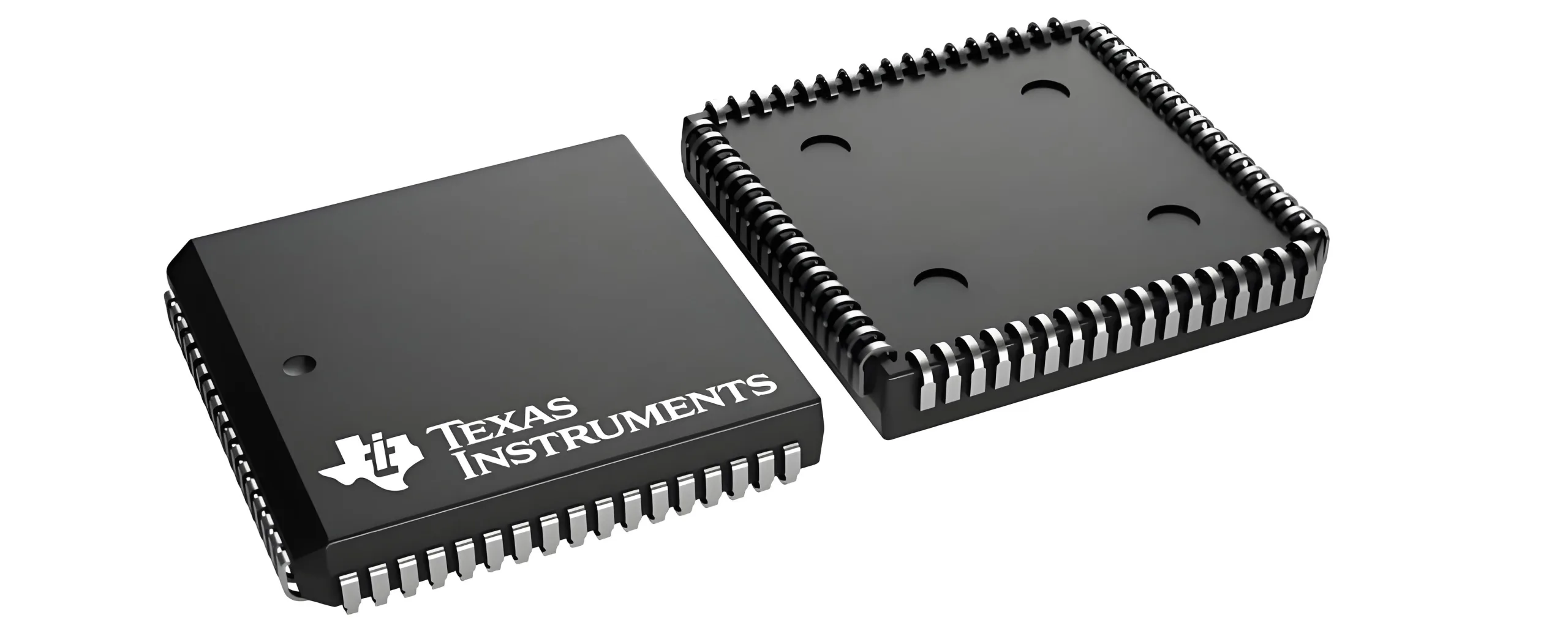

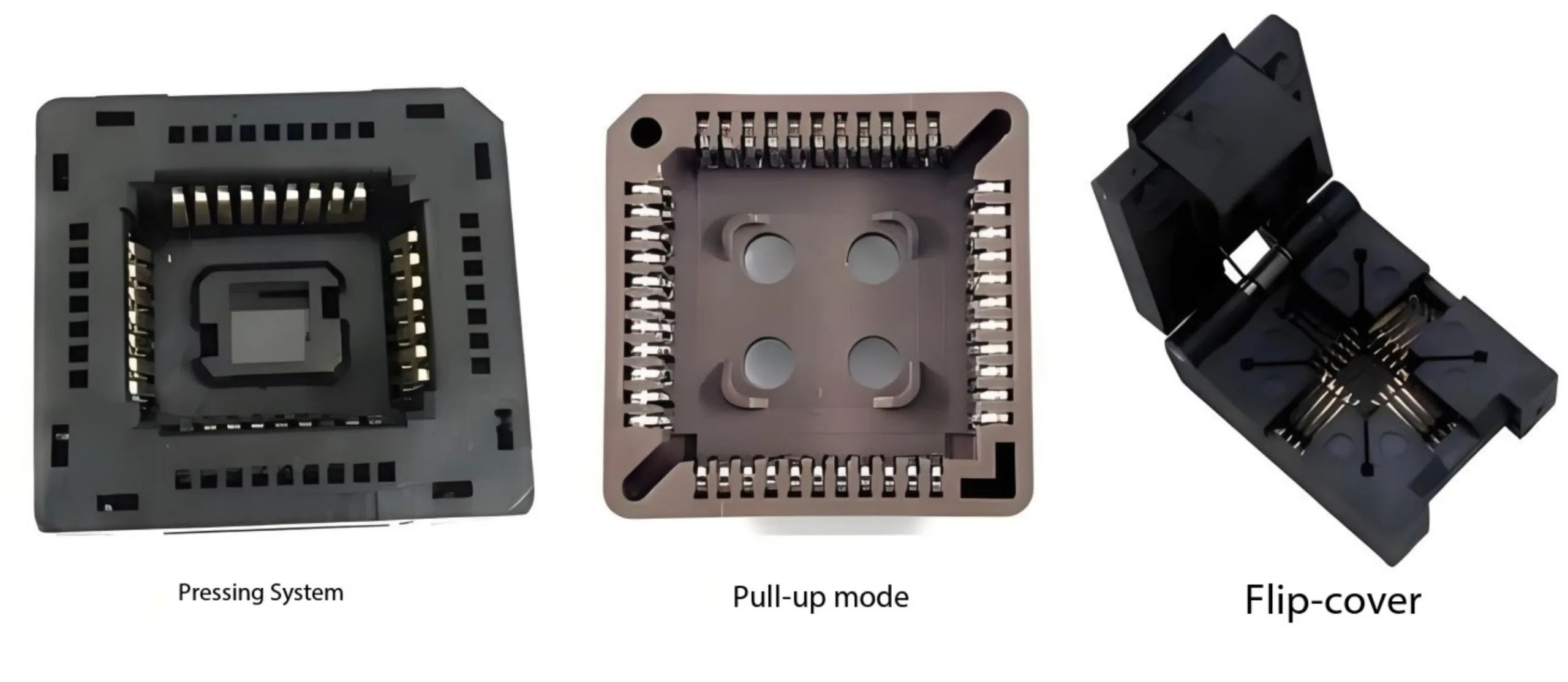

PLCC/QFJ: Estabilidade através de J-Leads

PLCC (Porta-chips com chumbo de plástico) ou QFJ (Quad Flat J com chumbo) usa cabos em forma de J dobrados para baixo para estabilidade mecânica contra vibração/estresse térmico.

Vantagem de padronização: A alta compatibilidade do PLCC/QFJ com soquetes de teste universais agiliza os testes de produção. Embora QFJ seja tecnicamente preciso, “PLCC” continua sendo o preferido do setor.

QFN: Avanço na miniaturização sem chumbo

QFN (Quad Flat sem chumbo) elimina leads externos, conectando via:

-

Almofada exposta (PE): Caminho térmico direto para PCB cobre

-

Flancos Molháveis: Almofadas soldáveis de parede lateral

Principais vantagens:

-

Ultracompacto: 40% menor que QFP

-

Superioridade Elétrica: Caminhos mais curtos reduzem a indutância parasita (L ≈ μ·l/w)

-

Eficiência Térmica: θja inferior vs.. QFP do mesmo tamanho

Evolução da Espessura: LQFN → UQFN → VQFN → WQFN → X1QFN → X2QFN. CCB (LPCC/LCCC) é sua variante de cerâmica/plástico sem chumbo.

Pacotes de matriz: Revolucionando os limites de densidade

Quando quad-flat atinge os limites de E/S, pacotes de matriz (LGA, BGA) ativar densidade de interconexão 2D.

LGA: Conexão elástica de precisão

LGA (Matriz de grade terrestre) usa contatos metálicos precisamente alinhados (por exemplo, LGA775: 775 contatos) combinando com pinos de soquete.

Valor Central:

-

Capacidade de soquete: Atualizações/manutenção de CPU

-

Baixa indutância: Caminhos de sinal curtos

-

Alta confiabilidade: Ideal para CPUs (Intel/AMD)

Limitação: Alto custo/tamanho do soquete favorece o BGA em dispositivos compactos. Observação: LGAs podem ser soldados diretamente por SMT.

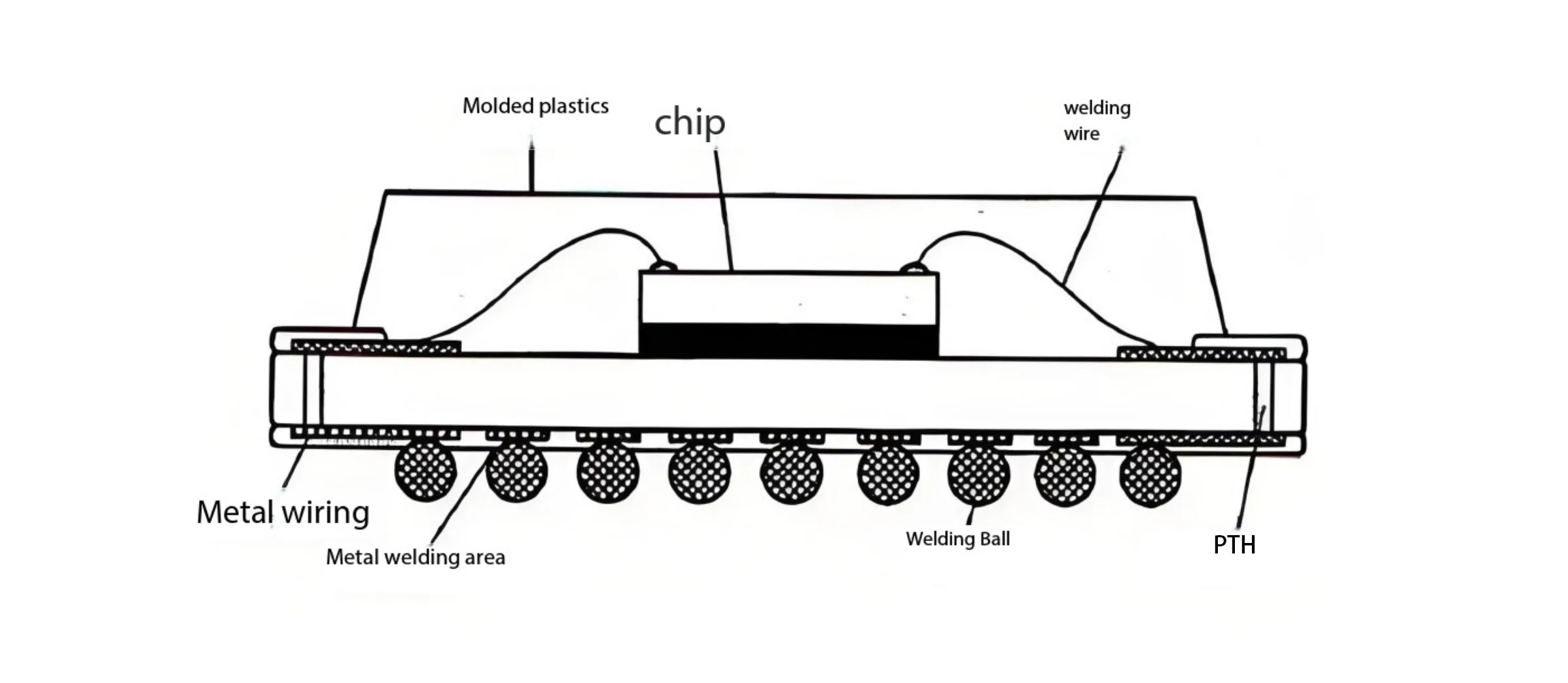

BGA: O domínio da bola de solda

BGA (Array da grade de bola) conecta através de uma matriz de bola de solda. Campo de bola (0.3–1,0 mm; <0.2mm para FBGA) é crítico.

Vantagens Transformativas:

-

Alta densidade: >1,000 Eu/nós (vs.. QFP's ~300)

-

Economia de espaço: 30%+ redução de área vs.. Mf

-

Elétrica/Térmica: Baixo atraso de sinal; bolas conduzem calor

-

Auto-alinhamento: A tensão superficial auxilia na montagem

Família BGA:

-

Material: PBGA (Plástico), CBGA/CABGA (Cerâmica)

-

Tamanho/passo: nFBGA/FBGA (Passo fino), TinyBGA, DSBGA/WCSP (Tamanho da matriz), LFBGA/VFBGA (Afinar)

-

Integração:

-

Fcbga (Flip-Chip): Conexão direta entre matriz e substrato via micro-impactos

-

PoP (Pacote em pacote): Empilhamento vertical (por exemplo, lógica + memória)

-

PG-WF2BGA: Embalagem espalhada em nível de wafer

-

Desafios: Inspeção de raios X (EIXO), retrabalho complexo, Correspondência de CTE Materiais de PCB.

Comparação de pacotes de array

| Recurso | PGA (Matriz de grade de pinos) | LGA (Matriz de grade terrestre) | BGA (Array da grade de bola) |

|---|---|---|---|

| Conexão | Pinos rígidos | Contatos planares | Bolas de solda |

| Força-chave | Confiabilidade do soquete | Densidade + encaixável | Densidade máxima/tamanho mínimo |

| Atraso de sinal | Mais alto | Médio | Mais baixo |

| Aplicações | CPUs legadas/industriais | CPUs de desktop/servidor | Móvel/GPU/SoC |

| Espaço PCB | Grande | Médio | Compactar |

Escala de chip & Pacotes em nível de wafer: Aproximando-se dos limites físicos

Csp: Redefinindo limites de tamanho

Csp (Pacote de escala de chips) métrica principal: Tamanho do pacote ≤ 1,2× tamanho da matriz (vs.. 2–5× para tradicional). BGA essencialmente miniaturizado (FBGA/VFBGA) com tom mais fino (0.2–0,5 mm).

Valor: Miniaturização definitiva para wearables/sensores.

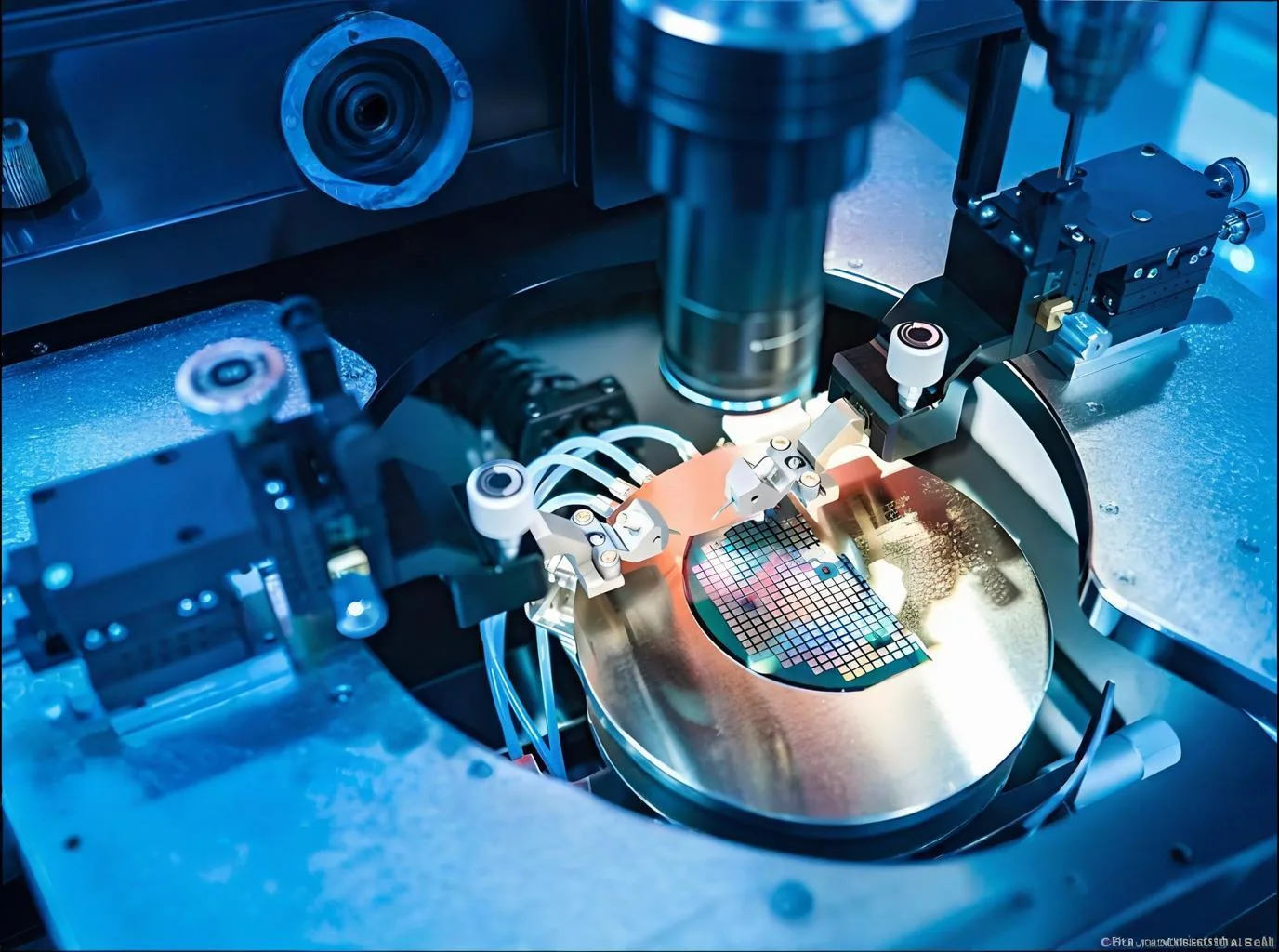

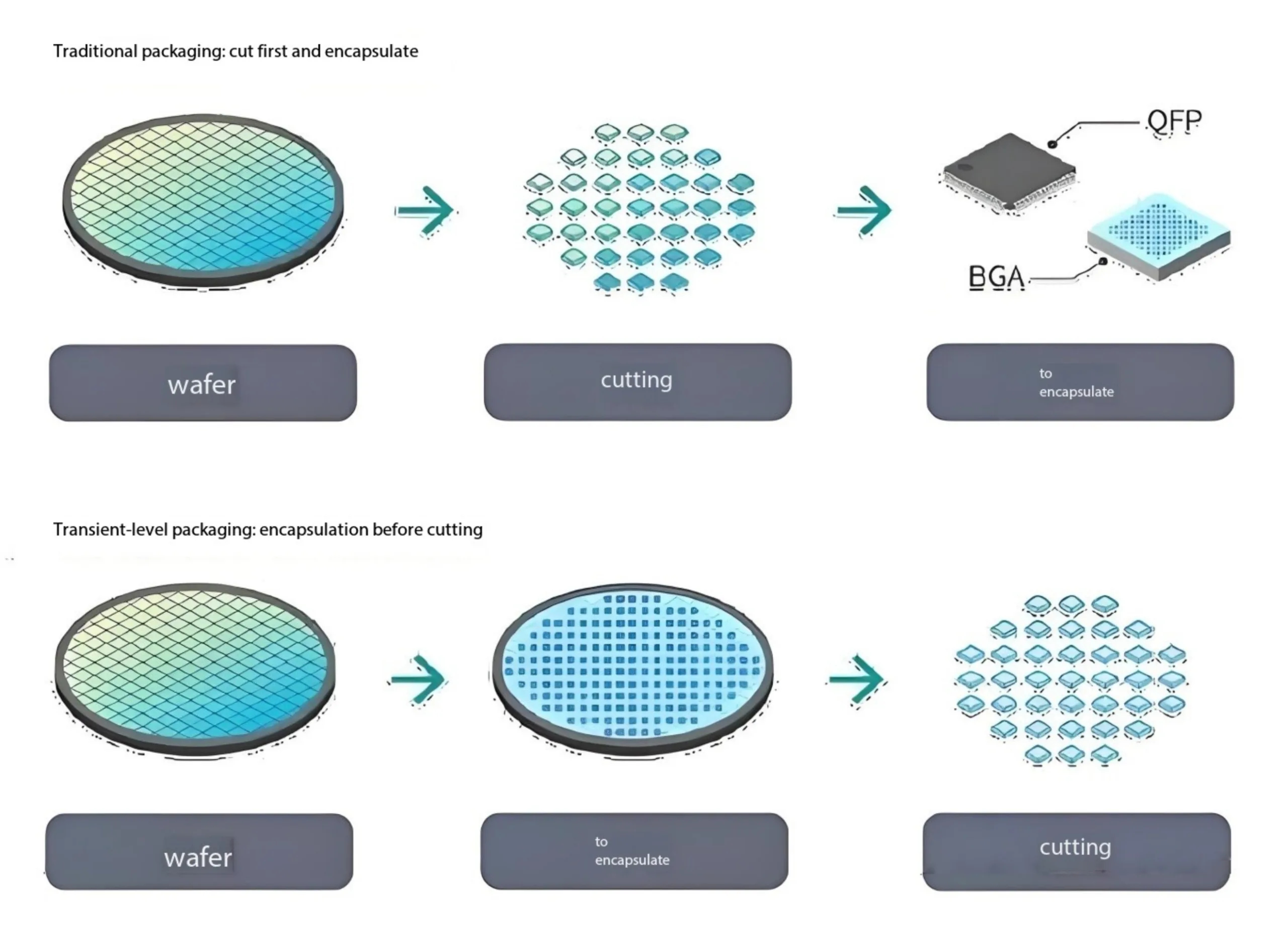

Ulc: A revolução no nível do wafer

A embalagem WLCSP/Wafer-Level conclui todas as etapas (RDL, bola) no wafer antes de cortar.

Vantagens disruptivas:

-

Tamanho Mínimo: ≈ Dimensões da matriz

-

Redução de custos: 30-50% mais barato (sem substratos/moldagem)

-

Desempenho máximo: Interconexões mais curtas, parasitas mais baixos

Tipos WLCSP:

-

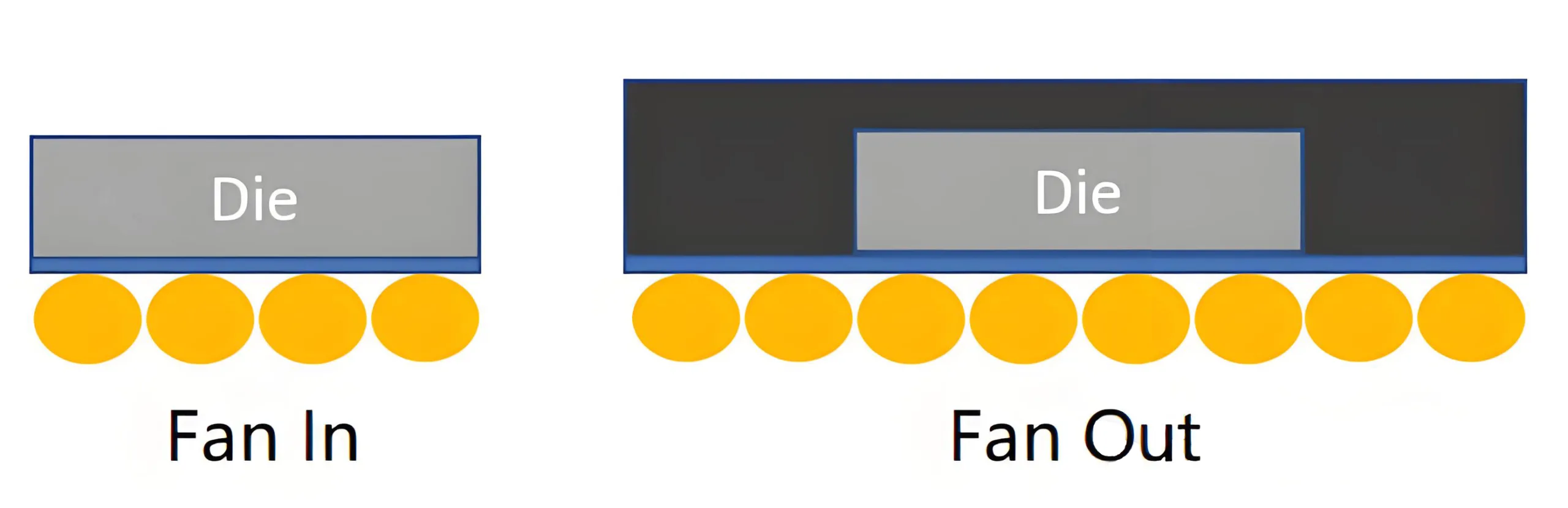

Fan-In WLCSP:

-

Bolas dentro da área do dado

-

Tamanho do pacote = tamanho da matriz

-

Baixo custo para sensores/PMICs

-

-

Fan-Out WLCSP (por exemplo, Informações TSMC, Samsung FO-PLP):

-

As bolas vão além do dado

-

Tamanho do pacote > tamanho da matriz

-

Maior densidade de E/S, integração multichip

-

Para módulos SoCs/RF premium

-

ID visual: Silício não encapsulado (vs.. DFN moldado em resina).

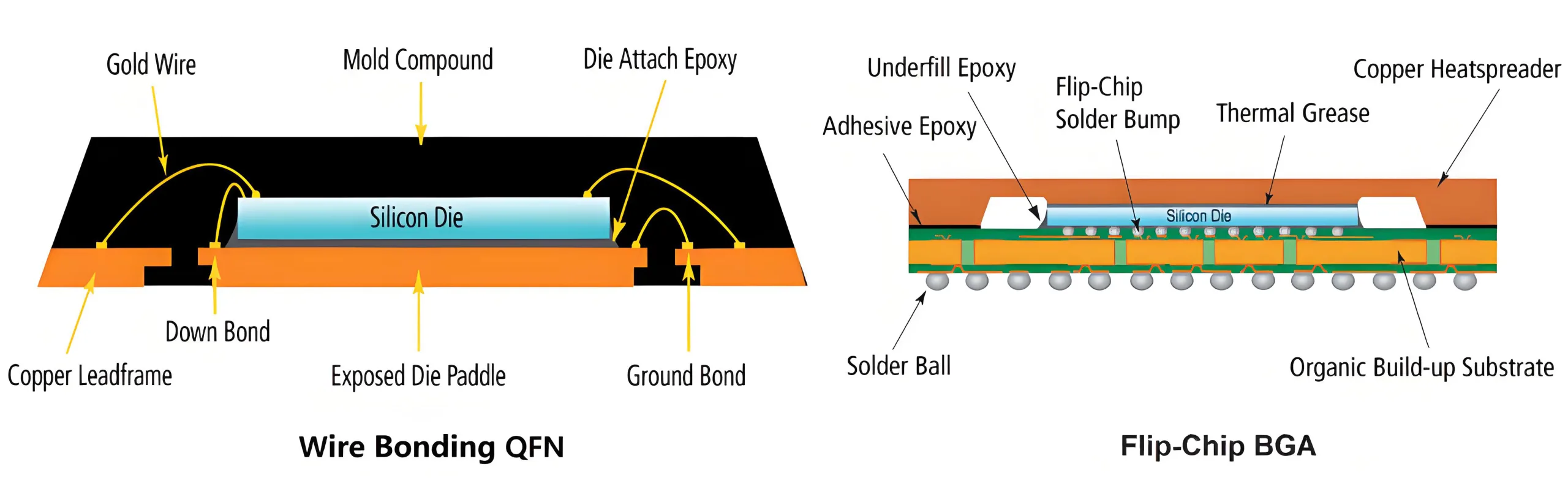

Morfologia da Embalagem & Técnicas de colagem

Formulário de pacote externo (QFP/BGA/WLCSP) e a ligação interna estão intrinsecamente ligadas:

-

Ligação de fio:

-

Maduro, baixo custo

-

Domina QFP/QFN/BGAs de gama média

-

Tem/Com fios; E/S moderada

-

-

Flip-Chip:

-

As matrizes são fixadas voltadas para baixo por meio de microsaliências

-

Interconexões mais curtas, indutância mais baixa

-

Essencial para FCBGA/WLCSP/CSP de alto desempenho

-

Conclusão & Fronteiras Futuras

De QFP para LGA/BGA e finalmente CSP/WLCSP, a evolução das embalagens de chips é uma crônica da compressão do espaço, ganhos de desempenho, e otimização de custos. Cada salto de miniaturização remodela o design do PCB – gerando traços mais precisos, multicamada IDH, e materiais avançados.

Próxima Fronteira: Tecnologias como TSV (Através do Silício Via), Gole (Sistema em pacote), e 2.5D/3D IC agora permitem integração heterogênea 3D, levando o design de PCB a novas dimensões - a serem exploradas em nosso próximo artigo.

Quando um bilhão de transistores cabem em um pacote do tamanho de um grão de areia, Batalhas de engenharia eletrônica em escala molecular.

LOGOTIPO UGPCB

LOGOTIPO UGPCB

Obrigado por compartilhar as informações conosco.

uau, esse blog é magnífico, gosto muito de ler seus artigos. Continue com as boas pinturas! Você reconhece, muitas pessoas estão pesquisando por essas informações, você pode ajudá-los muito.